Система автоматического управления

Иллюстрации

Показать всеИзобретение относится к технике управления подвижными объектами, например судами, работающими в неблагоприятных внешних условиях. Система содержит группу датчиков, блок сбора информации, связанный с аппаратурой спутниковой навигации и снабженный источником импульсного питания, подсистему инерциальной навигации и подсистему оптической коррекции. Входы-выходы блока сбора информации подключены к трем управляющим вычислителям, выходы которых через переключатель каналов вычислителей подключены к исполнительным органам объекта управления. Кроме того, выходы вычислителей и выходы встроенных в их состав средств оперативного контроля подключены к блоку контроля и управления. Выход этого блока подключен к управляющему входу упомянутого переключателя, дополнительный выход которого подключен к управляющему входу формирователя сигналов, связанного с датчиком внешнего воздействия. Система также содержит формирователь синхроимпульсов, входом подключенный к выходу переключателя, а выходами к вычислителям, блоку сбора информации и блоку контроля и управления. Изобретение позволяет повысить надежность и точность системы управления, а также расширить область ее практического использования. 10 з.п. ф-лы, 11 ил.

Реферат

Настоящее техническое решение относится к системам автоматического управления и, в частности, к области судовождения и управления широким классом подвижных объектов, а именно движением объектов как водного транспорта, так и наземного транспорта, а также систем управления авиационными объектами и изделиями ракетно-космической техники, к которым предъявляются повышенные требования по надежности работы в неблагоприятных внешних условиях, к которым относится широкий диапазон температур, внешние электромагнитные излучения, вызванные как работой силового электротехнического оборудования, так и внешние электромагнитные излучения, включая ионизирующие излучения космического пространства как естественного, так и техногенного происхождения, как непрерывного характера, так и импульсного, вызванного вспышками на Солнце или авариями на объектах с атомными энергетическими установками. Известна система автоматического управления судном (См. патент RU 2248914, (В63Н 25/04)) от 01.03.2004, содержащая датчик и задатчик курса, датчик угловой скорости, датчик кормовых рулей, выходы которых подключены к входам первого сумматора-усилителя, выход которого соединен с входом рулевого привода кормовых рулей. Система содержит также датчик угла дрейфа и датчик носовых рулей, выход которого подключен к первому входу второго сумматора-усилителя. Кроме того, в состав системы входят датчик и задатчик бокового смещения судна, задатчик допустимого угла дрейфа и блок логики, содержащий алгебраический сумматор, сумматор модулей двух сигналов, диод и электромагнитное реле с двумя нормально-разомкнутой и нормально-замкнутой контактными группами.

Недостатками данного технического решения являются:

1. Нестабильность характеристик. В связи с применением аналоговых узлов, параметры которых существенно зависят от условий эксплуатации (в первую очередь от температуры окружающей среды), будет наблюдаться дрейф параметров системы в целом.

2. Недостаточная отказоустойчивость. В системе не предусмотрено каких-либо средств нейтрализации отказов отдельных узлов, поэтому выход из строя любого узла приведет к отказу системы в целом. Не предусмотрены также средства восстановления работоспособности после сбоев, вызванных импульсными воздействиями. Кроме того, длительное ионизирующее воздействие приводит к деградации параметров комплектующих полупроводниковых элементов, что изменяет их электрические характеристики и делает систему неработоспособной, несмотря на отсутствие катастрофических отказов.

3. Ограниченные функциональные возможности. Внедрение дополнительных управляющих звеньев или расширение набора датчиков потребует полной переработки аппаратуры системы управления.

4. Фиксированный алгоритм управления. Как в случае расширения, а также реализации другого алгоритма управления, требуется полная переработка аппаратуры.

Задачи расширения функциональных возможностей, применения различных алгоритмов управления и повышения стабильности, благодаря наличию цифрового вычислителя, частично решаются в изобретении - аппаратуре автоматического управления движением судна (См. патент RU 2221728, (В63Н 25/04)) от 13.05.2002). Система содержит кроме вычислителя задатчик путевого угла, датчик угла перекладки руля, рулевой привод, опорную и вспомогательную антенну, приемник системы спутниковой навигации (ССН), сумматор, два интегратора и дифференциатор. Однако недостаток - низкая отказоустойчивость в данной аппаратуре по-прежнему присутствует, так как любой отказ вычислительного устройства влечет за собой отказ всей системы. Не предусмотрены также средства нейтрализации сбоев, вызванных импульсными воздействиями. В то же время катастрофический отказ может быть нейтрализован за счет использования заранее введенных в состав системы резервных компонентов, а параметрический дрейф параметров отдельных узлов может быть нейтрализован перестройкой параметров работы схем электрических, например, изменением быстродействия блоков цифровой обработки или учетом изменения параметров, например, стабильности токов и напряжений аналоговых узлов путем их измерения в процессе работы и последующим учетом их отклонений при обработке данных в вычислительных устройствах. Наиболее полно задача нейтрализации одиночных отказов в вычислительном устройстве, являющимся основным звеном системы, решена в СИСТЕМЕ УПРАВЛЕНИЯ СУДНОМ (См. патент №2424944 от 38.07.2011г.), данное решение может быть взято за прототип. Для нейтрализации последствий одиночных отказов вычислительного устройства и сохранения работоспособности системы управления в целом в состав системы введены три вычислительных устройства с общим устройством синхронизации, обеспечивающим синхронную и синфазную работу вычислителей, выходные сигналы которых прежде, чем поступить на исполнительные органы объекта, проходят через узел мажоритации.

Данное решение обеспечивает нейтрализацию первого отказа в любом из вычислителей. Однако после возникновения первой неисправности в любом из вычислительных устройств надежность дальнейшей работы системы резко снижается, так как возникновение любого второго отказа в любом из двух оставшихся исправными вычислителей приводит к отказу системы в целом, а интенсивность отказов вычислителей, приводящих к потере управления при таком варианте резервирования, в два раза больше, чем при работе с одним оставшимся исправным вычислителем.

Целесообразно после возникновения первого отказа перейти от структуры с мажоритацией к структуре, в которой к выходу подключен один из вычислителей, что требует введения дополнительных средств контроля работы вычислителей и переключения их выходных сигналов. Кроме того, наличие общего устройства синхронизации, отказ в котором приводит к неработоспособности системы, также не способствует требованию высокой надежности системы. В большинстве вычислительных устройств, работающих длительное время в неблагоприятных внешних условиях, а именно расширенном диапазоне температур, потоках ионизирующего излучения как естественного непрерывного фонового, так и импульсного (при вспышках на Солнце или техногенных авариях на объектах с атомными энергоустановками), происходит дрейф параметров элементов, приводящий в цифровых устройствах, как правило, к изменению быстродействия, а в аналоговых узлах - к изменению стабильности и точности их работы. В то же время подстраивая частоту обработки информации в цифровых узлах под их фактическое быстродействие и учитывая дрейф параметров в аналоговых узлах (например, в аналого-цифровых преобразователях) можно сохранить работоспособность и точностные характеристики системы управления. Решение этих задач требует существенной переработки известных решений. С целью повышения надежностных характеристик системы автоматического управления, точности ее работы с целью расширения состава объектов для ее применения предлагается

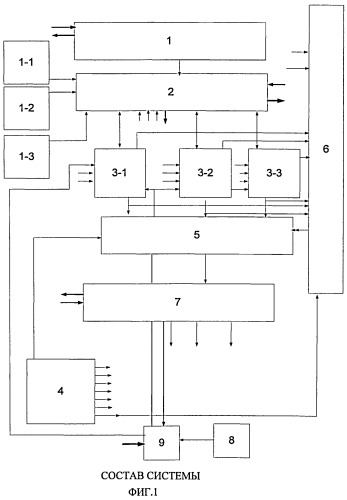

Система автоматического управления, содержащая различные датчики (угловой скорости, ускорения и т.д.), аппаратуру спутниковой навигации (АСН), блок сбора информации (БСИ), три управляющих вычислителя (УВ) с формирователем синхроимпульсов (ФСИ), исполнительные органы (ИО) объекта управления. Кроме того, в состав системы введены подсистема инерциальной навигации (ПИН), подсистема оптической коррекции (ПОК), датчик внешнего воздействия (ДВВ) и формирователь сигналов (ФС) блокировки и обнуления/пуска блоков УВУ.

Состав системы приведен на фигуре 1, где цифрой 1 обозначены датчики, цифрой 1-1 аппаратура спутниковой навигации, цифрой 1-2 - подсистема инерциальной навигации и цифрой 1-3 - подсистема оптической коррекции, цифрой 2 обозначен блок сбора информации (БСИ), цифрами 3-1, 3-2 и 3-3 обозначены управляющие вычислители, (цифрой 4 - формирователь синхроимпульсов), цифрой 5 - переключатель каналов УВ, цифрой 6 - блок контроля и управления (БКУ), цифрой 7 - исполнительные органы (ИО) объекта управления с датчиками обратной связи. Цифрой 8 обозначен датчик внешнего воздействия (ДВВ), а цифрой 9 обозначен формирователь сигналов. Датчики 1 подключены к блоку сбора информации, входы-выходы которого подключены к входам-выходам УВ. Выходы УВ подключены через переключатель каналов к исполнительным органам, а выходы входящих в состав ИО датчиков обратных связей подключены к блоку сбора информации, у которого токовый выход, выделенный на фигуре жирной линией, последовательно подключен к датчикам 1 и датчикам обратной связи, входящих в состав исполнительных органов, после чего возвращается в БСИ. Выходы ФСИ подключены к входам синхронизации УВ, БСИ и БКУ, а управляющий вход ФСИ подключен к выходу переключателя каналов. Тактовые выходы ФСИ подключены к управляющим входам источника импульсного питания.

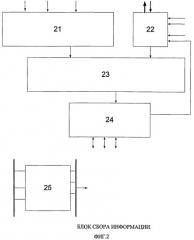

На фигуре 2 приведен состав блока сбора информации. Блок содержит приемные регистры 21, входы которых являются входами блока, преобразователь «аналог-код» 22, токовый вход-выход которого является одноименным входом-выходом блока. Приемные регистры и преобразователь подключены через схемы гальванической развязки 23 к узлу связи 24, вход-выход которого является входом-выходом блока, подключенным к УВ. Управляющий выход узла связи подключен к управляющему входу преобразователя. Цифрой 25 обозначен источник импульсного питания. Три управляющих сигнала на него поступают с выхода формирователя синхроимпульсов, как тактовые сигналы.

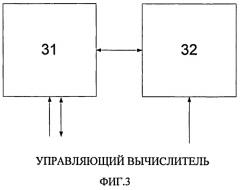

На фигуре 3 приведен управляющий вычислитель, который содержит процессор 31 с подключенным к нему запоминающим устройством 32, двунаправленные входы-выходы процессора являются одноименными входами-выходами вычислителя, а вход обнуления/пуска процессора и вход блокировки запоминающего устройства являются одноименными входами вычислителя, подключенными к формирователю сигналов.

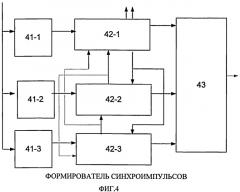

Формирователь синхроимпульсов (См. фигуру 4) содержит три генератора импульсов 41-1, 41-2 и 41-3, управляющий вход которых является одноименным входом формирователя. Каждый генератор подключен к своему блоку формирования 42-1, 42-2 и 42-3, фазирующий выход каждого из которых подключен к фазирующим входам двух других формирователей и является тактовым выходом, поступающим на управление импульсным источником питания в блок сбора информации. Выходы блоков подключены к мажоритарному элементу 43, выход которого является выходом формирователя и блока.

Генератор импульсов (См. фиг.5) содержит n последовательно соединенных инверторов 51, подключенных к мультиплексору 52, выход которого является выходом генератора и подключен к входу первого инвертора и входу счетчика частоты 54. Управляющий вход мультиплексора подключен к выходу счетчика кода частоты 55, инкрементный и декрементный входы которого подключены к одноименным выходам схемы сравнения 56. Первый вход схемы сравнения подключен к выходу счетчика частоты, а второй вход - к выходу регистра кода частоты 57. При этом входы счетчика кода частоты и регистра кода частоты являются управляющим входом генератора.

Блок фазирования (См. фиг.6) содержит элемент И 61, первый вход которого является входом формирователя, подключенным к генератору импульсов. Выход элемента подключен к счетчику 62 и сдвиговому регистру 63. Выходы счетчика подключены к входам первого 64-1 и второго 64-2 дешифратора. Выход первого дешифратора подключен к входу триггера останова 65, выход которого является фазирующим выходом формирователя и подключен к второму входу элемента И и первому входу мажоритарного элемента 68, к второму и третьему входу которого подключены выходы триггеров привязки 67, входы которых являются фазирующими входами формирователя. Их синхровход объединен с первым входом элемента И. Выход второго дешифратора является выходом метки времени и может быть использован УВ для расчета реального времени. Выход является выходом блока и формирователя в целом. Выход мажоритарного элемента подключен к входу триггера пуска 66, выход которого подключен к сбрасывающему входу триггера останова. Выходы нечетных и четных разрядов сдвигового регистра подключены к запускающим и сбрасывающим входам n триггеров формирователей синхроимпульсов (68-1 - 68-n), выходы которых являются синхронизирующими выходами блока и формирователя в целом.

Преобразователь (См. фиг.7) содержит коммутатор 71, информационные входы которого являются входами преобразователя, а выход подключен к преобразователю напряжения в частоту 72, выход которого подключен к блоку связи 73, входы-выходы которого являются входами-выходами преобразователя. Кроме того, преобразователь содержит источник тока 74, выход которого через последовательно включенный эталонный резистор RЭТ поступает на вход для включения внешних резисторных датчиков, а токовый вход источника является входом преобразователя для шины, приходящей от внешних резисторных датчиков. Управляющий выход блока связи подключен к управляющему входу коммутатора, а его входы являются входами преобразователя, подключенными к внешним датчикам.

На фигурах 8-1 и 8-2 приведены соответственно датчики внешних ионизирующего и электромагнитных воздействий, реализованные на основе блокинг-генератора с тем отличием, что в датчике ионизирующего воздействия к базе транзистора подключен обратносмещенный диод, а в датчике электромагнитного воздействия к базе подключен резонансный контур (антенна). На фигуре 9 приведен формирователь сигналов. Формирователь содержит кварцевый задающий генератор 91, выход которого подключен к первому входу первого элемента И 92, к второму входу которого подключен выход первого триггера 93. Выход этого элемента И подключен к входу счетчика тактов 94, реализованного на динамических триггерах. Выходы счетчика подключены к входам первого счетного 95-1 и второго счетного 95-2 дешифраторов. Выход первого дешифратора является выходом обнуления пуска формирователя. Выход второго дешифратора подключен к первому входу второго триггера 96, выход которого подключен к первому входу второго элемента И, выход которого является блокирующим выходом формирователя, а его запрещающий вход подключен к выходу дешифратора кода 98, входы которого подключены к выходам регистра управления 97, вход которого является управляющим входом формирователя, у которого вход от датчика подключен к второму входу второго элемента И 99 и входам первого и второго триггеров.

Динамический триггер (См. фиг.10) реализован на основе транзисторного усилителя, к базе которого помимо резисторного делителя, задающего рабочий режим, подключена LC цепь, являющаяся фактически элементом памяти, состояние которой передается на выход усилителя в моменты подачи на него импульсного напряжения питания, что сводит к минимуму вероятность искажения состояния.

На фигуре 11 приведена схема источника импульсного питания динамических триггеров. Источник содержит три параллельных цепи, предающих напряжение силовой шины на выход, в каждой цепи последовательно включены два полевых транзистора, три сигнала управления которыми разведены таким образом, что каждый сигнал поступает на два транзистора, установленные в разных цепях. На схеме сигналы управления обозначены соответственно одним, двумя и тремя штрихами.

Система работает следующим образом:

После включения питания начинают работать генераторы импульсов ФСИ и через несколько периодов высокой частоты с выхода ФСИ в УВ и остальные блоки системы начинают поступать синхронно и синфазно синхроимпульсы УВ приступают к выполнению программ управления, опрашивая через блок сбора информации внешние датчики и корректирующие подсистемы АСН, ПИН и ПОК.

Результаты вычислений выдаются через переключатель каналов на исполнительные органы объекта управления, выходная информация всех каналов УВ поступает одновременно в блок контроля и управления переключателем, в который, кроме того, поступают сигналы неисправности, вырабатываемые встроенными в каждый УВ аппаратурными средствами, например по mod3. Можно обозначить сигналы от этих средств через Нi, где i - номер УВ (1, 2 или 3). Для логики работы переключателя все УВ расположены по кольцу: 1, 2, 3, 1. Таким образом для УВ3 (i) УВ2 будет иметь индекс i-1, а УВ 1 будет иметь индекс i+1 и т.д. При обнаружении неисправности i-го УВ переключатель подключает к выходу сигналы предыдущего по номеру, т.е. i-1 вычислителя. В случае неисправности двух вычислителей к выходу подключены сигналы третьего исправного. Таким образом, после возникновения первого отказа к выходу подключены сигналы всегда одного вычислителя, что существенно снижает вероятность отказа системы после возникновения первой неисправности. В случае формирования сигналов неисправности трех вычислителей, что может быть следствием ограниченной достоверности работы встроенных средств контроля или схем сравнения к выходу остается подключенным последний признанный исправным вычислитель, что исключает неопределенность в логике работы переключателя. Логику выработки сигналов неисправности УВ, вырабатываемых БКУ, по которым происходит переключение каналов, можно представить в виде логической формулы.

Обозначим:

Hi - неисправность i-го УВ, нi - неисправность этого же вычислителя, сформированную внутренними средствами контроля,

Ci - неисправность этого же вычислителя, сформированную схемами сравнения.

Тогда Hi=Ci∨нi

Логику выработки сигнала неисправности, формируемого схемами сравнения, можно записать следующим образом:

Ci=(Иi∧Иi-1∧JИi-1∨Иi∧Иi-1∧Иi+1)∨(JИi∧JИi+1∧Иi-1

∨Иi∧JИi+1∧Иi-1∨JИi∧JИi-1∧Иi+1).

При срабатывании датчика внешнего воздействия на УВ из ФС поступает сигнал обнуления/пуска, после снятия которого процессора УВ переходят на программу восстановления, используя сохраненные в их запоминающих устройствах рестартовые массивы данных. В связи с тем, что запоминающие устройства были постоянно заблокированы от несанкционированного обращения, для работы с ними производится запись кода разблокировки, регистр 97 формирователя сигналов, который снимает на время существования кода в регистре сигнал блокировки и позволяет работать процессору с запоминающим устройством. После чтения массивов код разблокировки стирается и запоминающее устройство оказывается снова заблокировано. По мере формирования рестартовых массивов для их записи в запоминающее устройство также проводится запись кода разблокировки в регистр 97, который затирается после окончания такой записи, и запоминающее устройство вновь переводится в заблокированное состояние, исключающее искажение рестартовых массивов до нового срабатывания датчика.

Таким образом, введение переключателя с блоком контроля и управления позволяет нейтрализовать, по крайней мере, две неисправности в вычислителях и сохраняет вероятность работоспособности системы при трех неисправностях УВ. Наличие в ФСИ трех генераторов импульсов и трех взаимно фазируемых блоков фазирования и схем мажоритации на выходе обеспечивает нейтрализацию как одной постоянной неисправности в ФСИ, так и нейтрализацию кратковременных отказов (сбоев) в формирователе, в которых реализована функция взаимного фазирования на 2-3 периода высокой частоты. После чего начинается формирование синхронных и синфазных меток реального времени и синхроимпульсов, обеспечивающих работу УВ и системы в целом. Введение перестройки частоты генераторов импульсов позволяет на каждый интервал времени установить частоту синхронизации, соответствующую текущему быстродействию цифровых узлов, что позволяет не только повысить надежность работы системы при снижении быстродействия элементов, но и использовать возникающие запасы по быстродействию, для чего предусмотрено периодическое выполнение программ тестовых проверок УВ, позволяющее оценить работоспособность при текущей или устанавливаемой частоте синхронизации. Введение режима санкционирования доступа к запоминающему устройству обеспечивает восстановление вычислительного процесса путем повторения расчетов сбойного цикла решения с использованием массивов данных, сохраненных в запоминающем устройстве УВ. Для повышения надежности рестартовый массив дублируется и каждый из двух массивов охватывается контрольной суммой. По результатам проверки сохранности массивов по контрольным суммам выбирается рабочий массив, который используется для восстановления. Для нейтрализации параметрических уходов аналоговых узлов в блоке сбора информации в качестве основного выбран преобразователь напряжения в частоту, обладающий тем несомненным преимуществом, что зависимость точности и стабильности его работы определяется всего двумя элементами - резистором и конденсатором, выбором типов которых и предварительной их термотренировкой и радиационной обработкой с последующим «отжигом» можно обеспечить требуемую стабильность на продолжительном интервале времени. Нестабильность работы источника тока, необходимого для запитки внешних датчиков резистивного типа в предложенной системе, нейтрализуется установкой в токовую цепь высокостабильного эталонного резистора, замеряя падение напряжения, на котором определяют текущее значение тока опроса датчиков и проводят необходимый перерасчет результатов замеров. Совокупность предложенных решений в виде дополнительных блоков, организации перестройки структуры при возникновении отказов, а также нейтрализации параметрических уходов параметров, как цифровых узлов, так и аналоговых позволяет существенно повысить надежность и точность работы системы управления, работающей длительное время в условиях воздействия внешних дестабилизирующих факторов, что существенно расширяет по сравнению с известными решениями диапазон применения системы для объектов различного назначения.

1. Система управления подвижными объектами, содержащая три управляющих вычислителя с подключенными к ним через блок сбора информации датчиками углов, угловой скорости, ускорения, обратной связи исполнительных органов, аппаратурой спутниковой навигации, подсистемой инерциальной навигации, подсистемой оптической коррекции, формирователь синхроимпульсов, отличающаяся тем, что в ее состав введены переключатель каналов вычислителей, подключенный входами к вычислителям, а выходом - к исполнительным органам с датчиками обратной связи и формирователю синхроимпульсов, блок контроля и управления, подключенный входами к выходам вычислителей и их контрольных устройств, выходами - к управляющему входу переключателя, причем выходы датчиков углов, ускорения и обратной связи подключены к входам блока сбора информации, токовая шина которого последовательно проходит через информационные датчики и датчики обратной связи исполнительных органов, а входы-выходы блока подключены к вычислителям.

2. Система по п.1, отличающаяся тем, что блок сбора информации содержит буферные регистры и преобразователь информации, входы которых являются входами блока, а выходы через элементы гальванической развязки подключены к углу связи, входы-выходы которого являются входами-выходами блока, а управляющий выход подключен к управляющему входу преобразователя, токовая шина которого подключена последовательно к информационным датчикам и датчикам обратной связи, после которых возвращается на вход блока, кроме того, блок содержит источник импульсного питания, вход которого подключен к силовой шине, три управляющих входа являются входами, подключенными к выходам формирователя синхроимпульсов, а вторая сторона источника является выходом импульсного питания.

3. Система по п.1, отличающаяся тем, что управляющий вычислитель содержит процессор с подключенным к нему запоминающим устройством, причем входы-выходы процессора, его вход обнуления/пуска и блокирующий вход запоминающего устройства являются одноименными входами-выходами и входами вычислителя.

4. Система по п.1, отличающаяся тем, что формирователь синхроимпульсов содержит три генератора импульсов, управляющие входы которых являются входом формирователя, а выход каждого из которых подключен к своему блоку фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и является тактовым выходом блока и формирователя, а выходы блоков подключены к мажоритарному элементу, выходы которого являются выходами формирователя.

5. Система по п.4, отличающаяся тем, что генератор импульсов содержит n последовательно соединенных инверторов, выходы которых подключены к входам мультиплексора, выход которого является выходом генератора и подключен к входам первого инвертора и счетчика частоты, выход которого подключен к первому входу схемы сравнения, к второму входу которой подключен выход регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам счетчика кода частоты, вход которого и вход регистра кода частоты являются управляющим входом генератора.

6. Система по п.4, отличающаяся тем, что блок фазирования содержит элемент И, первый вход которого является входом формирователя, а выход подключен к сдвиговому регистру и счетчику, выходы которого подключены к первому и второму дешифраторам, причем выход первого дешифратора является выходом блока, а выход второго дешифратора подключен к запускающему входу триггера останова, выход которого является фазирующим выходом формирователя и подключен к второму входу элемента И и первому входу мажоритарного элемента, к второму и третьему входам которого подключены выходы триггеров привязки, входы которых являются фазирующими входами формирователя, а их синхронизирующий вход объединен с первым входом элемента И, а нечетные и четные выходы сдвигового регистра подключены к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются синхронизирующими выходами блока.

7. Система по п.2, отличающаяся тем, что преобразователь информации содержит коммутатор, входы которого являются входами преобразователя, а выход подключен к преобразователю напряжения в частоту, выход которого подключен к узлу связи, входы-выходы которого являются входами-выходами преобразователя, а управляющий выход подключен к управляющему входу коммутатора, к дополнительным входам которого подключены выводы эталонного резистора, включенного в шину источника тока, которая выводится на выход и после прохождения внешних датчиков возвращается в источник тока.

8. Система по п.1, отличающаяся тем, что датчик внешнего воздействия реализован на основе блокинг-генератора, к базе транзистора которого у датчика ионизирующего воздействия подключен обратно смещенный диод, а у датчика электромагнитного воздействия - резонансный контур.

9. Система по п.1, отличающаяся тем, что формирователь сигналов содержит кварцевый задающий генератор, подключенный выходом к первому входу первого элемента И, выход которого подключен к входу динамического счетчика, выходы которого подключены к первому и второму счетным дешифраторам, причем выход первого дешифратора является выходом обнуления/пуска формирователя, а выход второго дешифратора подключен к первому входу второго триггера, выход которого подключен к первому входу второго элемента И, выход которого является блокирующим выходом формирователя, управляющий вход которого является входом регистра управления, выход которого через дешифратор кода подключен к запрещающему входу второго элемента И, второй вход которого является датчиковым входом формирователя и объединен с вторым входом второго триггера и входом первого триггера, выход которого подключен к второму входу первого элемента И.

10. Система по п.9, отличающаяся тем, что динамический триггер реализован как транзисторный усилитель, к базе которого помимо задающего режим резисторного делителя подключена LC цепь в качестве элемента памяти.

11. Система по п.2, отличающаяся тем, что источник импульсного питания содержит три параллельных цепи, в каждой из которых последовательно включены между силовой шиной и выходной два полевых транзистора, причем три управляющих тактовых сигнала подключены к затворам транзисторов таким образом, что каждый сигнал поступает на затворы двух транзисторов, находящихся в разных цепях, образуя таким образом на транзисторах выборку «2 из 3».