Модульная система цифровой обработки для полезных нагрузок спутников связи

Иллюстрации

Показать всеИзобретение относится к области радиотехники, а именно к системе цифровой обработки для полезных нагрузок спутников связи, и может быть использовано в системах спутниковой связи с множеством направленных лучей. Технический результат заключается в осуществлении модульного подхода к конструкции и воплощению интегрированного процессора для систем спутниковой связи с множеством направленных лучей таким образом, что общий интегрированный процессор содержит большое количество идентичных интегрированных модулей процессора, а также в обеспечении поддержки требований к системе и трафику в широком диапазоне задач. Для этого количество модулей интегрированного процессора выбрано в соответствии с характеристиками антенны и ширины полосы восходящей линии и нисходящей линии определенной миссии, в связи с характеристиками модуля интегрированного процессора, и каждый модуль интегрированного процессора содержит каскад цифровой обработки, содержащий множество входных и выходных портов, A/D и D/A преобразователи и средство цифровой обработки. 1 з.п. ф-лы, 5 ил.

Реферат

1. Уровень техники

В системах спутниковой связи все более часто используются системы с множеством сфокусированных лучей, которые обеспечивают преимущества по усилению антенны, что снижает потребление энергии и способствует возможности работы с малогабаритными наземными терминалами, а также их возможности поддержки пространственного повторного использования частоты и, следовательно, повышения пропускной способности в системе с ограничением по ширине полосы. В связи с использованием систем с множеством сфокусированных лучей, необходимо обеспечить гибкость в маршрутизации из канала в луч, чтобы обеспечивать возможность изменения распределения трафика между лучами и обеспечения гибкости при отображении частот между восходящей линией и нисходящей линией, чтобы соответствовать ограничениям планирования частот. Учитывая множество существующих систем, в которых используется более чем одна сотня лучей, необходимо использовать сложные технологии цифровой обработки в основном канале данных полезной нагрузки для обеспечения требуемой гибкости. Цифровые процессоры, используемые в таких спутниковых системах с множеством направленных лучей, называются "прозрачными", в связи с тем, что сигналы канала данных дискретизируются в цифровой форме и обрабатываются, но не демодулируются в полезной нагрузке.

Системы, в которых в настоящее время используется прозрачная цифровая обработка, обычно относятся к категориям архитектуры систем прямой линии связи, обратной линии связи или ячеистой линии связи. В архитектурах прямой линии связи трафик передают в форме восходящей линии из одного или небольшого количества шлюзов в пределах одного или небольшого количества лучей к нисходящей линии к большому количеству пользовательских терминалов в пределах зоны охвата множества направленных лучей. В таких системах требуется обеспечить гибкость при маршрутизации данного канала восходящей линии шлюза в любой из лучей нисходящей линии и гибкость при отображении заданного канала восходящей линии в любой из доступных интервалов частот в пределах лучей нисходящей линии.

В архитектурах обратной линии связи трафик переносится в восходящей линии от большого количества пользовательских терминалов в пределах зоны охвата множества направленных лучей в нисходящую линию к одному или небольшому количеству терминалов шлюза, расположенных в пределах одного или небольшого количества лучей. Здесь существует требование обеспечения гибкости при маршрутизации каналов в любом частотном интервале в любом из восходящих лучей пользователя в любой доступный интервал в пределах луча или лучей нисходящей линии шлюза. Ячеистая архитектура отличается большим количеством направленных лучей, как в восходящей, так и в нисходящей линии, и при этом установлено требование обеспечения гибкости при маршрутизации из луча в луч, и отображении частот между восходящей и нисходящей линией для любого канала восходящей передачи данных.

Архитектуры цифрового процессора, используемые в настоящее время в системах с множеством направленных лучей, можно разделить на архитектуры с пространственным переключением или архитектуры с цифровым формированием луча. В архитектуре с пространственным переключением для сигналов восходящей линии из одного или множества лучей, выполняют цифровую выборку, используя аналогово-цифровые (А/D) преобразователи, и после этого их подвергают цифровому частотному демультиплексированию для изоляции отдельных каналов. Система переключения, работающая в отдельных каналах, обеспечивает гибкую маршрутизацию каждого канала восходящей линии в требуемый интервал частот в пределах требуемого луча нисходящей линии. Каналы, направленные в заданный луч нисходящей линии, частотно мультиплексируют и подвергают цифро-аналоговому (D/А) преобразованию для формирования требуемого аналогового сигнала луча. Такой подход можно применять для прямой, обратной или ячеистой архитектур, где интерфейсы антенной системы принимают форму портов лучей, например, используя антенну типа с одиночным возбуждением каждого луча (SFPB).

В архитектурах цифрового формирования луча обработка может использоваться в пределах архитектур полезной нагрузки, в которых используется множество фидеров или элементов в пределах антенны для синтеза заданного направленного луча, и, в частности, пригодной для антенны типа фазированной антенной решетки и антенны типа отражателя с облучателем в виде антенной решетки (AFR). Сложные взвешивающие функции в диаграммообразующей схеме для каждого канала используют для управления свойствами луча для этого канала. Например, весовые коэффициенты канала могут быть выбраны для определения направления заданного направленного луча в соответствии с распределением трафика наземного терминала, или управление размером и формой луча можно использовать для предоставления дополнительной гибкости. Цифровое формирование луча может применяться для линий связи с множеством направленных лучей, как для прямой, так и для обратной или ячеистой архитектур системы.

С центральным цифровым процессором ассоциированы, как соединенные через A/D и D/А преобразователи, аналоговые функции предварительной и последующей обработки, которые выполняют предварительную обработку сигналов, подаваемых в A/D преобразователи и выводимых из D/А преобразователей. Комбинация функций центральной цифровой обработки и функций аналоговой предварительной и последующей обработки составляет общий интегрированный процессор.

В настоящее время системы обработки, используемые в спутниковых системах, представляют собой специально разработанные системы в соответствии с требованиями конкретной задачи. Это обычно предполагает чрезвычайно сложное воплощение в форме одиночного модуля, размеры которого выбирают в соответствии с требованиями задачи, и для которого требуется модульная конструкция с множеством модулей более низкого уровня, большое количество разъемов высокой плотности и сложные объединительные платы. На разработку и испытания этих систем требуется много времени, что приводит к удлинению общего плана и повышению затрат. Высокие требования к локализованной массе и потреблению энергии могут сделать трудным размещение такой полезной нагрузки, что часто требует изощренного управления отбором тепла. Такой подход к проектированию в виде одиночного модуля имеет ограниченные возможности использования в других задачах, которые отличаются по размеру или масштабу.

Цель настоящего изобретения состоит в том, чтобы предложить модульный подход к конструкции и воплощению интегрированного процессора для систем спутниковой связи с множеством направленных лучей таким образом, что общий интегрированный процессор содержит большое количество идентичных интегрированных модулей процессора. Интегрированный модуль процессора может содержать большое количество физически интегрированных компонентов или множество дискретных компонентов.

Дополнительная цель настоящего изобретения состоит в том, чтобы обеспечить обобщенный модуль цифрового процессора, который можно использовать на поддержки требований к системе и трафику в широком диапазоне задач, отличающихся по типу и масштабу. Обобщенный цифровой модуль обеспечивает либо пространственное переключение, либо функцию цифрового формирования луча, как варианты выбора в пределах общей модульной конструкции. Хотя концепция центральной цифровой обработки является обобщенной, ожидается, что подробные параметры функций предварительной обработки и последующей обработки будут специфичными для задачи, например, в соответствии с частотами и полосами линий связи.

2. Сущность изобретения

Из первого аспекта следует, что настоящее изобретение относится к системе обработки полезной нагрузки спутника связи, содержащей один или более идентичных общих модулей интегрированного процессора, в которой количество модулей выбирается в соответствии с характеристиками антенны и ширины полосы восходящей линии и нисходящей линии конкретной задачи, в связи с характеристиками модуля интегрированного процессора.

В предпочтительном варианте воплощения каждый модуль интегрированного процессора содержит каскад предварительной обработки, причем каскад цифрового процессора содержит: множество входных портов, выполненных с возможностью приема сигналов, соответствующих восходящей линии, причем каждый входной порт имеет заданную ширину полосы; и множество выходных портов, выполненных с возможностью вывода сигналов, соответствующих нисходящей линии, причем каждый выходной порт имеет заданную ширину полосы; и каскад последующей обработки; и причем количество отдельных интегрированных модулей интегрированного процессора в системе обработки полезной нагрузки спутника связи является функцией портов антенны восходящей и нисходящей линии и соответствующей ширины полосы восходящей и нисходящей линии в отношении множества входных (N) и выходных (M) портов и соответствующей ширины полосы входного и выходного портов каскада цифрового процессора. Один или больше из входных портов и/или выходных портов могут обеспечивать избыточность.

Следовательно, размер общего процессора определяют путем использования множества идентичных модулей интегрированного процессора в соответствии с требованиями к системе более высокого уровня и параметрами, в соответствии с определенной шириной полосы системы, количеством портов лучей в пространственной архитектуре переключения или количеством портов фидеров/элементов в архитектуре цифрового формирования луча. В предельном случае отдельный модуль интегрированного процессора можно использовать для малой миссии или комбинированной миссии, в то время, как относительно большое количество модулей (например, 6 или больше), можно использовать для поддержки широкомасштабной миссии (например, в случае, когда обрабатывается полная коммуникационная емкость). Такой модульный подход можно использовать либо в архитектурах пространственного переключения, либо в архитектуре цифрового процессора формирования луча, и они могут быть воплощены в прямой, обратной или в ячеистой архитектуре. Архитектуры цифрового формирования луча большого масштаба могут потребовать дополнительных аналоговых аппаратных средств для соединения множества модулей процессоров.

Модульный подход обеспечивает решение с малым риском, поскольку, после того, как модуль интегрированного процессора будет разработан и проверен, множество копий проверенного модуля можно использовать для построения общего интегрированного процессора для конкретной миссии. Кроме того модуль центрального процессора можно использовать как обобщенный структурный блок процессора в определенном диапазоне типов миссий, характеризуемых либо требованиями пространственного переключения, либо требованиями цифрового формирования луча, что, таким образом, дополнительно снижает риск и невозвратные затраты.

В предпочтительном варианте воплощения каждый каскад цифрового процессора дополнительно содержит A/D преобразователь, связанный с каждым входным портом и выполненный с возможностью преобразования сигнала восходящей линии заданной ширины полосы в форму цифровой выборки; D/A преобразователь, связанный с каждым из выходных портов и выполненный с возможностью преобразования обработанного цифрового сигнала заданной ширины полосы в аналоговый сигнал нисходящей линии; средство цифровой обработки, содержащее множество демультиплексоров частоты, каждый из которых соединен с одним или более из множества A/D преобразователей и выполнен с возможностью разделения дискретизированной ширины полосы одного или более дискретизированных сигналов восходящей линии в множество каналов; средство обработки уровня канала, ассоциированное с каждым из каналов и выполненное с возможностью маршрутизации обработанных каналов в любой из множества выходных портов; множество мультиплексоров частоты, каждый из которых соединен со средством обработки уровня канала и с одним или более из множества D/A преобразователей и выполнен с возможностью комбинирования множества маршрутизируемых каналов.

В одном варианте выполнения каскад обработки уровня канала содержит систему пространственного переключателя, выполненную с возможностью гибкой маршрутизации заданного входного канала в один или более мультиплексоров частоты, ассоциированных с выходными портами. В альтернативном варианте выполнения каскад обработки уровня канала содержит систему диаграммообразующей схемы. Каскад обработки уровня канала, предпочтительно, также содержит переключатель памяти, выполненный с возможностью предоставления гибкой маршрутизации между частотными интервалами восходящей и нисходящей линии.

Каскад предварительной обработки каждого модуля интегрированного процессора ассоциирован с множеством входных портов модуля цифрового процессора и выполнен с возможностью изоляции заданной полосы частот из восходящей линии для преобразования с понижением частоты изолированной полосы до промежуточной частоты и приложения сигнала, преобразованного с понижением частоты, к одному или более из множества входных портов. Каскад предварительной обработки может содержать цепь предварительной обработки, ассоциированную с каждым из входных портов, или множество цепей процессора предварительной обработки, выходы которых могут быть частотно мультиплексированы для предоставления заданных входных сигналов в один или более из входных портов.

Кроме того, каскад последующей обработки каждого модуля интегрированного процессора ассоциирован с множеством выходных портов каскада цифрового процессора и выполнен с возможностью фильтрации и преобразования с повышением частоты сигналов нисходящей линии на соответствующие частоты. Каскад последующей обработки может содержать цепь последующей обработки, ассоциированную с каждым из выходных портов, или множество цепей последующей обработки, характеризуемых различными преобразованиями с повышением частоты и фильтрацией.

Предпочтительно, модуль интегрированного процессора может быть воплощен в одной из архитектуры системы ячеистой линии связи, прямой линии связи или обратной линии связи, или в виде комбинации этих архитектур.

В одном варианте выполнения, содержащем пространственную систему переключения, интегрированный модуль процессора выполнен с возможностью работы с одиночным возбуждением каждой из антенн луча, как в восходящей, так и в нисходящей линии. В этом случае интерфейсы модулей с антеннами принимают форму портов лучей. В других вариантах выполнения, содержащих систему формирования луча, антенна канала пользователя представляет собой фазированную антенную решетку, содержащую множество антенных элементов, или отражатель с облучателем в виде антенной решетки (AFR), содержащий множество точечных облучателей, смещенных от плоскости фокусирования рефлектора.

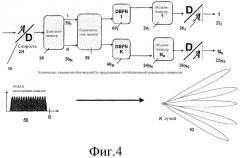

В еще одном варианте выполнения, содержащем систему диаграммообразующей схемы, когда модуль интегрированного процессора воплощен в архитектуре системы прямой линии, заданный входной канал предпочтительно разделен, чтобы подавать сигналы в множество выходных портов каскада цифрового процессора, при этом выборки канала умножаются на комплексные коэффициенты для управления свойствами луча нисходящей линии для этого канала. Аналогично, когда модуль интегрированного процессора воплощен в архитектуре системы обратной линии, заданный входной канал формируется путем суммирования сигналов из множества входных портов каскада цифрового процессора, при этом выборки канала умножаются на комплексные коэффициенты для управления свойствами луча восходящей линии для этого канала.

Восходящая линия или нисходящая линия предпочтительно относятся к наземным терминалам, поддерживающим частотное мультиплексирование множества каналов. В модуле, содержащем систему диаграммообразующей схемы, каждый канал восходящей и нисходящей линии может быть ассоциирован с отдельной цифровой диаграммообразующей схемой, при этом дискретизированный канал разделяется в соответствии с числом элементов/фидеров на соответствующей антенне нисходящей или восходящей линии. В другом варианте выполнения ширина полосы восходящей или нисходящей линии разделена на множество сегментов ширины полосы, и каждый сегмент прикладывается к или выводится из одного входного и выходного порта каскада цифрового процессора.

В одном варианте выполнения сигнал, соответствующий каждому лучу восходящей линии или антенному элементу/фидеру, подается на один входной порт каскада цифрового процессора, и/или сигнал, соответствующий каждому лучу нисходящей линии, или антенному элементу/фидеру, выводится из одного выходного порта каскада цифрового процессора. В качестве альтернативы, сигнал, соответствующий множеству лучей восходящей линии или антенных элементов/фидеров, подается на один входной порт, и/или сигнал, соответствующий множеству лучей нисходящей линии или антенных элементов/фидеров, выводится из одного выходного порта. В этом случае каскад предварительной обработки может быть выполнен с возможностью избирательного преобразования с понижением частоты сигналов из множества лучей восходящей линии или антенных элементов/фидеров на разные центральные частоты и суммирования сигналов, преобразованных с понижением частоты лучей или элементов/фидеров перед подачей этих сигналов во входной порт каскада цифрового процессора. В любом из этих вариантов выполнения может быть предусмотрен каскад последующей обработки для избирательного преобразования с повышением частоты сигнала из выходного порта каскада цифрового процессора в множество лучей нисходящей лини или антенных элементов/фидеров.

В других вариантах выполнения можно использовать множество модулей интегрированного процессора. Сигналы, соответствующие поднабору множества лучей восходящей лини или антенных элементов или фидеров, могут прикладываться ко входным портам каскада цифрового процессора каждого модуля, и/или сигналы, соответствующие поднабору множества лучей нисходящей линии или антенных элементов или фидеров, могут выводиться из выходных портов каскада цифрового процессора каждого модуля. В качестве альтернативы, сигналы, соответствующие всему множеству лучей восходящей линии или антенных элементов или фидеров, прикладываются к входным портам каскада цифрового процессора каждого модуля, и/или сигналы, соответствующие всему множеству лучей нисходящей линии или антенных элементов или фидеров, выводятся из выходных портов каскада цифрового процессора каждого модуля, причем каждый модуль выполнен с возможностью обработки разного сегмента общей ширины полосы луча или антенного элемента или фидера.

3. Краткое описание чертежей

Варианты выполнения изобретения будут теперь описаны только в качестве примера со ссылкой на приложенные чертежи, на которых:

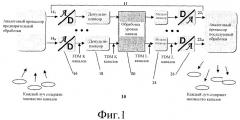

на фиг. 1 показано упрощенное схематичное представление обобщенного модуля интегрированного процессора в соответствии с настоящим изобретением;

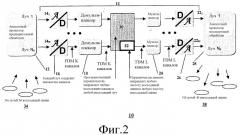

на фиг. 2 показано более подробное схематичное представление модуля интегрированного процессора по фиг. 1, включая в себя центральную пространственную функцию обработки пространственного переключения/переключения памяти, применяемую для архитектуры ячеистой системы, в которой используются антенны SFPB, как для восходящей, так и для нисходящей линии;

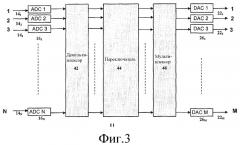

на фиг. 3 показано более подробное представление примера каскада цифрового процессора, который можно использовать как структурный блок модуля интегрированного процессора по фиг. 2;

на фиг. 4 показано упрощенное представление каскада цифрового процессора модуля интегрированного процессора по фиг. 1, в который встроена центральная функция обработки цифрового формирования луча, применяемая в архитектуре прямой системы, в которой используется антенна с фазированной антенной решеткой; и

на фиг. 5 показана схема архитектуры модуля с множеством интегрированных процессоров цифрового формирования луча, которая обеспечивает, функцию как прямой, так и обратной линии связи, в соответствии с вариантом выполнения настоящего изобретения.

4. Подробное описание изобретения

Перед описанием различных вариантов выполнения настоящего изобретения, которые выполнены в различных системных архитектурах, в которых используется, либо пространственный переключатель/переключатель памяти, или функция цифрового процессора формирования луча, вначале будет описана основная структура общего модуля процессора.

Как показано на фиг. 1, общий модуль 10 интегрированного процессора содержит аналоговый каскад 12 предварительной обработки, предназначенный для предварительной обработки входных сигналов перед A/D преобразованием, каскад 11 цифрового процессора, содержащий множество входных портов 141-N, причем каждый входной порт имеет A/D преобразователь 16, который преобразует входную полосу, представляющую интерес, в форму цифровой выборки, и цифровой демультиплексор 18, который разделяет общую входную полосу на множество каналов. Каскад 11 цифрового процессора имеет множество выходных портов 221-М, каждый из которых содержит цифровой мультиплексор 24, который комбинирует узкополосные каналы, и D/A преобразователь 26 для преобразования комбинированного сигнала, чтобы обеспечить выходной сигнал аналогового порта. Аналоговый каскад 28 предварительной обработки ассоциирован с выходными портами каскада 11 цифрового процессора для преобразования с повышением частоты выходного сигнала до требуемой частоты и фильтрации нежелательных изображений. Хотя на фиг. 1 показан только один модуль интегрированного процессора, следует понимать, что в системе обработки полезной нагрузки спутника связи может содержаться один или больше таких идентичных модулей в зависимости от характеристик антенны и ширины полосы восходящей и нисходящей линии для конкретной миссии.

Как показано на фиг. 1, между входными демультиплексорами 18 и выходными мультиплексорами 24 каскада 11 цифрового процессора, каскад 20 уровня обработки центрального канала (обычно пространственный переключатель/переключатель памяти или система цифрового формирования луча) предусматривает механизм для гибкой маршрутизации каналов между входными и выходными портами, чтобы гибко отображать каналы между частотами входных и выходных портов и, в случае цифрового формирования луча, для предоставления гибкого комплексного взвешивания сигналов каналов для управления свойствами луча. Следует понимать, что термин "модуль интегрированного процессора" может относиться к физическому интегрированию различных компонентов модуля или к воплощению в виде дискретных компонентов.

4.1 Архитектура пространственного переключателя/переключателя памяти

На фиг. 2 представлена архитектура ячеистой системы, в которой используются антенны с одиночным возбуждением каждого луча (SFPB), в которых интегрирован модуль 10 интегрированного процессора, воплощающий архитектуру 30 пространственного переключателя и архитектуру 32 переключателя памяти, как функции 20 центрального процессора уровня канала каскада 11 цифрового процессора. Восходящая линия 34 включает в себя множество направленных лучей Nu 36, каждый из которых содержит ряд каналов, мультиплексированных с разделением частоты (FDM), расположенных в доступных частотных интервалах в пределах общей полосы 34 восходящей линии. При этом возможно повторное использование частоты между множеством наземных терминалов, которые совместно используют один и тот же частотный интервал, при условии, что лучи находятся достаточно далеко друг от друга для ограничения взаимных помех. Нисходящая линия 38 содержит Nd направленных лучей 40, при этом каждый луч 40 содержит ряд каналов FDM, расположенных в доступных частотных интервалах. В предельном случае может потребоваться возможность гибкой маршрутизации любого из каналов восходящей линии в любой частотный интервал в любых лучах нисходящей линии.

Как описано со ссылкой на фиг. 2, каскад 11 цифрового процессора модуля 10 интегрированного процессора содержит множество N входных портов 141-N, и множество М выходных портов 221-M, где N может представлять собой то же или другое число, чем М. Каждый из лучей восходящей линии 36 и нисходящей линии 40 обычно ассоциирован с одним входным портом 141-N и выходным портом 221-M, соответственно, в каскаде 11 цифрового процессора. Каждый луч 36 восходящей линии вначале подвергают функции аналоговой предварительной обработки в каскаде 12 аналоговой предварительной обработки, где представляющую интерес полосу частот изолируют для исключения наложения спектров при последующей A/D выборке (то есть, любые находящиеся вне полосы сигналы могут накладываться в полосу в результате обработки выборки), и преобразуют с понижением частоты до промежуточной частоты (IF), пригодной для последующей выборки. Каскад 12 предварительного процессора может быть физически интегрирован с каскадом 11 цифрового процессора или может представлять собой отдельный компонент, внешний для каскада 11 цифрового процессора.

Предварительно обработанный сигнал 36 луча восходящей линии подают во входные порты 141-N и выполняют их выборку в A/D преобразователе 16 для представления сигналов всего луча в виде последовательности цифровых слов. A/D преобразователь 16 должен работать с достаточной высокой частотой выборки для представления всей полосы частот, представляющей интерес (максимальная частота fin выборок в секунду), которая, в свою очередь, определяет максимальную ширину полосы, которая может дискретизироваться (по теореме Найквиста fin/2, предполагая действительную выборку) и с достаточной длиной слова для ограничения шумов квантования, связанных с преобразованием.

Для сигналов луча после выборки затем выполняют цифровое демультиплексирование в демультиплексоре 18 на K отдельных каналов, путем применения соответствующей архитектуры цифрового демультиплексирования. Она обычно включает в себя эффективный алгоритм на основе FFT и децимацию частоты выборки, соответствующую отдельным каналам. Каждый канал может содержать одну или множество несущих или, в случае заданной широкополосной несущей, может быть занято целое число каналов. В последнем случае следует понимать, что конструкция фильтра 18 демультиплексора такова, что свойство непрерывности позволяет реконструировать более широкополосные несущие в функции мультиплексирования частоты. На практике отдельные выборки каналов мультиплексируют с разделением по времени (TDM) на кадры, где заданный кадр содержит одну выборку для каждого канала.

Функция 30 центрального пространственного переключения работает с входными каналами после выборки, обеспечивая направление сигналов из любого входного порта 141-N в любой выходной порт 221-M. Заданный входной канал может быть направлен во множество выходных портов (возможность многоадресной передачи или широковещательной передачи), и любой входной канал может быть направлен в любой частотный интервал выбранного выходного порта 221-M. Гибкость при отображении частоты достигается путем управления функциями считывания - записи в архитектуре 32 переключателя памяти, ассоциированной с функцией 20 обработки уровня центрального канала. Как описано выше, выходы демультиплексоров (18) принимают форму кадров TDM, где заданный кадр содержит одиночную выборку для каждого канала, и упорядочивание выборок в пределах кадра соотносят с частотой канала. Отображением частоты можно управлять путем изменения порядка выборок в пределах этих кадров TDM путем записи входных кадров в память и считывания выходных кадров из памяти с другим порядком выборки перед подачей в мультиплексоры.

Каждый выходной порт 221-M имеет мультиплексор 24 частоты, который комбинирует каналы, направляемые в него, которые, как описано выше, теперь имеют форму кадров TDM с местами размещения выборок, в соответствии с требуемым частотным отображением. Каждый выходной порт 221-M имеет D/A преобразователь 26, который работает с частотой fout выборок в секунду, которая, в свою очередь, определяет максимальную ширину полосы выходного сигнала (в соответствии с теоремой Найквиста, fout/2, предполагая действительную выборку). fout обычно может быть такой же, как fin, но следует понимать, что это не обязательно. Преобразованный сигнал порта выходного луча преобразуют с повышением частоты до требуемой частоты в каскаде 28 последующей обработки, связанном с выходными портами 221-M каскада 11 цифрового процессора, и применяют фильтрацию для устранения нежелательных изображений D/A преобразователя. Каскад 28 последующего процессора может быть физически интегрирован с каскадом 1 цифрового процессора 11 или может быть реализован внешним образом.

На фиг. 3 показан пример каскада обобщенного цифрового процессора для модуля интегрированного процессора в соответствии с одним вариантом выполнения настоящего изобретения, который можно использовать как структурный блок для процессора более крупного масштаба с архитектурой пространственного переключения. Каскад 11 цифрового процессора 11 содержит N входных портов 141-N, каждый с ассоциированным A/D преобразователем 161-N, и М выходных портов 221-M, каждый с ассоциированным D/A преобразователем 261-N. Из М входных и М выходных портов ряд из них будут обычно активны, а другие обеспечивают избыточность в системе. Цифровую обработку сигналов можно рассматривать как широкое разделение между тремя рангами функций 42, 44, 46, с множеством идентичных функциональных блоков в каждом ранге, между которыми обеспечивается возможность полного соединения. Первый ранг 42 обеспечивает демультиплексирование частоты входных сигналов, подвергаемых выборке. Третий ранг 46 аналогично обеспечивает формирование во время мультиплексирования частоты выходных сигналов после выборки. Второй центральный ранг 44 обеспечивает гибкую маршрутизацию между входными 141-N и выходными 221-M портами; в данном примере (фиг. 2) заданная функция 30 переключения принимает входные сигналы из каждого блока 18 демультиплексирования и обеспечивает выходы в каждый блок 24 мультиплексирования.

4.1.1. Примеры применения модульного подхода к архитектуре пространственного переключателя

При рассмотрении архитектур пространственного переключателя основные параметры, которые характеризуют общие требования процессору, представляют собой количество лучей восходящей и нисходящей линии, ширину полосы, занимаемую лучами, и ширину полосы, необходимую для удовлетворения требований гибкости. Аналогично, основные параметры, которые характеризуют заданный интегрированный модуль процессора, представляют собой количество входных и выходных портов его каскада цифрового процессора и ширину полосы цифровой обработки этих портов. Ряд ситуаций, характеризуемых разными требованиями к миссии, будут описаны ниже для иллюстрации гибкости модульного подхода в соответствии с настоящим изобретением.

Если количество лучей восходящей линии 36 и нисходящей линии 40 меньше, чем количество входных 141-N и выходных 221-M портов, соответственно, каскада цифрового процессора модуля 10, и если ширины полосы лучей восходящей линии 36 и нисходящей линии 40 меньше, чем у соответствующих входных 141-N и выходных 221-М портов, тогда будет достаточен один модуль 10 с прямым отображением лучей в порты модуля. В действительности, такая упрощенная ситуация, вероятно, может соответствовать малой миссии или комбинированной миссии.

Если количество лучей восходящей линии 36 и/или нисходящей линии 40 превышает количество входных портов 141-N и/или выходных портов 221-М каскада 11 цифрового процессора модуля 10, но ширина полосы лучей значительно меньше, чем соответствующая ширина полосы порта каскада цифрового процессора, тогда снова один модуль можно использовать при ассоциировании каждого порта каскада 11 цифрового процессора с множеством лучей. В таком случае каскад 12 предварительного процессора, ассоциированный с входными портами 141-N, имеет такую структуру, что группу сигналов 34 луча преобразуют с понижением частоты на разные центральные частоты (выбранные таким образом, чтобы исключить перекрытие) и суммируют перед выборкой A/D преобразователем 16 входного порта. Аналогично, каждый выходной порт 221-М каскада 11 цифрового процессора модуля 10 содержит сигналы, соответствующие множеству лучей 38, но снова избирательно смещенных по частоте таким образом, чтобы исключить перекрытие. После D/A преобразования выходного порта выходные сигналы подвергают различным видам преобразования с повышением частоты в каскаде 28 последующей обработки для установки сигналов луча на требуемых центральных частотах и выполняют фильтрацию полосы, чтобы отсечь нежелательные сигналы лучей и изображения D/A преобразователя.

Например, рассмотрим модуль 10 интегрированного процессора, содержащий каскад 11 цифрового процессора 11 с десятью входными портами 141-10 и десятью выходными портами 221-10, каждый из которых выполнен с возможностью размещения ширины полосы 200 МГц. Миссия спутника связи характеризуется двадцатью лучами восходящей линии 36 и двадцатью лучами нисходящей линии 40, каждый из которых имеет ширину полосы 100 МГц. В каскаде 12 предварительного процессора комбинируют десять пар сигналов 36 луча восходящей линии с их центральными частотами, смещенными на 100 МГц таким образом, что каждая пара сигналов луча занимает всю ширину полосы 200 МГц входного порта 141-10 каскада цифрового процессора. Обратное относится к отображению выходных портов 221-10 в лучи 40 нисходящей линии. Эта концепция составления поддиапазонов представляет собой предмет изобретения заявки на патент Великобритании № GB 0708940.2, поданной 10 мая 2007 г.

Если произведение лучей восходящей линии 36 или нисходящей линии 40 и соответствующей ширины полосы луча превышает произведение соответствующих чисел N входов 141-N и М выходных портов 221-M и соответствующей ширины полосы порта каскада 11 цифрового процессора модуля интегрированного процессора, тогда, очевидно, одного модуля недостаточно для поддержки требований миссии. Различные конфигурации могут быть воплощены в этой ситуации. В наименее сложной конфигурации предусмотрено множество модулей. Лучи восходящей линии 36 и нисходящей линии 40 разделяют на поднаборы, где каждый из поднаборов поддерживается одним из множества модулей 10 интегрированного процессора. И снова множество сигналов луча восходящей линии и поднабора луча может быть мультиплексировано в каждый входной порт 141-N каскада 11 цифрового процессора соответствующего модуля.

Например, для конкретной миссии, содержащей двадцать лучей восходящей линии 361-20 и двадцать лучей нисходящей линии 401-20, каждый из которых имеет ширину полосы 200 МГц, предусмотрены два модуля 10A и 10b интегрированного процессора. Каскад 11 цифрового процессора каждого из модулей 10а и 10b содержит десять входных каналов 141-10 и выходных каналов 221-10 портов и выполнен с возможностью поддержки поднабора из десяти лучей восходящей линии 361-10, 361-20 и лучей нисходящей линии 401-10, 401-20, при этом полную ширину полосы подвергают выборке в каждом входном порту 141-10. Однако такая конфигурация не позволяет обеспечить полную гибкость между всеми лучами восходящей и нисходящей линии, поскольку каналы в заданном поднаборе лучей 361-10 или 361-20 восходящей линии могут быть направлены только к лучам в пределах соответствующего поднабора 401-10, 401-20 нисходящей линии, соответственно. В некоторых случаях, этого может быть недостаточно для удовлетворения требований трафика в пределах определенной миссии.

В альтернативном подходе, который позволяет предоставить весь луч для обеспечения гибкости маршрутизац