Преобразователь параллельного кода баркера в параллельный двоичный код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства ¹â€”

Заявлено 02.IV.1968 (¹ 1230057/18-24) Кл. 42m>, 5/02 с присоединением заявки №вЂ”

Приоритет

Опубликовано 05.VI I I.1969. Бюллетень ¹ 25

Дата опубликования описания 15.|.1970

МПК С 061

УДК 681.325.53 (088.8) Комитет по делам иаобрвтений и открытий при Совете Министров

СССР

Авторы изобретения

Л. М. Асоян, Г. Г. Белкин, P. Х. Григорян, К. Х. Каранян, С. С. Абаджян и М. Г, Геворкян

Заявитель

ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА БАРКЕРА

В ПАРАЛЛЕЛЬНЪ|Й ДВОИЧНЫЙ КОД

Предложение относится к автоматике и вычислительной технике.

Известны преобразователи кода Баркера в параллельный двоичный код, содержащие входной и выходной регистры и логические схемы.

Предложенное устройство отличается тем, что в нем единичные и нулевые выходы триггеров каждого разряда подключены соответственно к двум парам схем «И», выходы схем

«И» каждой пары через схемы «ИЛИ» и линии задержки подключены к входам второго триггера данного разряда, выход схемы «ИЛИ», связанной с единичными выходами триггеров данного .разряда, подключен также к схемам

«И», соединенным с выходами второго триггера следующего разряда, а выход схемы

«ИЛИ», связанной с нулевыми выходами триггеров, подключен к схемам «И», связанным с выходами, первого триггера следующего разряда; единичные выходы триггера младшего разряда и вторых триггеров следующих разрядов служат выходами, соответствующими двоичному коду.

Предложенное устройство основано на реализации уравнений:

P + — Р,. A > + Р,В«1, (1)

P«i — — Р,А« + Р,В«, (2) где Р, — значение двоичного кода i-го разряда;

Р«1 †значен двоичного кода следующего старшего (i+1)-го разряда;

Р; — инверсное значение двоичного кода в i-ом разряде;

5 А«1 и B«> — значения двух (i+1)-х подраз:рядов в коде Баркера.

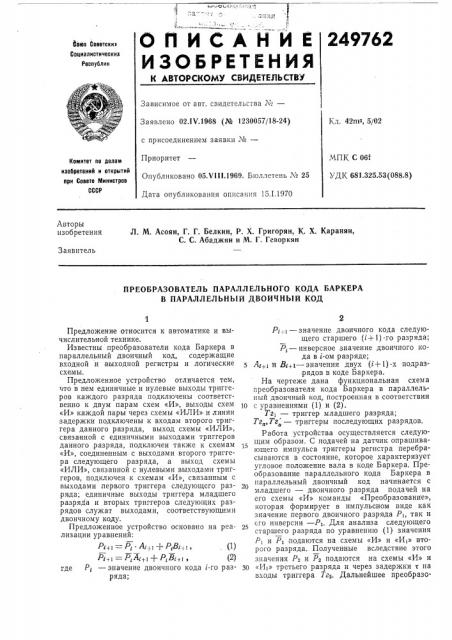

На чертеже дана функциональная схема преобразователя кода Баркера в параллельный двоичный код, построенная в соответствии

10 с уравнениями (1) и (2).

Тг| — триггер младшего разряда;

Tz„, Тㄠ— триггеры последующих разрядов.

Работа устройства осуществляется следую15 щим образом. С подачей на датчик опрашивающего импульса триггеры регистра перебрасываются в состояние, которое характеризует угловое положение вала в коде Баркера. Преобразование параллельного кода Баркера в параллельный двоичный код начинается с

20 младшего — двоичного разряда подачеи на его схемы «И» команды «Преобразование», которая формирует в импульсном виде как значение первого двоичного разряда Р1, так и

25 сго инверсии — P,. Для анализа следующего старшего разряда по уравнению (1) значения

Р, и Р, подаются на схемы «И» и «И1» второго разряда. Полученные вследствие этого значения Р и Р подаются на схемы «И» и

30 «И1» третьего разряда и через задержки т на входы триггера Тга. Дальнейшее преобразо249762

/г аУ Бпф/ген

$3@-О е о 9 î с /7P-3 д 0оичиьш жл

Составитель И. Н. Горелова

Редактор К. С. Опенченко Текред Л. К. Малова Корректор А, С, Колабин

Заказ 3353/!6 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва 7К-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2 вание кода Баркера в двоичный в остальных разрядах с последующей записью значений двоичных разрядов в триггерах соответствующих подразрядов В происходит аналогичным образом. 3а счет включения задержек между выходами схемы, формирующей значения прямого и инверсного изображения двоичного кода Р,. и Р,, и выходами триггера данного !

-го разряда возможно разделение во времени использования значений Р,. и Р; для образования значений двоичного кода в (i+1)-и разряде и запоминания двоичного значения кода в -м разряде. Через время t на всех триггерах подразрядов В устанавливается двоичный код, эквивалент углового положения вала, Таким образом, приведенная схема совмещает функции преобразователя кода Баркера в параллельный двоичный код с функциями запоминания двоичного кода, Предмет изобретения

Преобразователь параллельного кода Баркера в параллельный двоичный код, содержащий регистр, каждый разряд которого, за исключением младшего разряда, выполнен на двух триггерах, соединенных с шинами, соответствующими подразрядам кода Баркера, и логические схемы, отлича ощийся тем, что, с целью упрощения устройства,,в нем единичные и нулевые выходы триггеров каждого разряда подключены соответственно к двум парам схем

< И», выходы схем «И» каждой пары через схемы «ИЛИ» и линии задержки подключены к входам второго триггера данного разряда; выход схемы «ИЛИ», связанной с единичными ьыходами триггеров данного разряда, подключен также к схемам «И», соединенным с выходами второго триггера следующего .разряда, а выход схемы «ИЛИ», связанной с нулевыми выходами триггеров, подключен к схемам «И», связанным с выходами первого триггера следующего разряда; единичные выходы триггера младшего разряда и вторых триггеров следующих разрядов служат выходами, соответствующими двоичному коду.