Устройство предсказания исключительной ситуации "потеря точности" блока операции "умножение с накоплением"

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники, а именно к вычислительным системам на основе микропроцессоров с блоками вещественной и специализированной комплексной арифметики, включающими в себя подблоки операции умножения с накоплением. Техническим результатом является ускорение процесса выполнения потока независимых команд «умножения с накоплением» при разрешенной исключительной ситуации «потеря точности». Устройство содержит подблок предсказания суммы мантисс, счетчик старших нулей суммы мантисс, регистры мантисс чисел, входные регистры экспонент чисел, счетчик младших нулей мантиссы слагаемого, подблок вычисления сдвига выравнивания и предсказания сдвига предварительной нормализации, компаратор ранней потери точности, счетчик младших нулей суммы мантисс, компаратор поздней потери точности. 5 ил., 1 табл.

Реферат

Изобретение относится к области вычислительной техники, а именно: к вычислительным системам на основе микропроцессоров с сопроцессорами вещественной и комплексной арифметики.

Известны различные варианты структурной организации вычислительных устройств микропроцессоров, зависящие от способов обработки исключительных ситуаций при операциях над вещественными или комплексными числами. Так, в системах поддерживающих точные исключения стандарта IEEE754 необходимым является присутствие устройства, реализующего механизм отмены результатов всех операций, выполнившихся после операции, которая вызвала исключение. Так как длительность большинства инструкций вещественной арифметики больше длительности целочисленных операций, то при одновременном выполнении целочисленной и вещественной инструкций, возможна ситуация, при которой целочисленная инструкция будет завершена до окончания вещественной и отменить результат первой очень затруднительно.

Поэтому для правильной работы микропроцессора в режиме разрешения исключительных ситуаций, таких как «переполнение», «потеря значимости», «потеря точности», используют такой режим его работы, при котором на время выполнения текущей арифметической операции выполнение других команд параллельно текущей не разрешается. Такой режим работы значительно снижает скорость вещественных вычислений. Для того чтобы сгладить падение производительности, необходимо использовать устройство предсказания исключительных ситуаций, которое встраивается в исполнительный арифметический подблок и обеспечивает заблаговременный расчет признака возможной исключительной ситуации. Данный предсказанный признак, будет использован микропроцессором для принятия решения о последующей выдаче арифметических команд на исполнительные подблоки.

Эффективность применения устройства предсказания исключительных ситуаций зависит от точности предсказания и стадии выполнения инструкции, на которой может быть осуществлено предсказание. Эффективность будет тем выше, чем больше длительность арифметической инструкции, при условии, что возможно осуществить предсказание на ранних стадиях.

Так как вычислительные секции современных микропроцессоров строятся в основном с применением вещественных модулей «умножения с накоплением», то обеспечение последних устройством предсказания исключительных ситуаций даст возможность получить увеличение быстродействия.

Предсказание исключительной ситуации «потеря точности» является более сложным, чем предсказание ситуаций «переполнение» и «потеря значимости» и сопряжено со сложностью предсказания наличия отбрасываемых при округлении, значащих битов промежуточного результата. Обычно такой признак теряемых при округлении битов вычисляют после процесса окончательной нормализации промежуточного результата.

Известен исполнительный подблок вещественной арифметики, выполняющий операции «умножение», «сложение», «умножение с накоплением», «деление», «квадратный корень» и имеющий устройство предсказания исключительных ситуаций переполнения и потери значимости (патент US 6,631,392, кл. G06F 7/38, опубл. 7.10.2003).

В качестве недостатка данного подблока необходимо отметить то, что устройство предсказания исключительных ситуаций обслуживает сразу несколько арифметических подблоков вещественной арифметики (сумматор, умножитель, подблок квадратного корня/деления) и эта особенность делает затруднительным процесс определения принадлежности предсказанного признака конкретной команде.

Наиболее близким по технической сути и достигаемому результату является устройство, выполняющее вещественную операцию «умножение с накоплением» и содержащее ускоренную схему вычисления бита-признака потери точности. Схема вычисления бита-признака потери точности состоит из предсказателя значения промежуточной суммы, счетчика старших нулей предсказанной суммы, сумматора промежуточного значения, подсхемы нормализации промежуточного значения, подсхем дизъюнкции, включенных после каждой стадии подсхемы нормализации, которые определяют наличие отбрасываемых значащих при округлении битов (патент US 5,771,183, кл. G06F 7/00, опубл. 23.07.1998 г.).

Недостатком данного прототипа является структурная особенность, которая замедляет процесс выполнения потока независимых команд «умножения с накоплением» (при включенных IEEE754 исключениях) и которая заключается в том, что расчет бита-признака потери точности осуществляется после основного суммирования мантисс (с распространением переноса) и одновременно с процессом нормализации результата суммирования. Такая организация дает возможность несколько ускорить расчет бита-признака потери точности и завершить его одновременно с окончанием процесса нормализации, но не обеспечивает возможность досрочного расчета и, следовательно, предсказания бита-признака потери точности. Это ограничение не дает сформировать достаточное условие флага исключительной ситуации потери точности на ранних этапах работы конвейера модуля, и сигнализировать об этом ядру микропроцессора, не дожидаясь окончания расчета.

Технический результат от использования данного изобретения заключается в обеспечении ускорения процесса выполнения потока независимых команд «умножения с накоплением» при разрешенной исключительной ситуации «потеря точности».

Указанный технический результат достигается тем, что устройство предсказания исключительной ситуации «потеря точности» блока операции «умножение с накоплением», включающее подблок предсказания суммы мантисс, счетчик старших нулей суммы мантисс, согласно изобретению снабжено входными регистрами мантисс чисел В и С, входными регистрами экспонент чисел А, В и С, счетчиком младших нулей мантиссы слагаемого, подблоком вычисления сдвига выравнивания и предсказания сдвига предварительной нормализации, компаратором ранней потери точности, счетчиком младших нулей суммы мантисс, компаратором поздней потери точности, при этом счетчик младших нулей мантиссы слагаемого связан с входным регистром мантиссы числа С для осуществления подсчета числа младших нулей мантиссы слагаемого С и компаратором ранней потери точности для сравнения со сдвигом выравнивания, выходящим из подблока вычисления сдвига выравнивания и предсказания сдвига предварительной нормализации, связанного с входным регистром экспоненты числа А, входным регистром экспоненты числа В и входным регистром экспоненты числа С для получения признака наличия значащих битов выравненной мантиссы слагаемого за пределами разрядности внутреннего представления данных, а компаратор поздней потери точности связан со счетчиком старших нулей суммы мантисс и счетчиком младших нулей суммы мантисс, которые связаны с подблоком предсказания суммы мантисс для получения признака наличия значащих битов мантиссы результата, в отбрасываемой при округлении части.

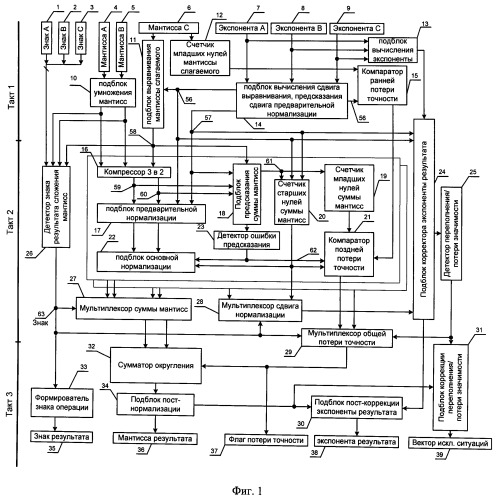

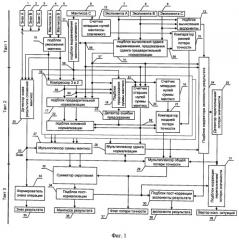

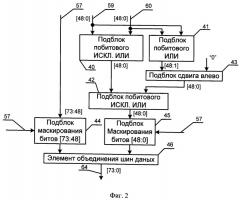

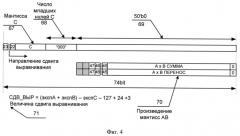

Изобретение реализовано на примере блока операции «умножение с накоплением» одинарной точности, как наиболее простом и поясняется чертежами, где на фиг.1 представлена структурная схема блока вычисления операции «умножение с накоплением» одинарной точности без промежуточного округления со встроенной схемой предсказания потери точности. На фиг.2 представлена детализированная структурная схема подблока предсказания суммы мантисс. На фиг.3 представлена детализированная структурная схема счетчиков младших и старших нулей, а также компаратора поздней потери точности. На фиг.4 и фиг.5 представлены иллюстрации, поясняющие алгоритм работы схем предсказания ранней и поздней потери точности. В случае применения изобретения в блоке «умножение с накоплением» другой точности, константы сравнения компараторов, разрядности счетчиков нулей будут зависеть от разрядности мантисс входных чисел.

В состав блока вычисления операции «умножение с накоплением» одинарной точности без промежуточного округления со встроенной схемой предсказания потери точности входит:

входной регистр знака числа А 1, входной регистр знака числа В 2, входной регистр знака числа С 3, входной регистр мантиссы числа А 4, входной регистр мантиссы числа В 5, входной регистр мантиссы числа С 6, входной регистр экспоненты числа А 7, входной регистр экспоненты числа В 8, входной регистр экспоненты числа С 9, подблок умножения мантисс 10, подблок выравнивания мантиссы слагаемого 11, счетчик младших нулей мантиссы слагаемого 12, подблок вычисления экспоненты 13, подблок вычисления сдвига выравнивания и предсказания сдвига предварительной нормализации 14, компаратор ранней потери точности 15, компрессор Зв2 16, подблок предварительной нормализации 17, подблок предсказания суммы мантисс 18, счетчик младших нулей суммы мантисс 19, счетчик старших нулей суммы мантисс 20, компаратор поздней потери точности 21, подблок основной нормализации 22, детектор ошибки предсказания 23, подблок корректора экспоненты результата 24, детектор переполнения/потери значимости 25, детектор знака результата сложения мантисс 26, мультиплексор суммы мантисс 27, мультиплексор сдвига нормализации 28, мультиплексор общей потери точности 29, подблок пост-коррекции экспоненты результата 30, подблок коррекции переполнения/потери значимости 31, сумматор округления 32, формирователь знака операции 33, подблок пост-нормализации 34, выходной регистр знака результата 35, выходной регистр мантиссы результата 36, выходной регистр флага потери точности 37, выходной регистр экспоненты результата 38, выходной регистр вектора исключительных ситуаций 39.

В свою очередь, подблок предсказания суммы мантисс 18 состоит из:

подблока побитового исключающего «ИЛИ» 40, подблока побитового «ИЛИ» 41, подблока побитового исключающего «ИЛИ» 42, подблока сдвига влево 43, подблока 44 маскирования битов [73:48], подблока 45 маскирования битов [48:0], элемента объединения шин данных 46.

Совокупность счетчика младших нулей суммы мантисс 19, счетчика старших нулей суммы мантисс 20 и компаратора поздней потери точности 21 состоит из:

счетчика 1 старших нулей битов [48:23] 47, счетчика 2 старших нулей битов [22:0] 48, счетчика младших нулей битов [48:0] 49, мультиплексора старших нулей 50, подблока маскирования 51, формирователя константы сравнения 52, компрессора 3в2 53, сумматора компаратора поздней потери точности 54, мультиплексора коррекции 55.

Описанное выше устройство работает следующим образом.

На вход блока поступают три операнда закодированных в формате IEEE754, каждое из чисел представлено полем экспоненты размером 8 бит, мантиссы - 24 бита и знака - 1 бит.

В первом такте работы схемы проводятся следующие действия:

в подблоке умножения мантисс 10 происходит умножение мантисс операндов А и В получаемых с входных регистров мантиссы числа А 4 и мантиссы числа В 5. Одновременно с этим происходит вычисление промежуточного значения экспоненты результата в подблоке вычисления экспоненты 13, а также значения сдвига выравнивания и предсказание сдвига предварительной нормализации в подблоке вычисления сдвига выравнивания, предсказания сдвига предварительной нормализации 14 на основе данных, поступаемых с входных регистров экспоненты числа А 7, экспоненты числа В 8, экспоненты числа С 9. Одновременно с этим, счетчик младших нулей мантиссы слагаемого 12, на основе данных, поступаемых с входного регистра мантиссы С 6, осуществляет подсчет числа младших нулей мантиссы слагаемого С. Величина младших нулей мантиссы слагаемого С сравнивается со сдвигом выравнивания в компараторе ранней потери точности 15, для получения флага наличия значащих битов выравненной мантиссы слагаемого за пределами разрядной сетки (74 бита) внутреннего представления результата. Далее, как только становятся готовы младшие биты значения сдвига выравнивания 56 (ЗНАЧ_СДВ_ВЫР_С), формируемые в подблоке вычисления сдвига выравнивания, предсказания сдвига предварительной нормализации 14, происходит выравнивание мантиссы слагаемого С в подблоке выравнивания мантиссы слагаемого 11.

Алгоритм работы схемы предсказания ранней потери точности проиллюстрирован на фиг.4. 67 - мантисса слагаемого С на входе схемы выравнивания. 68 - число младших нулей мантиссы, 69 - нулевые биты, дополняющие разрядность мантиссы до значения 74 бита. 70 - результат умножения мантисс операндов А и В в избыточной форме с сохранением переноса. 71 - значение сдвига выравнивания СДВ_ВЫР. Флаг ранней потери точности равен единице если:

ЗНАЧ_МЛ_НУЛ+(2*m+2)<СДВ_ВЫР, или

ЗНАЧ_МЛ_НУЛ+(2*m+2)<экспА + экспВ - экспС - bias+m+3, или

,

где экспА, экспВ, экспС - экспоненты обрабатываемых чисел в формате ieee754, m - разрядность мантиссы входных чисел, bias - значение смещения экспоненты.

Все действия второго такта работы дублируются, разделяясь на две ветви:

одна ветвь работает при условии, что больше результат умножения мантисс, чем мантисса слагаемого, вторая ветвь - при условии, что больше выравненная мантисса слагаемого. Это сделано, для того чтобы при вычитании была возможность выбрать модуль операции, а не выполнять преобразование отрицательного значения.

Каждая из ветвей схемы включает следующие действия над результатами первого такта:

осуществляется сложение результата умножения мантисс, представленного в избыточной форме с сохранением переноса, и выравненной мантиссы слагаемого в компрессоре 3в2 16. В подблоке предварительной нормализации 17 осуществляется предварительная нормализация промежуточного значения сложения мантисс на максимальную величину сдвига влево, равного 25 битам. Значение сдвига предварительной нормализации формируется в первом такте работы модуля, в подблоке вычисления сдвига выравнивания, предсказания сдвига предварительной нормализации 14. Одновременно с процессом предварительной нормализации в подблоке предсказания суммы мантисс 18 осуществляется предсказание значения суммы, на основе выходных значений 59 из 60 компрессора 3в2 16, величины 56 сдвига выравнивания мантиссы слагаемого С, значения 58 выравненной мантиссы слагаемого С из первого такта.

Подробная структурная схема подблока предсказания суммы мантисс 18 приведена на фиг.2. Она представляет собой упрощенную схему двоичного сумматора, в котором значение полусуммы, формируемое в подблоке 40, складывается по модулю два с упрощенным значением переноса, который формируется в подблоке 41 и поступает в текущую позицию. Упрощенный сигнал переноса учитывает только биты в предыдущей позиции. А именно, при суммировании двоичных чисел An и Bn, значение предсказанной суммы

Подблок предсказания суммы мантисс 18 логически делится на две составляющие: на старшую часть (биты [73:48]) и остальную часть (биты [48:0]). В качестве значения старшей части берется значение битов [73:48] от выравненной мантиссы слагаемого С 58. Для предсказания значения битов [48:0] суммы используется формула (2).

Предсказанные значения старшей части (биты [73:48]) и остальной части (биты [48:0]) проходят через подблоки маскирования 44 и 45, в которых, на основании признака 57 нахождения сдвига выравнивания 56 в диапазоне значений от 0 до 25 включительно, происходит формирование корректного значения предсказанной суммы, части которой затем объединяются элементом объединения шин данных 46.

Сформированное таким способом неточное значение суммы имеет величину младших нулей, равных точному значению у суммы, которая была бы получена при помощи полного двоичного сумматора, а число старших нулей меньше на один или равно точному значению. В таблице 1 приведены возможные варианты значений старших нулей в промежуточной сумме разрядностью 74 бита.

| Таблица 1 | ||

| Возможные варианты значений старших нулей в промежуточной сумме | ||

| Значение сдвига выравнивания мантиссы С, ЗНАЧ_СДВ_ВЫР_С | ||

| >0, <25 | >25 | |

| Значение старших нулей интервала битов [73:48], ЗНАЧ_СТ_НУЛ0 | ЗНАЧ_СДВ_ВЫР_С | >=25 |

| Значение старших нулей интервала битов [48:23], ЗНАЧ_СТ_НУЛ1 | 0 | подсчет |

| Значение старших нулей интервала битов [22:0], ЗНАЧ СТ НУЛ2 | 0 | подсчет, если ЗНАЧ_СТ_НУЛ1=25 |

Счетчик младших нулей суммы мантисс 19 осуществляет подсчет младших нулей предсказанной суммы. Счетчик старших нулей суммы мантисс 20 осуществляет подсчет старших нулей предсказанной суммы. Затем значения младших и старших нулей сравниваются с константой в компараторе поздней потери точности 21 для получения флага наличия значащих битов мантиссы результата, в отбрасываемой при округлении части.

Совокупность счетчика старших нулей суммы мантисс 20, счетчика младших нулей суммы мантисс 19 и компаратора поздней потери точности 21 функционирует следующим образом:

поле битов внутреннего значения суммы делится на три части (таблица 1), в которых независимо производится подсчет старших нулей. В качестве значения старших нулей поля битов [73:48] (ЗНАЧ_СТ_НУЛ0) берется значение сдвига выравнивания мантиссы слагаемого С 56 (ЗНАЧ_СДВ_ВЫР_С), если оно не превышает значения 25. Если ЗНАЧ_СДВ_ВЫР_С>25, то число нулей в поле битов [73:48] составляет 25 или 26. Значение старших нулей поля битов [48:23] (ЗНАЧ_СТ_НУЛ1) вычисляется в подблоке счетчика 1 старших нулей битов [48:23] 47 и учитывается только если ЗНАЧ_СДВ_ВЫР_С>25, иначе оно равно 0. Значение старших нулей поля битов [22:0] (ЗНАЧ_СТ_НУЛ2) вычисляется в подблоке счетчика 2 старших нулей битов [22:0] 48 и учитывается только если число старших нулей всего поля промежуточной суммы больше или равно значению 51, т.е. ЗНАЧ_СТ_НУЛ0+ЗНАЧ_СТ_НУЛ1=51, причем в этом случае не происходит поздней потери точности, и нет необходимости использовать ЗНАЧ_СТ_НУЛ2 для вычисления флага поздней потери точности, оно используется только для нормализации результата. Значение младших нулей поля битов [48:0] вычисляется в подблоке счетчика младших нулей битов [48:0] 49.

Алгоритм работы схемы предсказания поздней потери точности проиллюстрирован на фиг.5. 72 - мантисса результата операции «умножение с накоплением», представленная в избыточном виде с сохранением переноса. 74 - предсказанное значение суммы, имеющее число младших нулей 77, совпадающее со значением числа младших нулей полной суммы 73, число старших нулей 75, равное значению числа старших нулей полной сумы 73 или меньшее на один. Флаг поздней потери точности если:

, где m - разрядность мантиссы входных чисел,

78 - корректированное значение сдвига нормализации.

Таким образом, компаратор поздней потери точности 21, сравнивает сумму старших и младших нулей с константой. Если признак 57 нахождения сдвига выравнивания 56 в диапазоне значений от 0 до 25 включительно выставлен в "1", то в качестве числа старших нулей берется значение сдвига выравнивания 56 (ЗНАЧ_СТ_НУЛ0), а константа сравнения равна десятичному значению 49. Если признак 57 нахождения сдвига выравнивания 56 в диапазоне значений от 0 до 25 включительно выставлен в "0", то в качестве числа старших нулей берется значение ЗНАЧ_СТ_НУЛ1, а константа сравнения равна десятичному значению 24. Значение старших нулей поля битов [22:0] (ЗНАЧ_СТ_НУЛ2) не подается на компаратор, так как в случае, когда его необходимо учитывать, не происходит поздней потери точности. ЗНАЧ_СТ_НУЛ2, обрабатываясь в подблоке маскирования 51, через выход 66, подается на подблок основной нормализации 22.

Одновременно с предсказанием поздней потери точности в подблоке основной нормализации 22 осуществляется окончательная нормализация мантиссы результата и коррекция значения основного сдвига на основании сигнала коррекции, поступаемого с подблока детектора ошибки предсказания 23.

Параллельно с работой ветвей нормализации и предсказания суммы на основе данных, поступаемых с входных регистров знака числа А 1, знака числа В 2, знака числа С 3, значения произведения мантисс, а также значения 58 выравненной мантиссы слагаемого С вычисляется знак результата сложения мантисс в подблоке детектора знака результата сложения мантисс 26. На основании значения знака 63, выбираются значение нормализованной мантиссы с выхода одной из ветвей в мультиплексоре суммы мантисс 27, значение количества старших нулей для коррекции экспоненты - в мультиплексоре сдвига нормализации 28. Значение бита общей потери точности выбирается в мультиплексоре общей потери точности 29, где дополняется ранним признаком переполнения, формируемым в детекторе переполнения/потери значимости 25. Значение общего флага потери точности поступает на выходной регистр флага потери точности 37. Промежуточная корректировка экспоненты на основании значения старших нулей проводится в подблоке схемы коррекции экспоненты результата 24.

В третьем такте работы схемы проводятся следующие действия:

осуществляется сложение и округление значения мантиссы, представленной в избыточной форме в сумматоре округления 32. Затем проводится окончательная нормализация округленной мантиссы вследствие возможного переполнения в подблоке пост-нормализации 34. Переполнение мантиссы результата может происходить из-за округления. На основании возможного сигнала переполнения проводится окончательная корректировка экспоненты в подблоке пост-коррекции экспоненты результата 30, из которого значение экпоненты поступает на выходной регистр экспоненты результата 38. В подблоке коррекции переполнения/потери значимости 31 формируется вектор исключительных ситуаций, поступающий на выходной регистр вектора исключительных ситуаций 39. В подблоке формирователя знака операции 33 осуществляется формирование знака операции в целом, который поступает на выходной регистр знака результата 35. Мантисса результата операции поступает на выходной регистр мантиссы результата 36.

Устройство предсказания исключительной ситуации «потеря точности» блока операции «умножение с накоплением», включающее подблок предсказания суммы мантисс, счетчик старших нулей суммы мантисс, отличающееся тем, что оно снабжено входными регистрами мантисс чисел В и С, входными регистрами экспонент чисел А, В и С, счетчиком младших нулей мантиссы слагаемого, подблоком вычисления сдвига выравнивания и предсказания сдвига предварительной нормализации, компаратором ранней потери точности, счетчиком младших нулей суммы мантисс, компаратором поздней потери точности, при этом счетчик младших нулей мантиссы слагаемого связан с входным регистром мантиссы числа С для осуществления подсчета числа младших нулей мантиссы слагаемого С и компаратором ранней потери точности для сравнения со сдвигом выравнивания, выходящим из подблока вычисления сдвига выравнивания и предсказания сдвига предварительной нормализации, связанного с входным регистром экспоненты числа А, входным регистром экспоненты числа В и входным регистром экспоненты числа С для получения признака наличия значащих битов выравненной мантиссы слагаемого за пределами разрядности внутреннего представления данных, а компаратор поздней потери точности связан со счетчиком старших нулей суммы мантисс и счетчиком младших нулей суммы мантисс, которые связаны с подблоком предсказания суммы мантисс для получения признака наличия значащих битов мантиссы результата, в отбрасываемой при округлении части.