Устройство шифрования данных по стандарту гост 28147-89

Иллюстрации

Показать всеИзобретение относится к шифровальным устройствам на основе стандарта шифрования данных. Техническим результатом является повышение тактовой частоты устройства шифрования данных. Устройство раунда, реализующее последовательность действий для каждого раунда шифрования данных, содержит блок суммирования CM1, блок подстановки K, блок сдвига R, дополнительный регистр PREG. С учетом использования дополнительного регистра максимальная тактовая частота в схеме прохождения данных определяется максимальной задержкой в блоке CM1 и в блоках S и R. 3 ил.

Реферат

Область техники

Настоящее изобретение относится к шифровальным устройствам на основе стандарта шифрования данных, более конкретно к шифрованию данных по стандарту ГОСТ 28147-89.

Уровень техники

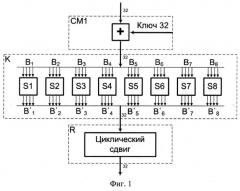

В настоящее время в России действующим стандартом шифрования является ГОСТ 28147-89. Шифрация/дешифрация данных в стандарте ГОСТ 28147-89 осуществляется за 32 однотипных цикла (раунда), в ходе каждого из которых необходимо выполнить определенную последовательность действий, определяемых стандартом. Последовательность действий согласно стандарту определяется функцией преобразования f(x, ki). Перед тем как подвергнуться преобразованиям функцией f, входные данные размером 64 бита разбиваются на два равных фрагмента N1 и N2 по 32 бита каждый. Вычисление значения функции f производится в три этапа. На первом этапе ее 32-битовый аргумент х, входом которого является N1, складывается с подключом ki по модулю 232. Далее данные, поступая на блок подстановки S, разбиваются на восемь последовательных 4-битовых вектора, каждый из которых преобразуется в некоторый 4-битовый вектор соответствующим узлом замены Sj, j=1, …, 8. Каждый узел замены можно представить в виде таблицы-перестановки шестнадцати чисел от 0 до 15, представленных в виде двоичных векторов длины 4. Восемь преобразованных S-блоками векторов последовательно соединяются в 32-битовый вектор S(x). На втором этапе с помощью регистра сдвига R производится циклический сдвиг вектора S(x) влево на 11 позиций. Далее, перед тем как перейти к следующей итерации, производится сложение полученных данных и N2 по модулю 2. Полученный результат записывается в N1, а старое заполнение N1 записывается в N2.

Однако стандарт, введенный в 1990-м году, по сравнению со своим главным конкурентом AES не способен работать на высоких тактовых частотах, что объясняется сложностью операций преобразования данных в одном раунде, порождающих большую задержку в комбинационной части и, как следствие, низкую тактовую частоту устройства в целом.

Целью настоящего изобретения является разработка аппаратной реализации шифрования данных по стандарту ГОСТ 28147-89, которая будет способна работать на тех же тактовых частотах, что и современные высокопроизводительные процессорные ядра.

Сущность изобретения

Техническим результатом предлагаемого изобретения является увеличение тактовой частоты схемы шифрования по стандарту ГОСТ 28147-89.

Устройство шифрования данных состоит из устройства раунда, регистровой памяти и устройства управления. Устройство раунда, реализующее последовательность действий для каждого раунда шифрования данных по стандарту ГОСТ 28147-89, содержит блок суммирования, блок подстановки, блок сдвига и дополнительный регистр. Регистровая память состоит из блока хранения данных, блока хранения ключа и блока хранения S-блоков. Блок хранения данных соединен с первым входом блока суммирования. Блок хранения ключа соединен со вторым входом блока суммирования. Выход блока суммирования подключен ко входу дополнительного регистра, выход которого подключен к первому входу блока подстановки. Ко второму входу блока подстановки подключен выход блока хранения S-блоков. Выход блока подстановки подключен ко входу блока сдвига. Выход блока сдвига подключен ко входу блока хранения данных. Тактовые сигналы подаются на блок хранения данных и дополнительный регистр.

Использование предлагаемого устройства раунда, содержащего дополнительный регистр, подключенный после блока суммирования, позволит увеличить тактовую частоту и согласовать работу устройства шифрования с быстродействующим процессорным ядром.

Краткое описание чертежей

На фиг.1 представлена примерная последовательность действий для каждого раунда по стандарту ГОСТ 28147-89.

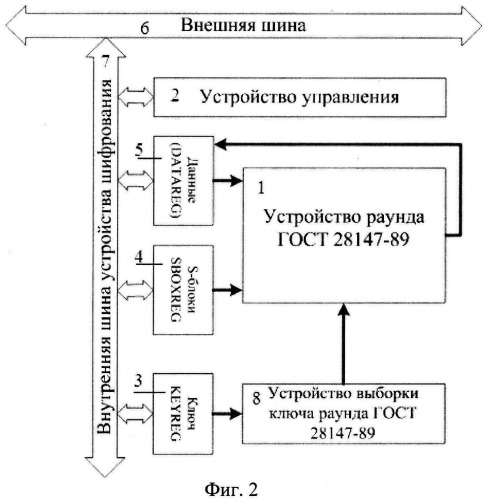

На фиг.2 представлена схема аппаратной реализации шифрования данных по стандарту ГОСТ 28147-89.

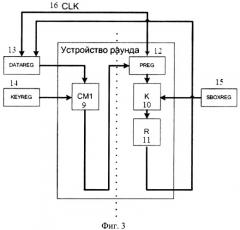

На фиг.3 представлена схема двухтактной реализации устройства раунда с установкой дополнительного регистра после операции сложения.

Подробное описание изобретения

Устройство шифрования данных (фиг.2) содержит устройство раунда 1 (устройство, реализующее последовательность действий для каждого раунда шифрования данных по стандарту ГОСТ 28147-89), регистровую память для хранения различной информации, а также устройство управления 2, которое управляет всеми процессами устройства шифрования данных. Ключ 3, S-блоки 4 и данные для шифрации 5 с указанием адреса размещения подаются в устройство шифрования по внешней шине 6. Устройство управления 2 размещает входные данные по соответствующим им регистрам. Данные хранятся в блоке хранения данных DATAREG размером 64 бит. Ключ 3 хранится в блоке хранения ключа KEYREG размером 256 бит, блоки подстановки хранятся в блоке хранения S-блоков SBOXREG размером 512 бит. Таким же образом осуществляется пересылка служебной информации, такой как режим шифрации, и команда «старт», которая свидетельствует о том, что все данные загружены и можно начинать шифрацию входных данных. После команды «старт» данные из DATAREG делятся на два фрагмента N1 и N2 по 32 бита каждый. Данные фрагмента N1 по внутренней шине 7 попадают на устройство раунда и последовательно проходят стадии суммирования, подстановки, сдвига и возврата в блок данных. Также на устройство раунда подается 32-битный фрагмент ключа, который перед каждым раундом выбирается из KEYREG с помощью устройства выборки ключа раунда 8, и подаются данные для подстановки из SBOXREG. Перед сохранением в блоке DATAREG производится сложение N1 и N2 по модулю 2. Полученный результат записывается в N1, а старое заполнение N1 записывается в N2. Максимальная тактовая частота определяется суммой задержек данных в каждом блоке устройства раунда (суммирование, подстановка, сдвиг) и в ряде случаев является недопустимо низкой.

Устройство раунда (фиг.3) содержит блок суммирования СМ1 9, блок подстановки K 10, блок сдвига R 11 и дополнительный регистр PREG 12. Выход блока хранения данных DATAREG 13 соединен с первым входом блока суммирования СМ1 9. Из блока хранения данных DATAREG 13 в блок суммирования СМ1 9 поступает N1. Выход блока хранения ключа KEYREG 14 соединен со вторым входом блока суммирования СМ1 9. Из блока хранения ключа KEYREG 14 в блок суммирования СМ1 9 поступает первый 32-битный фрагмент ключа, который выбирается посредством устройства управления 2. Выход блока суммирования СМ1 9 подключен к первому входу блока подстановки К 10 через дополнительный регистр PREG 12 размером 32 бита, в котором данные запоминаются до следующего такта. Ко второму входу блока подстановки К 10 подключен выход блока хранения S-блоков SBOXREG 15. Выход блока подстановки K 10 подключен к входу блока сдвига R 11.

Выход блока сдвига R 11 подключен к входу блока хранения данных DATAREG 13. На блок данных DATAREG 13 и дополнительный регистр PREG 12 подаются тактовые сигналы CLK 16. Таким образом, с учетом использования дополнительного регистра максимальная тактовая частота в схеме прохождения данных определяется максимальной задержкой в блоке СМ1 9 и в блоках K 10 и R 11.

Пусть время выполнения каждого блока соответствует T1, T2 и T3. Таким образом, тактовая частота устройства раунда без использования дополнительного регистра равна F=1/(T1+T2+T3). Использование дополнительного регистра после блока суммирования СМ1 позволит увеличить тактовую частоту до величины F=min(1/T1, 1/T2+T3), что в свою очередь значительно увеличит скорость шифрования данных.

Устройство раунда, реализующее последовательность действий для каждого раунда шифрования данных по стандарту ГОСТ 28147-89, содержащее: блок суммирования, блок подстановки, блок сдвига, дополнительный регистр; причем первый вход блока суммирования соединен с выходом блока хранения данных, второй вход блока суммирования соединен с выходом блока хранения ключа, выход блока суммирования подключен к первому входу дополнительного регистра, выход которого подключен к первому входу блока подстановки, ко второму входу блока подстановки подключен выход блока хранения S-блоков, выход блока подстановки подключен ко входу блока сдвига, выход которого подключен к первому входу блока хранения данных; тактовые сигналы подаются на блок хранения данных и дополнительный регистр.