Полупроводниковое устройство

Иллюстрации

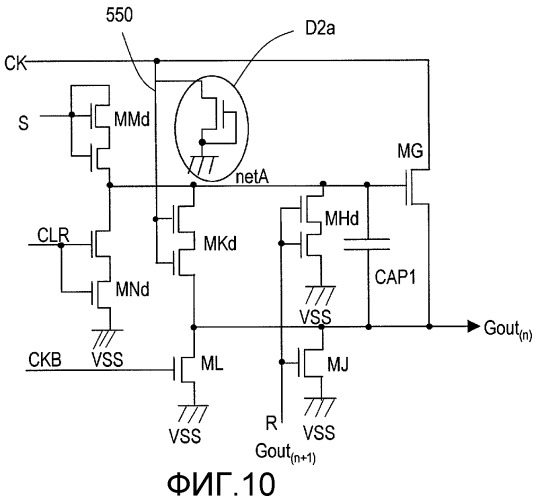

Показать всеИзобретение относится к полупроводниковым устройствам. Полупроводниковое устройство содержит схему, включающую в себя множество тонкопленочных транзисторов и по меньшей мере один диод, при этом множество тонкопленочных транзисторов имеют одинаковый тип проводимости. Когда тип проводимости множества тонкопленочных транзисторов является N-типом, электрод катодной стороны диода присоединяется к линии, присоединенной к затвору выбранного одного из множества тонкопленочных транзисторов, а когда тип проводимости множества тонкопленочных транзисторов является P-типом, электрод анодной стороны диода присоединяется к линии, присоединенной к затвору выбранного одного из множества тонкопленочных транзисторов. Устройство содержит и другой диод, не сформированный на линии, скомпонованный так, что направление протекания тока через него было противоположно по меньшей мере одному диоду. Схема включает сдвиговый регистр, включающий множество каскадов. Каждый из множества каскадов включает в себя первый транзистор для выдачи выходного сигнала и множество вторых транзисторов, чья область истока или область стока электрически присоединена к электроду затвора первого транзистора. Изобретение позволяет исключить повреждение тонкопленочных транзисторов от электростатического разряда в схеме с уменьшенным размером. 7 з.п. ф-лы, 36 ил., 1 табл.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к полупроводниковому устройству, включающему в себя множество тонкопленочных транзисторов и защитных диодов ESD (от электростатического разряда).

УРОВЕНЬ ТЕХНИКИ

В последние годы, становятся широко распространенными жидкокристаллические устройства отображения и органические электролюминесцентные (EL) устройства отображения, которые включают в себя тонкопленочный транзистор (в дальнейшем, «TFT») для каждого пикселя. TFT изготавливаются посредством использования полупроводникового слоя, сформированного на подложке, такой как стеклянная подложка. Подложка, на которой сформированы TFT, указывается ссылкой как подложка активной матрицы.

Традиционно, TFT, использующие пленку аморфного кремния в качестве активного слоя (в дальнейшем, «TFT на аморфном кремнии») и TFT, использующие пленку поликристаллического кремния в качестве активного слоя (в дальнейшем, «TFT на поликристаллическом кремнии»), широко используются в качестве TFT.

Поскольку подвижность носителей пленки поликристаллического кремния более высока, чем у пленки аморфного кремния, TFT на поликристаллическом кремнии имеет более высокий ток включенного состояния, чем TFT на аморфном кремнии, и способен к работе с большим быстродействием. Ввиду этого, были сконструированы панели отображения, в которых не только TFT для пикселей, но также некоторые или все их TFT для периферийных схем, таких как формирователи, сформированы TFT на поликристаллическом кремнии. Формирователи, сформированные таким образом на изолирующей подложке (типично, стеклянной подложке), формирующей панель отображения, могут называться монолитными формирователями. Формирователи включают в себя затворный формирователь и истоковый формирователь, и только один из таковых может быть монолитным формирователем. В материалах настоящей заявки, панель отображения указывает ссылкой на часть жидкокристаллического устройства отображения или органического электролюминесцентного устройства отображения, включающего в себя участок отображения, и не включает в себя подсветку, обрамление, или тому подобное, жидкокристаллического устройства отображения.

Изготовление TFT на поликристаллическом кремнии требует сложных технологических процессов, таких как технологический процесс термического отжига или технологический процесс ионного легирования, а также технологический процесс лазерной кристаллизации для кристаллизации пленки аморфного кремния. Таким образом, в настоящее время, TFT на поликристаллическом кремнии, главным образом, используются в средних и малых устройствах отображения, и TFT на аморфном кремнии используются в больших устройствах отображения.

В последние годы, с ростом потребности в повышении качества изображения и снижения потребляемой мощности в дополнение к увеличению размера устройств отображения, были сделаны предложения (Патентный документ № 1, Патентный документ № 2 и Непатентный документ № 1) TFT, использующие пленку микрокристаллического кремния (µc-Si) в качестве активного слоя, который имеет более высокие рабочие характеристики и более низкие производственные затраты чем TFT на аморфном кремнии. Такой TFT называется «TFT на микрокристаллическом кремнии».

Пленка микрокристаллического кремния является пленкой кремния, имеющей микрокристаллические частицы в ней, и границы зерен микрокристаллических частиц, в основном, находятся в аморфной фазе. То есть, она является смешанным состоянием между кристаллической фазой микрокристаллических частиц и аморфной фазой. Размер каждой микрокристаллической частицы является меньшим, чем у каждой кристаллической частицы, включенной в пленку поликристаллического кремния. В пленке микрокристаллического кремния, каждая микрокристаллическая частица, например, имеет столбчатую форму, растущую из поверхности подложки.

Были предложены TFT, которые используют металл-оксид-полупроводник, такой как полупроводниковую пленку Zn-O (ZnO) или полупроводниковую пленку In-Ga-Zn-O (IGZO), в качестве нового материала для замены кремния. Патентный документ № 3 устанавливает, что можно, с использованием полупроводникового слоя ZnO, получать TFT, имеющий отношение токов включенного состояния/выключенного состояния (ON/OFF) 4,5×105, подвижность около 150 см2/Вс, и пороговое значение около 1,3 В. Эта подвижность является гораздо большей, чем у TFT на аморфном кремнии. Непатентный документ №2 устанавливает, что, используя полупроводниковый слой IGZO, можно получать TFT, имеющий подвижность приблизительно от 5,6 до 8,0 см2/Вс и пороговое значение приблизительно от -6,6 до -9,9 V. Подобным образом подвижность является гораздо большей, чем у TFT на аморфном кремнии.

Таким образом, с большими устройствами отображения, есть случаи, в которых некоторые или все из TFT для периферийной схемы, такой как формирователь, формируются на подложке активной матрицы в дополнение к TFT для пикселей с использованием аморфного кремния, микрокристаллического кремния, IGZO, и т.д.

С другой стороны, схема защиты от ESD (электростатического разряда) нормально предусмотрена на подложке активной матрицы для предотвращения электростатического повреждения в отношении элементов, линий, и т.д.

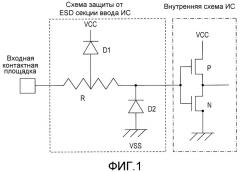

Фиг.1 - схема, показывающая пример схемы защиты от ESD, предусмотренной для внутренней схемы IC, имеющей CMOS (комплементарные элементы металл-оксид-полупроводник). Схема защиты от ESD, показанная на фиг.1, включает в себя защитный резистор R, сформированный между входным выводом CMOS, и два защитных диода D1 и D2 противоположных полярностей. Защитные диоды D1 и D2 оба присоединены к входной сигнальной линии CMOS.

Со схемой защиты от ESD, когда бросок напряжения ESD проникает на входной вывод, потенциал входного вывода увеличивается (+) или уменьшается (-). Если он увеличивается (+), защитный диод D1 включается, тем самым, шунтируя положительный заряд на линию VCC. Если он уменьшается (-), защитный диод D2 включается, тем самым, шунтируя положительный заряд на линию VSS. Величина электрического тока ограничивается защитным резистором R.

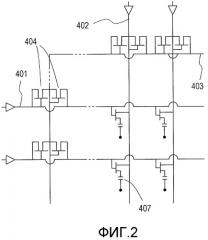

Патентный документ № 4 раскрывает подложку активной матрицы, включающую в себя множество затворных линий 401 и множество стоковых линий 402, пересекающих друг друга, с пиксельным тонкопленочным транзистором 407, предусмотренным на каждом пересечении, как показано на фиг.2, при этом, защитные диоды 404 от ESD предусмотрены между линией 403 опорного потенциала, на которую выдается опорный потенциал, и затворными линиями 401, и между линией 403 опорного потенциала и стоковыми линиями 402. Два диода 404 сформированы посредством использования одной и той же полупроводниковой пленки в качестве полупроводникового слоя пиксельного тонкопленочного транзистора 407 и имеют структуру, в которой исток и затвор TFT закорочены друг на друга. Диоды, имеющие такую структуру также указываются ссылкой как «диоды типа TFT». Электрод затвора одного из двух диодов 404 присоединен к затворной линии 401, а электрод затвора другого присоединен к линии 403 опорного потенциала. Поэтому, заряжается ли затворная 401 положительно или отрицательно по отношению к линии 403 опорного потенциала, можно обеспечивать электрический ток между затворной линией 401 и линией 403 опорного потенциала в таком направлении, чтобы нейтрализовать заряд. Поэтому, можно подавлять напряжение между затворной линией и линией стока, вызванное ESD, и предохранять тонкопленочный транзистор 407 от повреждения броском напряжения ESD.

Несмотря на то, что фиг.2 показывает диоды 404 типа TFT для защиты пиксельных тонкопленочных транзисторов 407, подобные диоды типа TFT могут использоваться для тонкопленочных транзисторов защитной схемы, например, используемых в схемах, таких как схемы формирователя.

СПИСОК ПРОТИВОПОСТАВЛЕННЫХ МАТЕРИАЛОВ

ПАТЕНТНАЯ ЛИТЕРАТУРА

Патентный документ № 1: Публикация № 6-196701 выложенного патента Японии

Патентный документ № 2: Публикация № 5-304171 выложенного патента Японии

Патентный документ № 3: Публикация № 2002-76356 выложенного патента Японии

Патентный документ № 4: Публикация № 63-220289 выложенного патента Японии

НЕПАТЕНТНАЯ ЛИТЕРАТУРА

Непатентный документ № 1: Zhongyang Xu, et al., «A Novel Thin-film Transistors With (mu)c-Si/a-Si Dual Active Layer Structure For AM-LCD» IDW'96 Proceedings of The Third International Display Workshops VOLUME 1, 1996, p.117-120 (Жонгянг Ксу, и другие, «Новейшие тонкопленочные транзисторы с двухслойной структурой активного слоя µc-Si/a-Si», Протоколы IDW'96 третьего международного симпозиума по устройствам отображения, том 1, 1996, стр. 117-120)

Непатентный документ № 2: Je-hun Lee, et al., «World's Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT», SID 08 DIGEST (USA), Society for Information Display, 2008, Volume 39, Issue 1, pp. 625-628 (Джи-хун Ли и другие, «Самая большая в мире (15-дюймовая) панель AMLCD XGA, использующая оксидные TFT IGZO», SID 08 DIGEST (США), Общество по отображению информации, 2008, том 39, вопрос 1, стр. 625-628)

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ПРОБЛЕМА

Как может быть видно из примера, показанного на фиг.1 и 2, схема защиты от ESD включает в себя по меньшей мере два диода, так что, заряжается ли линия, которая должна быть защищена, положительным зарядом или отрицательным зарядом, заряд может шунтироваться. Таким образом, есть проблема, что возрастает размер схемы.

Более точно, в тех случаях, когда диоды типа TFT, использующие полупроводниковую пленку, такую как пленка аморфного кремния, которая обладает относительно низкой подвижностью, используются в качестве защитных диодов от ESD, необходимо увеличивать ширину W канала диодов типа TFT, тем самым, дополнительно увеличивая размер защитного диода от ESD и, как результат, увеличивая участок обрамления устройства отображения.

Когда пытаются применять схему защиты от ESD к схеме сдвигового регистра, которая не имеет линий VDD, необходимо прокладывать трассы новой линии VDD снаружи, тем самым, дополнительно увеличивая размер схемы.

Настоящее изобретение было сделано ввиду проблем, описанных выше, и его цель состоит в том, чтобы предложить полупроводниковое устройство, включающее в себя множество тонкопленочных транзисторов и схему защиты от ESD для защиты тонкопленочных транзисторов от ESD, с размером схемы, уменьшенным от такового у традиционных технологий, наряду со сдерживанием повреждения тонкопленочных транзисторов, обусловленного ESD.

РЕШЕНИЕ ДЛЯ ПРОБЛЕМЫ

Полупроводниковое устройство по настоящему изобретению является полупроводниковым устройством, включающим в себя схему, включающую в себя множество тонкопленочных транзисторов и по меньшей мере один диод, при этом: множество тонкопленочных транзисторов имеют одинаковый тип проводимости; когда тип проводимости множества тонкопленочных транзисторов является N-типом, электрод катодной стороны по меньшей мере одного диода присоединяется к линии, присоединенной к затвору выбранного одного из множества тонкопленочных транзисторов; когда тип проводимости множества тонкопленочных транзисторов является P-типом, электрод анодной стороны по меньшей мере одного диода присоединяется к линии, присоединенной к затвору выбранного одного из множества тонкопленочных транзисторов; и другой диод, скомпонованный так, чтобы его направление протекания тока было противоположно по меньшей мере одному диоду, не сформирован на линии.

В предпочтительном варианте осуществления, пиковое значение напряжения схемы имеет значение 20 В или более.

Предпочтительно, чтобы полупроводниковые слои по меньшей мере одного тонкопленочного диода и выбранного одного из тонкопленочных транзисторов были сформированы из одной и той же полупроводниковой пленки.

Одна и та же полупроводниковая пленка может быть пленкой микрокристаллического кремния.

Схема может включать в себя регистр.

В предпочтительном варианте осуществления, сдвиговый регистр включает в себя множество каскадов, каждый последовательно выдает выходные сигналы; каждый из множества каскадов включает в себя первый транзистор для выдачи выходного сигнала и множество вторых транзисторов, чья область истока и область стока электрически присоединена к электроду затвора первого транзистора; и множество вторых транзисторов включает в себя многоканальный транзистор, имеющий активный слой, включающий в себя по меньшей мере две канальных области, область истока и область стока.

По меньшей мере один диод может включать в себя: электрод затвора, сформированный на подложке; слой изоляции затвора, сформированный на электроде затвора; по меньшей мере один полупроводниковый слой, сформированный на слое изоляции затвора и имеющий первую область и вторую область; первый электрод, предусмотренный в первой области и электрически присоединенный к первой области и электроду затвора; и второй электрод, предусмотренный во второй области и электрически присоединенный ко второй области.

По меньшей мере один полупроводниковый слой может включать в себя канальную область, перекрывающуюся с электродом затвора, со слоем изоляции затвора, вставленным между ними, и резистивную область, не перекрывающуюся с электродом затвора, со слоем изоляции затвора, вставленным между ними; и путь тока, включающий в себя канальную область и резистивную область, может быть сформирован между первым электродом и вторым электродом, в то время как диод находится во включенном состоянии.

ПОЛЕЗНЫЕ РЕЗУЛЬТАТЫ ИЗОБРЕТЕНИЯ

Согласно настоящему изобретению, в полупроводниковом устройстве, включающем в себя схему одноканальных TFT, можно подавлять рост утечки отключенного состояния TFT вследствие ESD наряду с подавлением увеличения размера схемы. Поэтому, можно предотвращать некорректную работу схемы.

Особенно эффективным является применение настоящего изобретения к подложке активной матрицы, которая включает в себя схему возбуждения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - схема, показывающая пример традиционной схемы защиты от ESD, предусмотренной во внутренней схеме ИС.

Фиг.2 - схема, показывающая традиционную подложку активной матрицы, имеющую схему защиты от ESD.

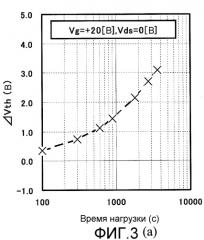

Фиг.3(a) и (b) - графики, показывающие результаты нагрузочных испытаний по зарядке затвора N-канального TFT на аморфном кремнии положительным зарядом (Vg=20 В) и результаты нагрузочных испытаний по зарядке затвора отрицательным напряжением (Vg=-20 В), соответственно.

Фиг.4 - график, показывающий характеристики тока (Id) - напряжения (Vg) TFT на аморфном кремнии.

Фиг.5(a) и (b) - схемы, каждая иллюстрирует участок схемы 520 в первом варианте осуществления настоящего изобретения.

Фиг.6 - схематический вид в поперечном разрезе, показывающий защитный диод по первому варианту осуществления настоящего изобретения.

Фиг.7 - график, иллюстрирующий характеристики защитного диода D2 по первому варианту осуществления настоящего изобретения.

Фиг.8(a) - схематический вид сверху жидкокристаллической панели 600 отображения по варианту осуществления настоящего изобретения, а (b) - вид сверху, показывающий схематическую структуру одного пикселя.

Фиг.9 - структурная схема, иллюстрирующая структуру сдвигового регистра 610B, включенного в затворный формирователь 610.

Фиг.10 - принципиальная схема одного каскада сдвигового регистра по варианту осуществления настоящего изобретения, который используется в одном из каскадов сдвигового регистра 610B.

Фиг.11 - схема, показывающая формы сигналов входных/выходных сигналов на разных каскадах сдвигового регистра 610B и форму сигнала напряжения netA.

Фиг.12 - схема, показывающая формы сигналов выходных сигналов из пяти каскадов с n-2 по n+2 сдвигового регистра 610B.

Фиг.13 - принципиальная электрическая схема, показывающая один из каскадов сдвигового регистра по справочному примеру.

Фиг.14 - принципиальная схема, показывающая один каскад сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

Фиг.15 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

Фиг.16 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

Фиг.17 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

Фиг.18 - принципиальная электрическая схема, показывающая один каскад еще одного другого сдвигового регистра по варианту осуществления настоящего изобретения, используемый в одном из каскадов сдвигового регистра 610B.

Фиг.19(a) и (b) - схемы, схематически показывающие полупроводниковое устройство по первому варианту осуществления настоящего изобретения, при этом, (a) - его вид сверху, и (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

Фиг.20 - блок-схема последовательности операций способа, показывающая пример способа для изготовления полупроводникового устройства, показанного на фиг.19.

Фиг.21(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

Фиг.22(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

Фиг.23(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

Фиг.21(a) и (b)- схемы, иллюстрирующие этап для изготовления полупроводникового устройства, показанного на фиг.19, при этом, (a) - вид сверху, а (b) - вид в поперечном разрезе, взятый вдоль линии A-A' и линии B-B' по (a).

Фиг.25(a) - вид сверху, схематически показывающий еще один другой диод по первому варианту осуществления настоящего изобретения, а (b) - вид в поперечном разрезе, взятый вдоль линии E-E' по (a).

Фиг.25(a) - вид сверху, схематически показывающий еще один другой диод по первому варианту осуществления настоящего изобретения, а (b) - вид в поперечном разрезе, взятый вдоль линии F-F' по (a).

Фиг.27 - схематический вид в поперечном разрезе, показывающий еще одно другое полупроводниковое устройство по первому варианту осуществления настоящего изобретения.

Фиг.28 - схематический вид сверху, показывающий тонкопленочный транзистор 710 по первому варианту осуществления настоящего изобретения, (b) - схематический вид в поперечном разрезе, взятый вдоль линии 28B-28B' по (a), а (c) - эквивалентная принципиальная электрическая схема тонкопленочного транзистора 710.

Фиг.29(a) - схематический вид сверху, показывающий еще один тонкопленочный транзистор 790, имеющий структуру с двумя затворами, а (b) - схематический вид в поперечном разрезе, взятый вдоль линии 29B- 29B' по (a).

Фиг.30 - график, показывающий пример характеристик тока отключенного состояния тонкопленочного транзистора 710 и тонкопленочного транзистора 790.

Фиг.31 - график, показывающий зависимость напряжения Vg (В) затвора и тока Ids (А) исток-сток для TFT, имеющих одноканальную структуру, двухканальную структуру и трехканальную структуру.

Фиг.32 (a)-(f) - схематические виды в поперечном разрезе, иллюстрирующие способ для изготовления подложки 801 активной матрицы, включающей в себя тонкопленочный транзистор 710.

Фиг.33(a) - схематический вид с верху, показывающий тонкопленочный транзистор 710A по варианту осуществления настоящего изобретения, а (b) - схематический вид сверху, показывающий тонкопленочный транзистор 710B по варианту осуществления настоящего изобретения.

Фиг.34 - график, показывающий зависимость между напряжением Vg (В) затвора и током Ids (А) исток-сток для тонкопленочного транзистора 710A и тонкопленочного транзистора 710B.

Фиг.35(a) - схематический вид с верху, показывающий тонкопленочный транзистор 710C по варианту осуществления настоящего изобретения, (b) - схематический вид сверху, показывающий тонкопленочный транзистор 710D по варианту осуществления настоящего изобретения, а (c) - схематический вид сверху, показывающий тонкопленочный транзистор 710E по варианту осуществления настоящего изобретения.

Фиг.36(a) - схематический вид с верху, показывающий тонкопленочный транзистор 710F по варианту осуществления настоящего изобретения, (b) - схематический вид сверху, показывающий тонкопленочный транзистор 710G по варианту осуществления настоящего изобретения, а (c) - схематический вид сверху, показывающий тонкопленочный транзистор 710H по варианту осуществления настоящего изобретения.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Полупроводниковое устройство по настоящему изобретению имеет схему, включающую в себя множество тонкопленочных транзисторов и по меньшей мере один диод. Тонкопленочные транзисторы, включенные в схему по настоящему изобретению все имеют одинаковый тип проводимости (все являются P-канальными TFT или все являются N-канальными TFT). В настоящем описании изобретения, такая схема указывается ссылкой как «схема, сформированная одноканальными TFT».

В настоящем изобретении, если тип проводимости множества тонкопленочных транзисторов, имеющих одинаковый тип проводимости, является N-типом, электрод катодной стороны по меньшей мере одного диода присоединяется к линии, которая присоединена к затвору одного из множества тонкопленочных транзисторов. Если тип проводимости множества тонкопленочных транзисторов является P-типом, электрод анодной стороны по меньшей мере одного диода присоединяется к линии, которая присоединена к затвору одного из множества тонкопленочных транзисторов. Другой диод, скомпонованный так, чтобы его направление протекания тока было противоположно по меньшей мере одному диоду, не сформирован на линии.

Настоящее изобретение широко применимо к схемам возбуждения и подложкам активной матрицы устройств отображения, или устройствам отображения, использующим таковые. Например, для относительно большого устройства отображения, такого как тонкий телевизор ЖКД (с жидкокристаллическим дисплеем), предпочтительно, чтобы полупроводниковая пленка, имеющая более низкую подвижность, чем поликремний, такая как пленка аморфного кремния, пленка микрокристаллического кремния и пленка IGZO, используется не только для пиксельных TFT, но также схемных TFT, используемых в периферийных схемах, таких как схемы возбуждения, но такие TFT типично являются одноканальными TFT. То есть, они являются N-канальными TFT или P-канальными TFT, и не образуют CMOS.

Далее, со ссылкой на чертежи, будут подробно описаны проблемы, которые должны быть решены настоящим изобретением.

Схема, сформированная одноканальными TFT, имеет проблему, что ток утечки отключенного состояния возрастает, и вероятно должна возникать некорректная работа, по сравнению со схемами, включающими в себя CMOS, используемые в LPS или однокристальных ИС. Причина является следующей. С CMOS, пороговое значение может регулироваться посредством использования этапа легирования. В противоположность, нормально, с одноканальным TFT, для того чтобы снижать себестоимость, этап легирования не выполняется, а потому, пороговое значение не может регулироваться. Таким образом, подпороговая область характеристик Id-Vg находится около Vg=0[В], и вероятно, что возникает утечка закрытого состояния.

Настоящие изобретатели провели исследования для обнаружения причины вышеприведенной проблемы и, как результат, обнаружили, что, когда положительный или отрицательный заряд подается на затвор одноканального TFT, пороговое значение TFT смещается в положительном или отрицательном направлении в зависимости от полярности заряда, приложенного к нему. Также было обнаружено, что с N-канальным одноканальным TFT, ток утечки отключенного состояния возрастает, только когда пороговое значение смещается в отрицательном направлении.

Фиг.3(a) и 3(b) - графики, показывающие результаты нагрузочных испытаний, при которых затвор N-канального TFT на аморфном кремнии заряжается положительным зарядом (Vg=20 В), и результаты нагрузочных испытаний, при которых затвор заряжается отрицательным зарядом (Vg=-20 В). При обоих нагрузочных испытаниях, напряжение исток-сток предполагается имеющим значение 0 В. Вертикальная ось графика представляет величину заряда (ΔVth) порогового значения Vth N-канального TFT на аморфном кремнии, а горизонтальная ось представляет время нагрузки. Величина ΔVth порогового значения является значением, полученным вычитанием порогового значения до прикладывания нагрузки из порогового значения после того, как приложена нагрузка, через предопределенный период времени.

Как может быть видно из результатов, показанных на фиг.3(a), когда положительный заряд прикладывается к затвору N-канального TFT на аморфном кремнии, пороговое значение смещается в положительном направлении, тем самым, увеличивая пороговое значение. С другой стороны, как показано на фиг.3(b), когда отрицательный заряд прикладывается к затвору, пороговое значение смещается в отрицательном направлении, тем самым, уменьшая пороговое значение.

Хотя ток утечки отключенного состояния затвора (ток утечки отключенного состояния) не увеличивается, когда пороговое значение TFT смещается в положительном направлении, ток утечки отключенного состояния затвора (ток утечки отключенного состояния) увеличивается, когда оно смещается в отрицательном направлении.

Фиг.4 - график, показывающий характеристики тока (Id) - напряжения (Vg) TFT на аморфном кремнии. Предполагается, что длина L канала TFT на аморфном кремнии имеет значение 4 мкм, ширина W канала имеет значение 24 мкм, напряжение Vd стока имеет значение 10 В, а напряжение VSS истока имеет значение -5 В. Предполагается, что температура измерения является комнатной температурой. По существу, никакого тока Id(off) не протекает, когда затвор находится в отключенном состоянии (Vg=VSS), до того, как смещается пороговое значение, как указано кривой 510. Однако, когда пороговое значение смещается в отрицательном направлении, ток Id(off) отключенного состояния затвора существенно возрастает, как указано кривой 512.

Когда ток Id(off) отключенного состояния затвора возрастает, схема, включающая в себя этот TFT, может работать некорректно. В тех случаях, когда схема по настоящему варианту осуществления является затворным формирователем, может быть возможным, что не выдается никакого сигнала. Наоборот, даже если пороговое значение смещается в положительном направлении, ток Id(off) отключенного состояния затвора не возрастает, и является маловероятным, что возникает некорректная работа схемы, обусловленная утечкой отключенного состояния.

На основании результатов исследования, описанных выше, настоящие изобретатели обнаружили, что в схеме, сформированной одноканальными TFT, TFT необходимо защищаться только от заряда, имеющего такую полярность, которая увеличивает ток утечки отключенного состояния TFT, и не нужно защищаться от заряда, имеющего другую полярность, таким образом, приходя к настоящему изобретению.

То есть, в полупроводниковом устройстве, имеющем схему, включающую в себя N-канальный TFT в качестве одноканального TFT по настоящему изобретению, необходимо формировать защитный диод (диод D2 в схеме защиты по фиг.1) только для подавления зарядки затвора N-канального TFT отрицательным зарядом. С другой стороны, в полупроводниковом устройстве, имеющем схему, включающую в себя P-канальный TFT в качестве одноканального TFT, необходимо формировать защитный диод (диод D1 в схеме защиты по фиг.1) только для подавления зарядки затвора P-канального TFT положительным зарядом. Поэтому, поскольку количество диодов для защиты от ESD может быть уменьшено на 1/2, можно уменьшать размер схемы от традиционных технологий наряду с предотвращением некорректной работы схем, обусловленной ESD. Когда применяется к схеме сдвигового регистра, который не включает в себя линию VDD, больше не нужно прокладывать трассу линии VDD с целью формирования схемы защиты от ESD, можно более эффективно уменьшать размер схемы.

(Первый вариант осуществления)

Первый вариант осуществления полупроводникового устройства по настоящему изобретению далее будет описан со ссылкой на чертежи.

Полупроводниковое устройство по настоящему изобретению имеет схему, включающую в себя множество TFT и защитный диод для защиты по меньшей мере одного из множества TFT от ESD. Множество TFT все являются N-канальными TFT или все являются P-канальными TFT (одноканальная конфигурация). Защитный диод предусмотрен на линии, которая присоединена к затвору TFT, который должен быть защищен.

Фиг.5(a) - схема, иллюстрирующая участок схемы 520 по настоящему варианту осуществления. Схема 520 включает в себя N-канальный тонкопленочный транзистор 522, линию 524, присоединенную к затвору тонкопленочного транзистора 522, линию 526 VDD и схему защиты, включающую в себя защитный диод D2. Защитный диод D2 имеет структуру, в которой, например, исток и затвор TFT закорочены друг на друга, и также указывается ссылкой как «диод типа TFT».

Фиг.6 - схематический вид в поперечном разрезе, иллюстрирующий защитный диод D2. Защитный диод D2 включает в себя электрод 530 затвора, полупроводниковый слой 534, сформированный на электроде 530 затвора, с пленкой 532 изоляции затвора, вставленной между ними, а также первый электрод 536 (электрод истока) и второй электрод 538 (электрод стока), электрически присоединенные к противоположным краям полупроводникового слоя 534. Предполагается, что ток течет с истока на сток. Контактный слой 540 сформирован между полупроводниковым слоем 534 и каждым из первого и второго электродов 536 и 538. Первый электрод 536 присоединен к электроду 530 затвора на контактном отверстии 542. Участок 544 (канальный участок) полупроводникового слоя 534, вставленного между двумя электродами 536 и 538, перекрывается с электродом 530 затвора. В защитном диоде D2, ток течет с первого электрода 536 на второй электрод 538 через канальный участок 544 полупроводникового слоя 534. В настоящем варианте осуществления, первый электрод 536 (анодная сторона) и электрод 530 затвора защитного диода D2 присоединены к линии 526 VSS, показанной на фиг.5(a), а второй электрод 538 (катодная сторона) присоединен к линии 524.

Фиг.5(a) вновь будет подвергнут ссылке. Как описано выше, поскольку тонкопленочный транзистор 522 имеет N-канал, если отрицательный бросок напряжения ESD прикладывается к затвору тонкопленочного транзистора 522, пороговое значение может смещаться в отрицательном направлении, тем самым, повышая утечку отключенного состояния. С этой схемой 520, когда отрицательный бросок напряжения ESD подается на линию 524, бросок напряжения ESD может шунтироваться защитным диодом D2 на линию 526 VSS, тем самым, подавляя увеличение утечки отключенного состояния, обусловленной прикладыванием отрицательного броска напряжения ESD к затвору тонкопленочного транзистора 522.

С другой стороны, когда положительный бросок напряжения ESD подается на линию 524, бросок напряжения ESD прикладывается непосредственно к затвору тонкопленочного диода 522, так как нет схемы защиты для шунтирования положительного заряда. В этом случае, однако, поскольку пороговое значение тонкопленочного транзистора 522 смещается в положительном направлении, утечка отключенного состояния не увеличивается вследствие смещения порогового значения.

Таким образом, с настоящим вариантом осуществления, можно подавлять увеличение утечки отключенного состояния тонкопленочного транзистора 522, обусловленной ESD. Несмотря на то, что два защитных диода разных направлений протекания тока предусмотрены для каждой линии при традиционных технологиях, с настоящим вариантом осуществления можно подавлять рост утечки отключенного состояния тонкопленочного транзистора 522 посредством предоставления одного защитного диода D2 для каждой линии 524, тем самым, уменьшая размер схемы от традиционных технологий.

Фиг.7 - график, иллюстрирующий характеристики защитного диода D2 по настоящему варианту осуществления. Горизонтальная ось графика представляет напряжение Vdiode (В) на защитном диоде D2, а вертикальная ось представляет ток (A), протекающий через защитный диод D2. Напряжение Vdiode выражается в качестве VSS-Vg (Vg: потенциал линии 24). В этом примере предполагается, что ширина W канала защитного диода D2 имеет значение 20 мкм, а длина L канала имеет значение 16 мкм.

Как может быть видно из фиг.7, когда отрицательный заряд подается на линию 524, тем самым, прикладывая положительное напряжение (VSS-Vg>0) защитного диода D2 (прямое смещение), ток протекает с первого электрода на второй электрод защитного диода D2, а потому, можно шунтировать отрицательный заряд с линии 524 на линию 256 VSS.

С другой стороны, если потенциал Vg находится в пределах рабочего диапазона напряжений (VSS≤Vg≤VDD) тонкопленочного транзистора 522, никакой ток не протекает через защитный диод D2, даже если отрицательное напряжение (VSS-Vg<0) прикладывается к защитному диоду D2 (обратное смещение).

Несмотря на то, что ширина W канала и длина L канала защитного диода D2 не ограничены конкретными значениями, типично предпочтительно, чтобы ширина W канала была большой (например, 10 мкм или больше), в каком случае, большая величина заряда может разряжаться, когда подается ESD. Более предпочтительно, ширина W канала имеет значение 20 мкм или большее. Если длина L канала велика (например, 5 мкм или более), велико сопротивление нагрузки, и можно подавлять утечку, возникающую через защитный диод D2 во время нормальной работы. С другой стороны, если ширина W канала и длина L канала слишком велики, это приводит к увеличению размера схемы, а потому, предпочтительно, чтобы ширина W канала имела значение 1000 мкм или меньше, а длина L канала имела значение 50 мкм или меньше.

Схема 520 по настоящему варианту осуществления может включать в себя P-канальный тонкопленочный транзистор вместо N-канального тонкопленочного транзистора 522. В этом случае, схема защиты, присоединенная к затвору P-канального тонкопленочного транзистора, включает в себя защитный диод D1, имеющий структуру, в которой сток и затвор закорочены друг на друга, как показано на фиг.5(b). Электрод катодной стороны (сток) защитного диода D1 присоединен к линии VDD, а электрод анодной стороны (исток) присоединен к линии 524', присоединенной к затвору P-канального тонкопленочного транзистора 522'. Схема защиты не включает в себя никакого диода, скомпонованного, так что его направление протекания тока является противоположным таковому у защитного диода D1. Таким образом, когда положительный бросок напряжения ESD прикладывается к линии 524', бросок напряжения ESD может шунтироваться на линию VDD, а потому, можно предохранять пороговое значение P-канального тонкопленочного транзистора от смещения в положительном направлении.

Схема 520 типично включает в себя множество TFT одинакового типа проводимости и схему защиты от ESD для защиты по меньшей мере одного из множества TFT от ESD. Схема защиты от ESD включает в себя защитный диод D2, который эффективен против ESD той полярности, которая увеличивает утечку в отключенном состоянии TFT, который должен защищаться, и не включает в себя защитный диод D1, который эффективен против ESD противоположной полярности. Схеме по настоящему варианту осуществления требуется включать в себя только по меньшей мере одну схему защиты, описанную выше, и схема защиты, описанная выше, может быть предусмотрена для каждого из двух или более TFT. Может быть TFT, защищенный схемой защиты, включающей в себя два защитных диода D1 и D2.

Настоящий вариант осуществления предпочтительно применяется к полупроводниковому устройству, включающему в себя схему, чьим пиковым значением напряжения является 20 В или более. С таким полупроводниковым устройством, пороговое значение TFT, включенного в схему, смещается на очень большие величины, а потому, можно получать особенно резко выраженный эффект, предусматривая схему защиты, описанную выше.

Схема 520 по настоящему варианту осуществления может быть сдвиговым регистром, который, например, сформирован (изготовленным за одно целое) монолитным с жидкокристаллической панелью отображения. Далее будет описана ко