Корреляционный измеритель временных сдвигов случайных сигналов

Иллюстрации

Показать всеИзобретение относится к специализированным устройствам извлечения информации и служит для измерения временных сдвигов между случайными аналоговыми сигналами. Техническим результатом является структурное упрощение корреляционного измерителя. Корреляционный измеритель содержит входной аналоговый мультиплексор, аналого-цифровой преобразователь, два регистра, перемножитель, цифровой мультиплексор, оперативное запоминающее устройство, сумматор, блок сравнения, блок управления и связи между элементами. 1 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к специализированным устройствам извлечения информации и служит для измерения временных сдвигов между случайными аналоговыми сигналами.

Известен корреляционный измеритель (прототип), содержащий аналого-цифровой преобразователь, регистр, перемножитель, группу накапливающих сумматоров, два демультиплексора, блок поиска экстремума и блок управления, выход регистра соединен с первым входом перемножителя, выход мультиплексора подключен к информационному входу аналого-цифрового преобразователя, выход которого подключен к информационному входу первого демультиплексора, первый выход которого соединен с информационным входом регистра, второй вход перемножителя соединен с вторым выходом первого демультиплексора, выход перемножителя соединен с информационным входом второго демультиплексора, выходы которого соединены с информационными входами накапливающих сумматоров, выходы которых соединены с информационными входами блока поиска экстремума, выход которого является выходом измерителя, информационными входами измерителя являются соответственно первый и второй информационный входы мультиплексора, адресный вход которого объединен с адресным входом первого демультиплексора и подключен к первому адресному выходу блока управления, второй адресный выход которого соединен с адресным входом второго демультиплексора, первый, второй и третий тактовые выходы блока управления соединены с тактовыми входами аналого-цифрового преобразователя, регистра и накапливающих сумматоров соответственно, входы обнуления накапливающих сумматоров объединены с обнуляющим входом блока поиска экстремума и подключены к обнуляющему выходу блока управления, управляющий выход которого соединен с запускающим входом блока поиска экстремума, входами запуска и обнуления корреляционного измерителя являются соответствующие входы блока управления [Пат. RU 2229157. Опубл. 20.05.2004, Бюл. №14].

Измеритель-прототип реализует метод парных некоррелированных выборок и позволяет определять временной сдвиг между случайными аналоговыми сигналами по положению пика их взаимокорреляционной функции. Однако измеритель оказывается сложным в реализации: количество независимых сумматоров-накопителей равно количеству определяемых ординат взаимокорреляционной функции, что сдерживает его применение в ситуациях, когда требуется иметь относительно большой диапазон измеряемых временных сдвигов или высокое разрешение по времени.

Технический результат, достигаемый при использовании настоящего изобретения, заключается в структурном упрощении корреляционного измерителя.

Технический результат достигается тем, что в известный корреляционный измеритель временных сдвигов случайных сигналов, содержащий аналоговый мультиплексор, аналого-цифровой преобразователь, первый регистр, перемножитель и блок управления, выход аналогового мультиплексора подключен к информационному входу аналого-цифрового преобразователя, первый вход перемножителя соединен с выходом первого регистра, информационными входами измерителя являются соответственно первый и второй информационный входы аналогового мультиплексора, адресный вход которого подключен к первому адресному выходу блока управления, первый тактовый выход которого соединен с тактовым входом аналого-цифрового преобразователя, второй тактовый выход блока управления соединен с тактовым входом первого регистра, согласно изобретению введены оперативное запоминающее устройство, второй регистр, сумматор, цифровой мультиплексор и блок сравнения, выход аналого-цифрового преобразователя соединен с информационным входом первого регистра и вторым входом перемножителя, выход которого соединен с первым информационным входом цифрового мультплексора, выход которого соединен с первым входом сумматора, выход которого соединен с информационным входом второго регистра, выход которого соединен с информационным входом оперативного запоминающего устройства, выход которого соединен со вторым входом сумматора, адресный и управляющий вход оперативного запоминающего устройства соединены с соответствующими выходами блока управления, третий тактовый выход которого соединен с тактовым входом второго регистра, вход блока сравнения соединен с выходом сумматора, а выход со входом остановки блока управления, выходом измерителя является второй адресный выход блока управления, адресный вход цифрового мультиплексора соединен с третьим адресным выходом блока управления, второй информационный вход цифрового мультиплексора является входом кода единицы.

Кроме того, технический результат достигается тем, что блок сравнения выполнен на основе компаратора идентичности, один из входов которого выполняет функции информационного, а другой является входом постоянной величины.

Сущность изобретения поясняется функциональными схемами и временными диаграммами.

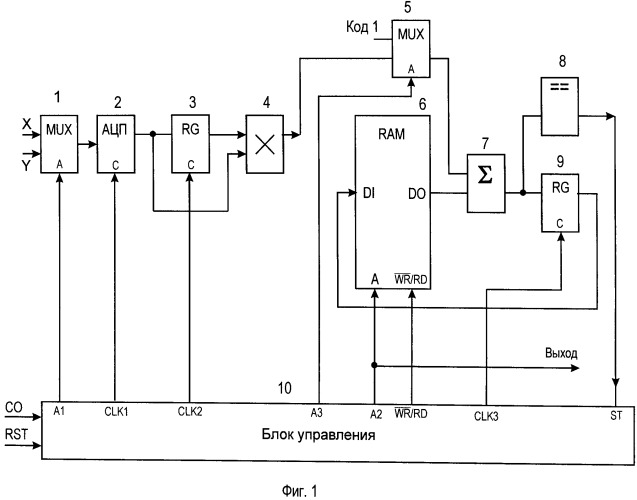

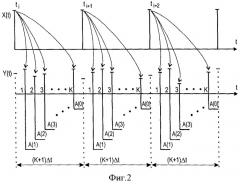

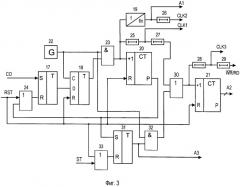

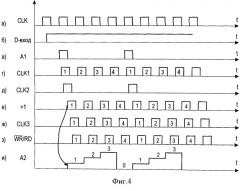

На фиг.1 показана функциональная схема корреляционного измерителя временных сдвигов; на фиг.2 приведены временные диаграммы, поясняющие измерение относительных временных сдвигов методом некоррелированных парных выборок; на фиг.3 - функциональная схема блока 10 управления (пример исполнения); на фиг.4 - временные диаграммы, иллюстрирующие работу блока 10 управления.

Функциональная схема корреляционного измерителя (фиг.1) содержит входной аналоговый мультиплексор 1, аналого-цифровой преобразователь (АЦП) 2, регистры 3, 9, перемножитель 4, цифровой мультиплексор 5, оперативное запоминающее устройство (ОЗУ) 6, сумматор 7, блок 8 сравнения и блок 10 управления. Выход мультиплексора 1 подключен к информационному входу АЦП 2, выход которого подключен к информационному входу регистра 3, выход которого соединен с первым входом перемножителя 4, второй вход которого соединен с выходом АЦП 2, выход перемножителя 4 соединен с первым входом мультплексора 5, выход которого соединен с первым входом сумматора 7, второй вход которого соединен с выходом DO ОЗУ 6, информационный вход DI которого соединен с выходом регистра 9, информационный вход которого соединен с выходом сумматора 7, адресный выход А1 блока 10 управления соединен с адресным входом мультиплексора 1, тактовые входы CLK1, CLK2 и CLK3 блока 10 управления соединены с тактовыми входами АЦП 2, регистра 3 и регистра 9 соответственно, адресный вход А и управляющий вход ОЗУ 6 соединены с выходами А2 и соответственно, адресный выход A3 блока 10 соединен с адресным мультиплексора 5, информационным выходом корреляционного измерителя временных сдвигов является второй адресный выход А2 блока 10, входами управления СО и обнуления RST корреляционного измерителя являются соответствующие входы блока 9 управления, вход блока 8 сравнения соединен с выходом сумматора 7, а выход со входом остановки ST блока 10 управления, второй информационный вход мультиплексора 5 является входом кода единицы.

Временные диаграммы по фиг.2 содержат выборки сигнала x(t) и выборки сигнала y(t), задержанного относительно x(t).

Блок 9 управления по фиг.3 содержит триггеры 17, 18, 31, делитель 19 частоты, счетчики 20 и 21, генератор 22 тактовых импульсов, элемент И 23, 32, элементы ИЛИ 24, 30, 33, элементы 25, 26, 27, 28 и 29 задержки. Вход установки в единицу триггера 17 является запускающим входом блока 9 управления, выход триггера 17 соединен с D-входом триггера 18, выход которого соединен с первым входом элемента И 23, второй вход которого объединен с тактовым входом триггера 18 и подключен к выходу генератора 22, входы делителя 19 и элемента 25 задержки объединены с суммирующим входом счетчика 20 и подключены к выходу элемента И 23, суммирующий вход счетчика 21 соединен с выходом элемента 2ИЛИ 30, первый вход которого через элемент 27 задержки подключен к выходу элемента 25 задержки, выход которого является первым тактовым выходом CLK1 блока 9 управления, вторым тактовым выходом CLK2 которого является выход элемента 26 задержки, вход которого соединен с выходом делителя 19 частоты, выход которого является первым адресным выходом А1 блока 9, третьим тактовым выходом CLK3 которого является выход элемента 28 задержки, вход которого соединен с выходом элемента 27 задержки, выходом блока 9 является выход элемента 29 задержки, вход которого соединен с выходом элемента 28, обнуляющие входы триггера 18, счетчиков 20, 21 объединены с первым входом элемента ИЛИ 24 и служат обнуляющим входом RST блока 9 управления, обнуляющий вход триггера 31 соединен с выходом элемента 2ИЛИ 33, первый вход которого объединен со входом RST блока 9, а второй вход является входом остановки ST блока 10, выход переполнения счетчика 20 соединен со вторым входом элемента ИЛИ 24 и с входом установки в единицу триггера 31, вторым адресным выходом А3 блока 9 является информационный выход счетчика 21, третьим адресным выходом A3 блока 9 является выход триггера 31, выход элемента ИЛИ 24 соединен с обнуляющим входом триггера 17, выход триггера 31 соединен с первым входом элемента 2И 32, выход которого соединен со вторым входом элемента 2ИЛИ 30, второй вход элемента 2И 32 соединен с выходом генератора 22 тактовых импульсов.

Временные диаграммы по фиг.4 содержат: тактовые импульсы CLK (фиг.4, а) на выходе генератора 22, логический уровень (фиг.4, б) на D-входе триггера 18, адресные импульсы А1 (фиг.4, в) на первом адресном выходе блока 9; тактовые импульсы CLK1 (фиг.4, г) на первом тактовом выходе блока 9; тактовые импульсы CLK2 (фиг.4, д) на втором тактовом выходе блока 9; тактовые импульсы «+1» (фиг.4, е) на суммирующем входе счетчика 21; тактовые импульсы CLK3 (фиг.4, ж) на третьем тактовом выходе блока 9; импульсы управления записью/чтением на выходе блока 9 (фиг.4, з); текущий адресный код А2 (фиг.4, и) на втором адресном выходе блока 9.

Заявляемый корреляционный измеритель времени задержки служит для обработки центрированных, стационарных и эргодичных случайных процессов x(t) и y(t). В основе функционирования измерителя лежит метод измерения функции корреляции некоррелированными парными выборками. Временной сдвиг τ между сигналами x(t) и y(t) определяют по положению пика их взаимокорреляционной функции R(τ).

Корреляционный измеритель (фиг.1) работает следующим образом. Через входной аналоговый мультиплексор 1 на вход АЦП 2 поступают сигналы x(t) и y(t), при этом мультиплексор 1 коммутирует входные сигналы таким образом, что опережающий сигнал x(t) подается на вход АЦП 2 реже запаздывающего y(t) в К+1 раз, как показано на фиг.2. Но поскольку в схеме задействован только один АЦП, то при переходе к отсчетам y(t) теряется первый отсчет, например, в момент времени и теряется отсчет y(ti), показанный на фиг.2 штриховой линией. Такая потеря вполне допустима, если исходить из того, что описываемый корреляционный измеритель предназначен для работы в условиях отличного от нуля временного сдвига τ между сигналами x(t) и y(t). В этом случае корреляции между появляющимися в один и тот же момент времени отсчетами сигналов x(f) и y(i) быть не может. Таким образом, на один отсчет x(t) приходится К отсчетов y(t) (см. фиг.2). Для записи и хранения отсчетов сигнала x(t) служит регистр 3, в нем каждый отсчет х(t) хранится в течение К тактов, что позволяет за это время осуществить К операций умножения отсчета x(t) на текущие отсчеты сигнала y(t), поступающие со входа АЦП 2. То есть за указанные К тактов, образующие один цикл, будет получено К произведений вида

x(ti)y(ti+kΔt),

где k - номер отсчета сигнала y(t) в цикле, k=1, 2…К;

Δt - период взятия отсчетов (период тактирования АЦП 2);

ti=i(K+1)Δt, i=0, 1, 2,…I.

Заметим, что произведение kΔt определяет величину искусственно вносимого временного сдвига, необходимого для вычисления ординат взаимокорреляционной функции R(τ), а значение К задает максимальный сдвиг, выраженный в количестве периодов Δt. Далее в момент времени ti+1 вместо отсчета x(ti) в регистр 2 заносится отсчет x(ti+1) и операция формирования произведений вышеуказанного вида повторяется для отсчетов сигнала y(ti+1+kΔt), и так, цикл за циклом, в течение интервала наблюдения формируются произведения отсчетов, необходимые для последующего вычисления корреляционной функции.

Вычисление корреляционной функции возлагается на арифметический узел, образованный перемножителем 4, мультиплексором 5, ОЗУ 6, сумматором 7 и буферным регистром 9. Во время вычисления корреляционной функции мультиплексор 5 коммутирует выход перемножителя 4 на вход сумматора 7 и таким образом произведения отсчетов поступают на один из входов сумматора 7, на другой вход которого поступает содержимое ОЗУ 6, соответствующее порядковому номеру произведения в цикле (значению k). Полученная таким образом сумма через буферный регистр 9 поступает в ОЗУ 6 для смены ранее находившегося операнда в ячейке, содержимое которой использовалось для получения настоящей суммы. Несложно понять, что если ОЗУ 6 в начале анализа будет принудительно обнулено, то вышеописанная процедура суммирования и пересылки будет являться реализацией алгоритма суммирования произведений с накоплением. При этом первое в цикле произведение записывается в ячейку ОЗУ 6 с адресом А(1), второе - в ячейку с адресом А(2), третье - в ячейку с адресом А(3) и так далее по предпоследнее произведение, последнее произведение, в связи с особенностями работы блока управления, записывается в ячейку с нулевым адресом. Схематически соответствие адресов ОЗУ отсчетам сигналов, участвующих в формировании произведений, показано на фиг.2. По истечении интервала наблюдения, который состоит из конечного числа вышерассмотренных циклов, в ОЗУ 6 будет накоплено К сумм вида

,

где (I+1) - число отсчетов сигнала x(t,) в течение интервала наблюдения.

После завершения этапа формирования сумм произведений отсчетов, то есть по истечении интервала наблюдения, измеритель переходит к этапу определения положения корреляционного пика, что осуществляется выявлением наибольшей из сумм Sk. Поиск максимальной из имеющихся в ОЗУ 6 сумм осуществляется путем последовательного инкрементирования содержимого всех задействованных ячеек ОЗУ 6 до тех пор, пока не будет достигнут некоторый пороговый уровень Р. Для этого на данном этапе через мультиплексор 5 на верхний по схеме вход сумматора 7 (см. фиг.1) подается код единицы, а адреса ячеек ОЗУ 6 последовательно меняют, вызывая таким образом на выход DO ОЗУ содержимое ячеек, после чего результат инкрементирования содержимого каждой вызванной ячейки ОЗУ 6 через буферный регистр 9 записывается в ту же ячейку. Одновременно блок 8 сравнения контролирует результат на выходе сумматора 7. При равенстве суммы на выходе сумматора 7 заданному значению P, блок 8 вырабатывает сигнал равенства, который подается на вход остановки ST блока 10 управления для завершения этапа поиска взаимокорреляционного пика. Оценку искомого временного сдвига τ*(k, Δt) определяют по адресу k ячейки ОЗУ 6, при котором наступило указанное равенство, то есть τ*(k, Δt)=kΔt. Причем, в связи с особенностями функционирования измерителя, как уже отмечалось, адреса ОЗУ 6 повторяют значения k, кроме нулевого. Нулевой адрес А(0) ОЗУ 5 соответствует максимальной задержке (см. фиг.2).

Пороговый уровень P фиксируется в блоке 8 сравнения и задается исходя из неравенства

P≥(I+1)(2N-1)2+1,

где N - разрядность операндов на входе перемножителя 4.

Блок 8 сравнения строится на основе компаратора идентичности [Аванесян Г.Р. Цифровые интегральные микросхемы. Справочное пособие. - М.: Радиотехника, 2008, стр.79, 80] и может представлять собой совокупность указанного компаратора и регистра, в котором хранится код величины Р. Один вход компаратора играет роль входа блока 8 сравнения (он является информационным), а другой вход является входом постоянной величины и соединяется с выходом упомянутого регистра в котором хранится эта величина. Разумеется, если интервал наблюдения будет фиксированным, то есть если I меняться не будет, то порог Р можно иметь постоянным. В таком случае в блоке сравнения от регистра, хранящего код P, можно отказаться, а требуемый код формировать путем задания фиксированных уровней напряжения на разрядах соответствующего входа компаратора.

Управляет работой корреляционного измерителя блок 10 (см. фиг.3). Запуск корреляционного измерителя производится путем подачи на вход CO блока 10 управления запускающего импульса, после чего блок 10 начинает формировать управляющие сигналы, согласно временным диаграммам представленным на фиг.4. Для упрощения на временных диаграммах показан случай К=4. Принцип действия блока 10 во многом аналогичен принципу действия блока управления, описанному в прототипе [Пат. RU 2229157. Опубл. 20.05.2004, Бюл. №14].

Рассмотрим вкратце принцип формирования управляющих сигналов. Перед началом запуска последовательную логику блока 10 обнуляют, переводя его, таким образом, в режим ожидания запускающего импульса, кроме того, предполагается, что ячейки ОЗУ 6 также обнулены. С появлением импульса запуска CO, поступающего на S-вход триггера 17, на выходе триггера 18, синхронно с положительным фронтом очередного тактового импульса (фиг.4, а), устанавливается высокий логический уровень, разрешающий прохождение тактовых импульсов на входы делителя 19 частоты и счетчиков 20, 21. Так как согласно алгоритму измерений в буферный регистр 4 в начале цикла заносится отсчет сигнала x(t), то для формирования адресного сигнала, направляющего сигнал x(t), используется первый импульс с выхода делителя 19 (фиг.4, в). В течение действия вершины указанного импульса адресный вход мультиплексора 1 находится под воздействием высокого логического уровня, обеспечивающего коммутацию на вход регистра 3 сигнала x(ti). Информация в указанный регистр заносится по переднему фронту первого тактового импульса CLK2 (фиг.4, д). После окончания действия адресного импульса мультиплексор 1 переходит в режим коммутации сигнала y(t), дискретизируемого в такт с импульсами последовательности CLK1 (фиг.4, г). Поскольку в нашем примере k=4, то каждый цикл будет состоять из четырех тактовых импульсов. Одновременно тактовые импульсы с выхода элемента 2И 23 через элементы задержки поступают на счетный вход счетчика 21 (фиг.4, е), который выполняет функции адресного и управляет адресацией ОЗУ 6. Сигналы записи/считывания ( ), необходимые для работы ОЗУ 6 являются смещенными во времени копиями тактовых импульсов CLK3, которые в свою очередь необходимы для тактирования регистра 9. Отсчет интервала наблюдения Т с дискретом Δt ведется счетчиком 20, коэффициент пересчета которого выбирается таким образом, чтобы с окончанием интервала наблюдения начал формироваться импульс переполнения, являющийся обнуляющим для триггера 17 и запускающим для триггера 31. Перевод триггера 31 в состояние высокого логического уровня на выходе приводит к установке на адресном выходе A3 блока высокого логического уровня переключающего мультиплексор 5 (см. фиг.1) и разрешению прохождения тактовых импульсов на счетный вход адресного счетчика 21 по истечении времени Т, что необходимо для формирования адресного кода на этапе определения максимальной величины находящейся в ОЗУ 6. При этом адресный код на выходе А2 блока 10 формируется, периодически повторяясь, до тех пор пока на вход остановки ST блока 10 не поступит сигнал равенства с выхода блока 8 сравнения.

Временные сдвиги, вносимые элементами 25, 26, 27, 28, 29 задержки, обеспечивают устойчивое однозначное функционирование измерителя за счет смещения во времени моментов обновления информации и моментов ее фиксации.

В отличие от прототипа, в котором используется группа накапливающих сумматоров, количество которых равно количеству вычисляемых ординат взаимокорреляционной функции, в рассмотренном измерителе все операции суммирования произведений и накоплений выполняются при помощи одного сумматора и ОЗУ, что значительно упрощает как структуру устройства, так и его стоимость, а также позволяет рационально использовать ресурсы памяти. Причем требования к быстродействию единственного в измерителе сумматора предъявляются те же, что и к сумматорам прототипа. Кроме того, предложенная схема позволила исключить блок поиска экстремума как отдельную структурную единицу, а его функции возложить на имеющиеся в измерителе аппаратные ресурсы. Что же касается дополнительно введенных для этой цели мультиплексора 5 и блока 8 сравнения, то они гораздо проще исключенного блока поиска экстремума.

1. Корреляционный измеритель временных сдвигов случайных сигналов, содержащий аналоговый мультиплексор, аналого-цифровой преобразователь, первый регистр, перемножитель и блок управления, выход аналогового мультиплексора подключен к информационному входу аналого-цифрового преобразователя, первый вход перемножителя соединен с выходом первого регистра, информационными входами измерителя являются соответственно первый и второй информационный входы аналогового мультиплексора, адресный вход которого подключен к первому адресному выходу блока управления, первый тактовый выход которого соединен с тактовым входом аналого-цифрового преобразователя, второй тактовый выход блока управления соединен с тактовым входом первого регистра, отличающийся тем, что в него введены оперативное запоминающее устройство, второй регистр, сумматор, цифровой мультиплексор и блок сравнения, выход аналого-цифрового преобразователя соединен с информационным входом первого регистра и вторым входом перемножителя, выход которого соединен с первым информационным входом цифрового мультиплексора, выход которого соединен с первым входом сумматора, выход которого соединен с информационным входом второго регистра, выход которого соединен с информационным входом оперативного запоминающего устройства, выход которого соединен со вторым входом сумматора, адресный и управляющий вход оперативного запоминающего устройства соединены с соответствующими выходами блока управления, третий тактовый выход которого соединен с тактовым входом второго регистра, вход блока сравнения соединен с выходом сумматора, а выход со входом остановки блока управления, выходом измерителя является второй адресный выход блока управления, адресный вход цифрового мультиплексора соединен с третьим адресным выходом блока управления, второй информационный вход цифрового мультиплексора является входом кода единицы.

2. Корреляционный измеритель временных сдвигов по п.1, отличающийся тем, что блок сравнения выполнен на основе компаратора идентичности, один из входов которого выполняет функции информационного, а другой является входом постоянной величины.