Программируемое логическое устройство

Иллюстрации

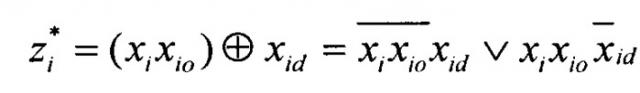

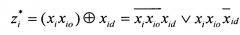

Показать всеИзобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в отказоустойчивой аппаратуре. Техническим результатом является сокращение аппаратных затрат при реализации систем логических функций большого количества переменных. Устройство содержит группы D-триггеров, блоки вычисления функций, счетчик, дешифратор, блоки конъюнкций, блоки значений конъюнкций, при этом блоки вычисления функций, блоки конъюнкций, блоки значений конъюнкций реализованы на базе логических элементов 2·2НЕ-И-ИЛИ, реализующих функцию . 4 ил., 8 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в отказоустойчивой аппаратуре.

Известно программируемое логическое устройство, содержащее g n-входовых элементов И (n - количество информационных входов устройства, 2≅g≅2n), t элементов ИЛИ (t - количество информационных выходов устройства), первую, вторую и третью группы D-триггеров, первую группу элементов И с тремя состояниями выхода, группу элементов И-НЕ с тремя состояниями выхода, g·t двухвходовых элементов И, счетчик и дешифратор, первый, второй и третий RS-триггеры, дополнительный элемент ИЛИ и вторую группу элементов И с тремя состояниями выхода (авт.св. СССР №1444892, кл. G11C 17/00, G06F 7/00, 1988 г.).

Недостатками известного устройства являются низкое быстродействие вычисления логических функций при наличии отказов и высокие аппаратурные затраты на реализацию систем логических функций вследствие использования стандартных логических базисов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторая группа m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, причем входом сброса D-триггеров первой, второй и третьей групп счетчика является вход сброса устройства, счетный вход счетчика является входом программирования устройства, а информационные выходы счетчика подключены к информационным входам дешифратора, неинверсные выходы D-триггеров второй группы подключены к управляющим входам соответствующих элементов И с тремя состояниями на выходе группы m·2n элементов И с тремя состояниями на выходе, неинверсные выходы D-триггеров третьей группы подключены ко вторым входам соответствующих элементов И группы m·2n элементов И, управляющие входы элементов второй группы m·2n элементов И с тремя состояниями на выходе подключены к инверсным выходам соответствующих D-триггеров второй группы D-триггеров, а информационные входы элементов второй группы m·2n элементов И с тремя состояниями на выходе являются соответствующими входами расширения соответствующей группы из m групп входов расширения, выходы элементов И с тремя состояниями на выходе объединены и подключены ко входам настройки соответствующего из m блоков вычисления функций, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы, четвертый выход дешифратора является выходом окончания программирования устройства, информационные входы D-триггеров первой и второй группы являются соответствующими входами расширения соответствующей из m групп входов расширения, информационные входы D-триггеров третьей группы являются 2(n-1) входами расширения соответствующей из m групп входов расширения, первые входы элементов И группы m(n-1) элементов И являются соответствующими из n-1 неинверсных входов группы 2n·m входов парафазных входных переменных (по 2m разрядов на каждый блок вычисления функций), первые входы элементов ИЛИ группы m(m-1) элементов ИЛИ являются соответствующими из n-1 инверсных входов группы 2n·m входов парафазных входных переменных (по 2m разрядов на каждый из m блоков вычисления функций), выходы элементов И группы m(n-1) элементов И подключены к соответствующим i-м инверсным входам парафазных входных переменных соответствующего из m блоков вычисления функций , а старший неинверсный разряд этих входов является соответствующим n-м неинверсным входом группы 2n·m входов парафазных входных переменных, выходы элементов ИЛИ группы m(n-1) элементов ИЛИ подключены к соответствующим i-м инверсным входам парафазных входных переменных соответствующего из m блоков вычисления функций , а старший инверсный разряд этих входов является соответствующим n-м инверсным входам группы 2n·m входов парафазных входных переменных, входы сброса блоков вычисления функций являются входом сброса устройства, входы синхронизации блоков вычисления функций являются входом синхронизации устройства, дополнительные входы сброса блоков вычисления функций являются группой m входов дополнительного сброса устройства, входы реконфигурации m блоков вычисления функций являются группой m входов реконфигурации блоков вычисления функций при отказах, входы типа реконфигурации m блоков вычисления функции при отказах являются группой m входов типа реконфигурации блоков вычисления функций при отказах, выходы неинверсного значения функции блоков вычисления функций являются соответствующими разрядами группы m выходов значений функции устройства, выходы инверсного значения функции блоков вычисления функций являются соответствующими разрядами группы m выходов инверсных значений функций устройства, выходы готовности результатов вычислений блоков вычисления функций являются группой m выходов готовности результатов вычисления функций устройства, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов, ), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе, причем входы управления нечетных элементов И с тремя состояниями на выходе из группы 4·2n элементов И с тремя состояниями на выходе подключены к неинверсному выходу Т-триггера, инверсный выход которого подключен ко входам управления четырех элементов И с тремя состояниями на выходе из группы 4·2n элементов И с тремя состояниями на выходе, информационные выходы которых являются соответствующими разрядами входов настройки блока, информационные входы нечетных элементов И с тремя состояниями на выходе из первой половины группы 4·2n элементов И с тремя состояниями на выходе подключены к соответствующим j-м элементам второй половины входов настройки, , информационные входы нечетных элементов И с тремя состояниями на выходе из второй половины 4·2n элементов И с тремя состояниями на выходе подключены к соответствующим М разрядам первой половины входов настройки, , выходы нечетных элементов И с тремя состояниями на выходе группы 4·2n элементов И с тремя состояниями на выходе объединены с выходами соответствующих четных элементов И с тремя состояниями на выходе и подключены к соответствующим нечетным входам соответствующего элемента 2·2НЕ-И-ИЛИ первой группы из n групп элементов 2·2НЕ-И-ИЛИ (по две пары нечетный - четный элемент И с тремя состояниями выхода на каждый элемент 2·2НЕ-И-ИЛИ, четные входы элементов 2·2НЕ-И-ИЛИ каждой S-й группы, , элементов 2·2НЕ-И-ИЛИ являются соответствующими разрядами входов парафазных входных переменных блока (второй вход каждого элемента 2·2НЕ-И-ИЛИ S-й группы является входом XS, четвертый - ), выходы элементов 2·2НЕ-И-ИЛИ S-й группы, , где n - число входных переменных, подключены к соответствующим нечетным входам элементов 2·2НЕ-И-ИЛИ S+1 группы, причем к каждому элементу 2·2НЕ-И-ИЛИ в группы подключены выходы двух элементов i-1 групп, выход единственного элемента 2·2НЕ-И-ИЛИ последней n-й группы из n групп элементов 2·2НЕ-И-ИЛИ подключен к информационному входу первого D-триггера, второй вход этого элемента подключен к выходу первого элемента ИЛИ, а четвертый вход этого элемента 2·2НЕ-И-ИЛИ n-й группы подключен к выходу второго элемента ИЛИ, первые входы первого и второго элементов ИЛИ подключены к выходам первого и второго элементов И соответственно, второй вход первого элемента ИЛИ подключен к объединенным выходам первого и второго элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями при выходе, второй вход второго элемента ИЛИ подключен к объединенным выходам третьего и четвертого элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе, вторые входы первого и второго элементов И, входы второго и четвертого инвертора являются видом реконфигурации блока при отказах, первый вход первого элемента И и вход первого инвертора являются входом типа реконфигурации блока при отказах, выход первого инвертора подключен к первому входу второго элемента И, вход обнуления первого D-триггера и первый вход четвертого элемента ИЛИ являются входом сброса блока, входы синхронизации первого и второго D-триггеров, счетный вход Т-триггера, вход элемента задержки являются входом синхронизации блока, выход второго инвертора подключен ко второму входу четвертого элемента ИЛИ, третий вход которого является входом дополнительного сброса блока, выход четвертого элемента ИЛИ подключен ко входам обнуления второго D-триггера, RS-триггера фиксации импульса и Т-триггера, выход первого D-триггера подключен к информационному входу второго D-триггера и первому входу третьего элемента ИЛИ, второй вход которого подключен к выходу второго D-триггера, выход третьего элемента ИЛИ является выходом значения функции блока и подключен ко входу третьего инвертора и первому входу пятого элемента ИЛИ, выход третьего инвертора является выходом инверсного значения функции блока, выход четвертого инвертора подключен ко второму входу пятого элемента ИЛИ, третий вход которого подключен ко входу третьего элемента И, выход пятого элемента ИЛИ является выходом готовности результатов вычисления функций блока, первый вход третьего элемента И подключен к выходу RS-триггера функции импульса, а второй вход третьего элемента И подключен к инверсному выходу Т-триггера, который также подключен ко входам управления нечетных элементов И с тремя состояниями на выходе дополнительной группы элементов с тремя состояниями на выходе, ко входам управления четных элементов которой подключен неинверсный выход Т-триггера, информационные входы первого и четвертого элементов И с тремя состояниями на выходе являются n-м инверсным входом хn парафазных входных переменных блока, а информационные входы второго и третьего элементов И с тремя состояниями на выходе дополнительной группы элементов И с тремя состояниями на выходе являются n-м инверсным входом парафазных входных переменных блока (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00). Данное устройство принято за прототип.

Недостатком известного устройства, принятого за прототип, являются высокие аппаратурные затраты на реализацию систем логических функций большого числа переменных.

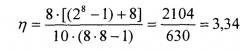

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию логических функций в совершенной дизъюнктивной нормальной форме (СДНФ). В связи с этим, каждый блок вычисления функций должен иметь 2n настроечных входов для задания всех возможных конституент функции n переменных, хотя некоторые из них могут повторяться в других функциях системы функций. Для реализации каждого блока вычисления функций в прототипе необходим 2n-1 элемент, что приводит к невозможности такой реализации даже для небольших n - порядка 8…10. В настоящее время в программируемых логических интегральных схемах (ПЛИС) переход на блоки вычисления функций (LUT) 6 переменных только начат, в основном используются блоки 4, 5 переменных.

Задачей изобретения является снижение аппаратных затрат на реализацию систем логических функций большого количества переменных.

Поставленная задача была решена за счет того, что в известное программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций, где m - число вычисляемых логических функций, счетчик, дешифратор, причем информационные входы D-триггеров из групп D-триггеров подключены к соответствующим разрядам входов данных, входы сброса всех D-триггеров всех групп D-триггеров и вход сброса счетчика объединены и подключены ко входу сброса устройства, выход счетчика подключен ко входу дешифратора, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы D-триггеров, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы D-триггеров, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы D-триггеров, выходы группы m блоков вычисления функций являются выходами устройства, каждый блок вычисления функций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию , где k=int log2(n),(n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2НЕ-И-ИЛИ двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ дополнительно введены k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D-триггеров, вторых D-триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D-триггеров, вторых D-триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D-триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D-триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D-триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам функций блоков значений конъюнкций, причем нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2НЕ-И-ИЛИ, реализующих функцию , подключены к третьим входам соответствующих элементов второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены ко вторым входам второй группы элементов 2·2НЕ-И-ИЛИ, выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ содержат два элемента 2·2НЕ-И-ИЛИ и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блока конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-ый блок значений конъюнкций содержит k групп n-1 элементов 2·2НЕ-И-ИЛИ, где k=int log2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2НЕ-И-ИЛИ подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , подключены к четным входам четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ содержат два элемента 2·2НЕ-И-ИЛИ и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций.

Введение процедуры вычисления логических функций в дизъюнктивной нормальной форме (ДНФ) на базе логических элементов, реализующих функцию 2·2НЕ-И-ИЛИ , позволяет снизить аппаратные затраты на реализацию систем логических функций большого количества переменных.

Суть новой введенной процедуры заключается в следующем:

а) в задании для каждой конъюнкции вычисляемой системы логических функций трех констант - масок: основной, выделяющей существенные переменные, дополнительной, выделяющей не инверсные существенные переменные, выходных функций, указывающей, какие функции системы функций активирует данная конъюнкция;

б) в вычислении каждого разряда данной конъюнкции по соответствующему разряду входного вектора с использованием логических элементов 2·2НЕ-И-ИЛИ;

в) в вычислении значений данной конъюнкции по соответствующим результатам вычисления всех ее разрядов с использованием логических элементов 2·2НЕ-И-ИЛИ;

г) в вычислении значений функций по результатам вычисления всех конъюнкций с использованием логических элементов 2·2НЕ-И-ИЛИ.

Введение дополнительных k-1 групп триггеров первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций позволяет хранить в процессе вычислений k-1 n-разрядную основную маску для выделения существенных переменных (ХО) для обеспечения вычислений в k-1 блоках конъюнкций.

Введение дополнительных k-1 групп вторых D-триггеров количеством n позволяет хранить в процессе вычислений k-1 n-разрядную дополнительную маску для выделения не инверсных существенных переменных (XD) для обеспечения вычислений в k-1 блоках конъюнкций.

Введение дополнительных k-1 групп третьих D-триггеров количеством n позволяет хранить в процессе вычислений k-1 n-разрядную маску выходных функций (ZB), указывающую, какие функции системы функций активирует данная конъюнкция для обеспечения вычислений в блоках вычисления функций.

Введение блоков конъюнкций с предлагаемой структурой и соответствующими связями позволяет вычислять каждый разряд данной конъюнкции по соответствующему разряду входного вектора с использованием логических элементов 2·2НЕ-И-ИЛИ.

Введение блоков значений конъюнкций с предлагаемой структурой и соответствующими связями позволяет вычислять значение данной конъюнкции по соответствующим результатам вычисления всех ее разрядов в блоках конъюнкций с использованием логических элементов 2·2НЕ-И-ИЛИ, при этом, если конъюнкция истинна, то есть равна единице (все существенные разряды входного вектора совпадают с соответствующими данной конъюнкции), то на выходе блока значений формируется нулевой сигнал.

Введение новых связей для m блоков вычисления функций позволяет вычислять значения функций в системе функций по результатам вычислений в блоках значений конъюнкций, используя настроечную информацию в k-1 группах третьих D-триггеров во время реализации новой введенной дисциплины.

Введение новых связей для D-триггеров первой группы позволяет хранить в процессе вычислений n-разрядную основную маску для выделения существенных переменных (ХО) для обеспечения вычислений в первом блоке конъюнкций.

Введение новых связей для D-триггеров второй группы позволяет хранить в процессе вычислений n-разрядную основную маску для выделения существенных переменных (ХО) для обеспечения вычислений в первом блоке конъюнкций.

Введение новых связей для дешифратора позволяет обеспечить программирование дополнительных k-1 групп D-триггеров первой, второй и третьей групп для последующего участия их в реализации вычислений логических функций.

Введение новых связей элементов в блоке вычисления функций позволяет вычислять значения функций в системе функций по результатам вычислений в блоках значений конъюнкций, используя настроечную информацию в k-1 группах третьих D-триггеров во время реализации новой введенной дисциплины.

На фиг.1 изображена схема электрическая структурная программируемого логического устройства.

На фиг.2 - схема электрическая функциональная j-го разряда - i-го блока конъюнкции.

На фиг.3 - схема электрическая функциональная i-го блока значений конъюнкции.

На фиг.4 - схема электрическая функциональная i-го блока вычисления функций.

Программируемое логическое устройство содержит первую 1, вторую 2 и третью 3 группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций 4, где m - число вычисляемых логических функций, счетчик 5, дешифратор 6, k-1 групп первых D-триггеров 7 количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров 8 количеством n, k-1 групп третьих D-триггеров 9 количеством n, группу k блоков конъюнкций 10, группу k блоков значений конъюнкций 11.

Устройство имеет входы задания переменных 12.

Информационные входы D-триггеров из групп 1, 2, 3, 7, 8, 9 D-триггеров подключены к соответствующим разрядам входов данных 13.

Входы сброса всех D-триггеров из групп 1, 2, 3, 7, 8, 9 D-триггеров и вход сброса счетчика 5 объединены и подключены ко входу сброса 14 устройства.

Выход счетчика 5 подключен ко входу дешифратора 6.

Первый выход 6.1.1 дешифратора 6 подключен ко входам синхронизации D-триггеров первой группы D-триггеров 1.

Второй выход 6.1.2 дешифратора 6 подключен ко входам синхронизации D-триггеров второй группы D-триггеров 2.

Третий выход 6.1.3 дешифратора 6 подключен ко входам синхронизации D-триггеров третьей группы D-триггеров 3.

Счетный вход счетчика 5 является входом программирования устройства 15.

Выходы группы m блоков вычисления функций 4 являются выходами устройства 16.

Информационные входы D-триггеров k-1 групп первых D-триггеров 7, вторых D-триггеров 8, третьих D-триггеров 9 подключены к соответствующим разрядам настроечных входов 13.

Входы сброса D-триггеров k-1 групп первых D-триггеров 7, вторых D-триггеров 8, третьих D-триггеров 9 объединены и подключены ко входу сброса 14 устройства.

Входы синхронизации D-триггеров i-ой из k-1 групп первых D-триггеров 7 подключены к соответствующим i-м из k-1 выходов 6.i.1 дешифратора 6 для k-1 групп первых D-триггеров 7.

Входы синхронизации D-триггеров i-ой из k-1 групп вторых D-триггеров 8 подключены к соответствующим i-м из k-1 выходов 6.i.2 дешифратора 6 для k-1 групп вторых D-триггеров 8.

Входы синхронизации D-триггеров i-ой из k-1 групп третьих D-триггеров 9 подключены к соответствующим i-м из k-1 выходов 6.i.3 дешифратора 6 для k-1 групп третьих D-триггеров 9.

Выходы группы первых D-триггеров 1 подключены к первой группе входов 10.1.1 первого блока конъюнкций 10.1.

Выходы группы вторых D-триггеров 2 подключены ко второй группе входов 10.1.2 первого блока конъюнкций 10.1.

Третьи группы входов 10.1.3 всех блоков конъюнкций подключены ко входу задания переменных 12 устройства.

Выходы k-1 групп первых D-триггеров 7 подключены к первым группам входов 10.i.1 соответствующих i-ых из k-1 блоков конъюнкций 10.i (i=2…k).

Выходы k-1 групп вторых D-триггеров 8 подключены ко вторым группам входов 10.i.2 соответствующих i-ых из k-1 блоков конъюнкций 10.i (i=2…k).

Выходы 10.1.4 i-ых блоков конъюнкций 10.i подключены ко входам соответствующих блоков значений конъюнкций 11.i.

Выходы j-ых блоков значений конъюнкций 11.i подключены ко входам конъюнкций 4.j каждого из блоков вычисления функций 4 (j=1…k).

Выходы i-ых D-триггеров из k-1 групп третьих D-триггеров 9 подключены к соответствующим i-ым входам функций 4.2.i (i=1…m) блоков вычисления функций 4.

Устройство имеет выходы значений функций 16.

Последний выход дешифратора 6 является выходом готовности 17 устройства.

Каждый блок i-ый вычисления функций 10.i содержат k групп n-1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию , где k=int log2(n), (n=2k). В первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов.

Нечетные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.1.j количеством r, где r=2n-1 подключены к соответствующим входам первой группы входов блока вычисления функций 4.1.1, 4.3.1…4.n-1.1. При этом предполагается, что .

Четные входы первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.1.j подключены к соответствующим входам 4.2.1, 4.4.1…4.n.1 второй группы входов блока вычисления функций.

Выходы нечетных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , подключены к нечетным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.2.j.

Выходы четных элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.1 подключены к четным входам второй группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.2.

Аналогично выходы нечетных элементов нечетной группы элементов 22·2НЕ-И-ИЛИ, реализующих функцию , 18.k подключены к нечетным входам следующей группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.k+1.

Выходы четных элементов нечетной группы 2·2НЕ-И-ИЛИ, реализующих функцию , 18.k подключены к четным входам следующей группы элементов ·2·2НЕ-И-ИЛИ, реализующих функцию , 18.k+1.

Выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 18.k-1.1, 18.k-1.2 содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию .

Выход первого элемента предпоследней группы 18.k-1.1 подключен к первому и второму входам единственного элемента последней группы 18.k.

Выход второго элемента предпоследней группы 18.k-1.2 подключен к третьему и четвертому входам единственного элемента последней группы 18.k, выход которого является выходом i-го блока вычисления функций 16.i.

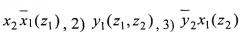

Каждый i-ый блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 19-24.

Входы первых трех элементов 19, 20, 21 объединены, вход первого элемента 19 подключен к соответствующему i-му входу 10.1.3.i третьей группы входов соответствующего блока конъюнкций 10 и к первым двум входам четвертого элемента 22.

Вход второго элемента 20 подключен к соответствующему i-му входу 10.1.1.i первой группы входов данного блока конъюнкций 10 и к третьему и четвертому входам четвертого элемента 23.

Вход третьего элемента 21 подключен к соответствующему i-му входу 10.1.2.i второй группы входов блока конъюнкций 10 и ко второму входу шестого элемента 24, выход которого является i-м выходом 10.1.4.i i-го блока конъюнкций 10.

Выход первого элемента 19 подключен к первому и третьему входам пятого элемента 23.

Выход второго элемента 20 подключен ко второму и четвертому входам пятого элемента 23.

Выход третьего элементам 21 подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента 24.

Выход пятого элемента 23 подключен к четвертому входу шестого элемента 24. Каждый i-ый блок значений конъюнкций 11 содержит k групп n-1 пирамидально соединенных элементов 25, 2·2НЕ-И-ИЛИ, реализующих функцию , где k=int log2(n), (n=2k), и дополнительный элемент 26.

Первый и второй входы элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 25.1 подключены к соответствующим нечетным входам блока значений конъюнкций 10.1.4.

Третий и четвертый входы элементов первой группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 25.1 подключены к соответствующим четным входам блока значений конъюнкций 10.1.4.

Выходы нечетных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 25.k подключены к нечетным входам четной группы 24.k+1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию .

Выходы четных элементов нечетной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 25.k подключены к четным входам четной группы 25.k+1 элементов 2·2НЕ-И-ИЛИ, реализующих функцию .

Выходы предпоследней группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию , 25.k-1 содержат два элемента 2·2НЕ-И-ИЛИ, реализующих функцию , 25.k-1.1, 25.k-1.2 и выход первого элемента предпоследней группы 25.k-1.1 подключен к первому и второму входам единственного элемента последней группы 25.k.

Выход второго элемента предпоследней группы 25.k-1.2 подключен к третьему и четвертому входам единственного элемента последней группы 25.k, выход которого подключен ко всем входам дополнительного элемента 26, выход которого является выходом данного i-го блока значений конъюнкций 11.1.i.

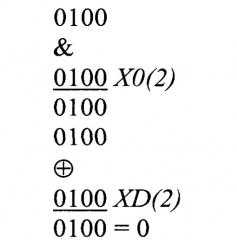

Первая группа D-триггеров 1 и k-1 групп первых D-триггеров 7 (фиг.1) количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций предназначены для записи и хранения в процессе вычислений информации настройки k n-разрядных основных масок для выделения существенных переменных (ХО) с целью обеспечения вычислений в k блоках конъюнкций 10.

Запись в j-e триггеры D-триггеров этих групп 1, 7 осуществляется с соответствующих j-x разрядов настоечных входов 13 по переднему фронту сигнала "1" на выходе 6.j.1 дешифратора 6 j=1…k.

D-триггеры этих групп 1, 7 обнуляются по входу обнуления 14. Настроечная информация, записанная в D-триггерах этих групп 1,7, управляет входами настройки 10.1.1-10.k.1 k блоков конъюнкций 10.1-10.k и определяет реализуемые в конъюнкциях существенные переменные.

D-триггеры этих групп 1, 7 могут быть реализованы, например, на интегральных микросхемах 155ТМ2 с дополнительными инверторами по входу R.

Вторая группа D-триггеров 2 и k-1 групп вторых D-триггеров 8 (фиг.1) количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций предназначены для записи и хранения в процессе вычислений информации настройки k n-разрядных дополнительных масок не инверсных существенных переменных (XD) с целью обеспечения вычислений в k блоках конъюнкций 10.

Запись в j-e триггеры D-триггеров этих групп 2, 8 осуществляется с соответствующих j-x разрядов настоечных входов 13 по переднему фронту сигнала "1" на выходе 6.j.2 дешифратора 6, j=1…k.

D-триггеры этих групп 2, 8 обнуляются по входу обнуления 14. Настроечная информация, записанная в D-триггерах этих групп 2, 8, управляет входами настройки 10.1.2-10.k.2 k блоков конъюнкций 10.1-10.k и определяет реализуемые в конъюнкциях существенные неинверсные переменные.

D-триггеры этих групп 2, 8 могут быть реализованы, например, на интегральных микросхемах 155ТМ2 с дополнительными инверторами по входу R.

Третья группа D-триггеров 3 и k-1 групп третьих D-триггеров 9 (фиг.1) количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций предназначены для записи и хранения в процессе вычислений информации настройки k n-разрядных масок выходных функций (ZB), указывающих, какие функции системы функций активирует данная конъюнкция для обеспечения вычислений в блоках вычисления функций 4.

Запись в j-e триггеры D-триггеров этих групп 3, 9 осуществляется с соответствующих j-x разрядов настоечных входов 13 по переднему фронту сигнала "1" на выходе 6.j.3 дешифратора 6, j=1…k.

D-триггеры этих групп 3, 9 обнуляются по входу обнуления 14. Настроечная информация, записанная в D-триггерах этих групп 3, 9, управляет входами настройки 4.2.1-4.2.m m блоков вычисления функций 4, m≤n и указывает, какие функции системы функций активирует данная конъюнкция для обеспечения вычислений в блоках вычисления функций 4.

D-триггеры этих групп 3