Устройство для контроля качества канала передачи данных

Иллюстрации

Показать всеИзобретение относится к измерительной технике. Технический результат заключается в повышении достоверности контроля качества линии связи канала передачи данных и оконечного передающего оборудования. Устройство содержит модем, состоящий из демодулятора и модулятора, измеритель коэффициента взаимного различия, состоящий из двух перемножителей, фазовращателя, двух интеграторов, двух квадраторов, сумматора, стробирующего блока и нормирующего блока, группу элементов И, элемент ИЛИ, элемент ИЛИ-НЕ, триггер, регистр, блок измерения отношения энергии сигнала к спектральной плотности шума, измеритель порогового значения коэффициента взаимного различия, состоящий из элемента И, удвоителя, квадратора, логарифмирующего устройства, делителя; компаратор, блок вывода результатов контроля, группу линий задержки, аналого-цифровой преобразователь, управляемую линию задержки, ключ, дополнительно введены элемент ИЛИ, два элемента И, RS-триггер, компаратор, два устройства для вычисления математического ожидания, состоящие из двух элементов ИЛИ, двух инверторов, регистра, двух регистров сдвига, группы элементов И, группы сумматоров, счетчика, делителя. 2 ил.

Реферат

Изобретение относится к измерительной технике и может использоваться для создания систем автоматизированного контроля качества канала передачи данных без перерыва в приеме несущей частоты, модулированной информационной кодовой последовательностью.

Известно устройство для автоматизированного контроля линии связи канала передачи данных, содержащее модем, состоящий из демодулятора и модулятора, измерителя коэффициента взаимного различия (ИКВР), группу элементов И, элемент ИЛИ, элемент ИЛИ-НЕ, триггер, регистр, блок измерения отношения энергии сигнала к спектральной плотности шума (авторское свидетельство СССР №1001489, кл. Н04В 3/46), измеритель порогового значения коэффициента взаимного различия, компаратор, блок вывода результатов контроля, аналого-цифровой преобразователь, группу линий задержки, управляемую линию задержки, ключ (см. патент на изобретение RU 2304847 С2, кл. Н04В 3/46).

Недостатком данного устройства является низкая достоверность оценки качества не только линии связи канала передачи данных, но и оконечного передающего оборудования, являющихся составными частями канала передачи данных.

Цель изобретения - повышение достоверности контроля качества линии связи канала передачи данных и оконечного передающего оборудования, являющихся составными частями канала передачи данных. Под каналом передачи данных может пониматься как кабель, так и радиоканал.

Для достижения поставленной цели в устройство для автоматизированного контроля линии связи канала передачи данных, содержащее модем, состоящий из демодулятора и модулятора, измерителя коэффициента взаимного различия (ИКВР), группу элементов И, элемент ИЛИ, элемент ИЛИ-НЕ, триггер, регистр, блок измерения отношения энергии сигнала к спектральной плотности шума (авторское свидетельство СССР №1001489, кл. Н04В 3/46), измеритель порогового значения коэффициента взаимного различия, компаратор, блок вывода результатов контроля, группу линий задержки, аналого-цифровой преобразователь, управляемую линию задержки, ключ, введены элемент ИЛИ, два элемента И, RS-триггер, компаратор, два устройства для вычисления математического ожидания (фигура 2), состоящие из двух элементов ИЛИ, двух инверторов, регистра, двух регистров сдвига, группы элементов И, группы сумматоров, счетчика, делителя, элемента И, причем входы элемента ИЛИ подключены к первому и второму выходам первого компаратора, сравнивающего коэффициент взаимного различия с пороговым значением коэффициента взаимного различия (КВР), а выход элемента ИЛИ подключен к установочному S входу RS-триггера, сбросовый R вход которого соединен с третьим выходом первого компаратора, сравнивающего коэффициент взаимного различия с пороговым значением КВР, а выход RS-триггера соединен с первыми входами двух элементов И и управляющими входами устройств для вычисления математического ожидания, причем второй вход первого из них соединен с выходом аналого-цифрового преобразователя и с первым входом первого компаратора, а второй вход второго из них соединен с выходом измерителя порогового значения КВР и со вторым входом первого компаратора, а выход каждого из элементов И соединен с входами соответствующих им устройств для вычисления математического ожидания, причем выходы устройств для вычисления математического ожидания подключены к входам компаратора, сравнивающего математическое ожидание флуктуации коэффициента взаимного различия и математическое ожидание флуктуации порогового значения КВР, а выходы компаратора, сравнивающего математические ожидания, подключены к четвертому и пятому входам блока вывода результатов контроля, причем вход устройства для вычисления математического ожидания является входом первого инвертора, первым входом первого элемента ИЛИ и входом первого регистра сдвига, которые являются составными компонентами устройства для вычисления математического ожидания, причем выход первого инвертора соединен со вторым входом первого элемента ИЛИ, выход которого соединен с входом второго регистра сдвига, выход которого соединен с входом счетчика, с первым входом второго элемента ИЛИ и со вторыми входами группы элементов И, причем первые входы группы элементов И соединены с соответствующими выходами первого регистра сдвига, а выходы группы элементов И соединены с соответствующими входами группы сумматоров, вторые входы которых соединены с соответствующими выходами регистра, также сумматоры соединены последовательно между собой для осуществления переносов значений в старшие разряды, причем вход, служащий для осуществления переноса в старший разряд, последнего сумматора соединен с первым входом элемента И, второй вход которого соединен с последним выходом регистра, а выход элемента И соединен со сбросовым входом регистра и со сбросовым входом счетчика, а выходы сумматоров соединены с соответствующими входами регистра и с соответствующими входами делителя, другой вход которого соединен с выходом счетчика, а выход делителя является выходом устройства для вычисления математического ожидания; управляющие входы устройств для вычисления математического ожидания соединены с входом второго инвертора, выход которого соединен со вторым входом элемента И, причем выход элемента И соединен со сбросовым входом второго регистра сдвига.

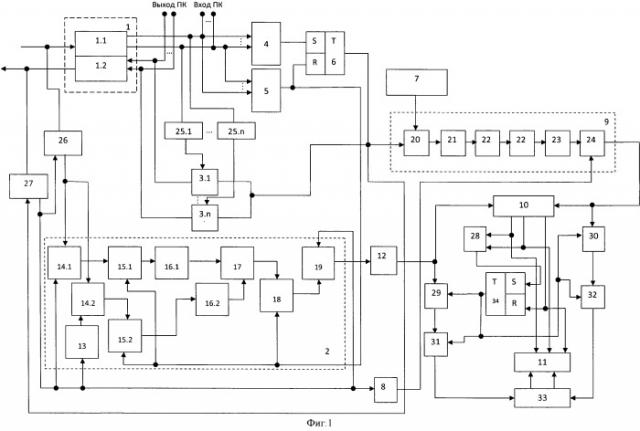

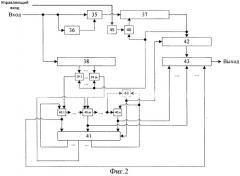

На фигурах 1 и 2 приведена функциональная электрическая схема предлагаемого устройства.

Устройство для контроля качества канала передачи данных содержит модем 1, состоящий из демодулятора 1.1 и модулятора 1.2, измеритель коэффициента взаимного различия (ИКВР) 2, состоящий из двух перемножителей 14.1, 14.2, фазовращателя 13, осуществляющего преобразование по Гильберту сигнала с выхода ключа 27, двух интеграторов 15.1, 15.2, двух квадраторов 16.1, 16.2, сумматора 17, стробирующего блока 18 и нормирующего блока 19; группу элементов И 3.1-И 3.n (количество элементов n определяется количеством информационных контактов параллельного входа модулятора 1.2 модема 1), элемент ИЛИ 4, элемент ИЛИ-НЕ 5, триггер 6, регистр 7, блок измерения отношения энергии сигнала к спектральной плотности шума 8 (авторское свидетельство СССР №1001489, кл. Н04В 3/46), измеритель порогового значения коэффициента взаимного различия 9, состоящий из элемента И 20, удвоителя 21, квадратора 22, логарифмирующего устройства 23, делителя 24, подключенных последовательно; компаратор 10, блок вывода результатов контроля 11, аналого-цифровой преобразователь 12, группу линий задержки 25.1-25.n, управляемую линию задержки 26, ключ 27, элемент ИЛИ 28, элемент И 29, элемент И 30, компаратор 33, RS-триггер 34, устройства для вычисления математического ожидания 31 и 32 (фигура 2), состоящие из элемента ИЛИ 35, инвертора 36, регистров сдвига 37 и 38, группы элементов И 39.1-39.m, группы сумматоров 40.1-40.m-40.n, регистра 41, счетчика 42, делителя 43, элемента И 44, инвертора 45, элемента ИЛИ 46, причем параллельный выход демодулятора 1.1 модема 1 подключен к входу компьютера, к входам элемента ИЛИ 4 и к входам элемента ИЛИ-НЕ 5 и каждый контакт параллельного выхода демодулятора модема через соответствующие линии задержки 25.1-25.n подключен к одному входу соответствующего элемента И из группы элементов И 3.1-3.n, к другим входам которых параллельно подключен выход триггера 6, который также подключен к первому входу элемента И 20 измерителя порогового значения коэффициента взаимного различия 9 и к управляющему входу ключа 27; установочный вход триггера 6 подключен к выходу элемента ИЛИ 4, а сбросовый вход триггера 6 подключен параллельно к выходу элемента ИЛИ-НЕ 5, входам интеграторов 15.1, 15.2, входу стробирующего блока 18 измерителя коэффициента взаимного различия 2, выход каждого элемента И из группы элементов И 3.1-3.n подключен к соответствующему информационному контакту параллельного входа модулятора 1.2 модема 1 и к выходу компьютера, выход нормирующего блока 19 измерителя коэффициента взаимного различия 2 подключен к входу АЦП 12, а выход АЦП 12 подключен к первому входу первого компаратора 10, к другому входу которого подключен выход делителя 24 измерителя порогового значения коэффициента взаимного различия 9, а выходы первого компаратора 10 (А<В), (А-В), (А>В) подключены к блоку выводов результата контроля 11. Выход регистра 7 подключен к второму входу элемента И 20 измерителя порогового значения коэффициента взаимного различия 9. Вход линии связи в демодулятор 1.1 и выход модулятора 1.2 в линию связи модема 1 являются входами заявляемого устройства, а вход линии связи в демодулятор 1.1 подключен к первому входу управляемой линии задержки 26, а выход управляемой линии задержки 26 подключен параллельно к входам перемножителей 14.1, 14.2 измерителя коэффициента взаимного различия 2, выход модулятора 1.2 в линию связи подключен к первому входу ключа 27, выход которого параллельно подключен к управляющему входу управляемой линии задержки 26, к другому входу перемножителя 14.1, входу фазовращателя 13, первому входу нормирующего блока 19 измерителя коэффициента взаимного различия 2 и к входу блока измерения отношения энергии сигнала к спектральной плотности шума 8, выход которого подключен к первому входу делителя 24 измерителя порогового значения коэффициента взаимного различия 9, выход фазовращателя 13 подключен к второму входу перемножителя 14.2, выходы перемножителей 14.1, 14.2 подключены соответственно к входам интеграторов 15.1, 15.2, выходы которых подключены соответственно к входам квадраторов 16.1, 16.2, выходы которых подключены к входам сумматора 17, выход которого подключен к второму входу стробирующего блока 18, выход которого подключен к второму входу нормирующего блока 19; входы элемента ИЛИ 28 подключены к первому и второму выходам компаратора 10, а выход элемента ИЛИ 28 подключен к установочному S входу RS-триггера 34, сбросовый R вход которого соединен с третьим выходом компаратора 10, а выход RS-триггера 34 соединен с первым входом элемента И 29, с первым входом элемента И 30 и управляющими входами устройств для вычисления математического ожидания 31 и 32, причем второй вход элемента И 29 соединен с выходом аналого-цифрового преобразователя 12 и с первым входом компаратора 10, а второй вход элемента И 30 соединен с выходом делителя 24 и со вторым входом компаратора 10, а выход элемента И 29 и выход элемента И 30 соединены с первыми входами соответствующих им устройств для вычисления математического ожидания 31 и 32, причем выходы устройств для вычисления математического ожидания 31 и 32 подключены к входам компаратора 33, а выходы компаратора 33 подключены к четвертому и пятому входам блока вывода результатов контроля 11; причем вход инвертора 36, первый вход элемента ИЛИ 35, вход регистра сдвига 38 являются входом устройства для вычисления математического ожидания, причем выход инвертора 36 соединен со вторым входом элемента ИЛИ 35, выход которого соединен с входом регистра сдвига 37, выход которого соединен с входом счетчика 42, с первым входом элемента И 46 и со вторыми входами группы элементов И 39.1-39.m, причем первые входы группы элементов И 39.1-39.m соединены с соответствующими выходами регистра сдвига 38, а выходы группы элементов И 39.1-39.m соединены с соответствующими входами группы сумматоров 40.1-40.m-40.n, вторые входы которых соединены с соответствующими выходами регистра 41, также сумматоры 40.1-40.m-40.n соединены последовательно между собой для осуществления переносов значений в старшие разряды, причем вход, служащий для осуществления переноса в старший разряд, сумматора 40.n соединен с первым входом элемента И 44, второй вход которого соединен с последним выходом регистра 41, а выход элемента И 44 соединен со сбросовым входом регистра 41 и со сбросовым входом счетчика 42, а выходы сумматоров 40.1-40.m-40.n соединены с соответствующими входами регистра 41 и с соответствующими входами делителя 43, другой вход которого соединен с выходом счетчика 42, а выход делителя 43 является выходом устройства для вычисления математического ожидания; управляющие входы устройств для вычисления математического ожидания 31 и 32 соединены с входом инвертора 45, выход которого соединен со вторым входом элемента И 46, причем выход элемента И 46 соединен со сбросовым входом регистра сдвига 37.

Принцип работы предлагаемого устройства основан на переходе от дифференцированного анализа форм и параметров сигналов, поступающих из линии связи, к комплексному анализу свойств этих сигналов. Несложный дифференцированный параметрический анализ сигналов с квадратурной амплитудной модуляцией показывает, что количество параметров, характеризующих качество формируемых сигналов, модулированных многоуровневой квадратурной фазовой модуляцией, колеблется от 20 (с минимальным количеством комбинаций в кодах Треллиса) до 66 (при 32 комбинациях). Причем отклонение отдельного параметра, такого как нестабильность несущей частоты или нестабильность амплитуды, может вызвать искажения всех комбинационных составляющих. Использование традиционных методов параметрического контроля весьма проблематично из-за высоких временных и аппаратурных затрат, причем параметрический контроль такой значительной совокупности параметров невозможен в режиме реального времени.

На канал связи могут воздействовать внешние дестабилизирующие факторы, такие как аддитивная и мультипликативные помехи, обусловленные электромагнитной несовместимостью между каналом передачи информации и внешними электромагнитными устройствами, осуществляющими электромагнитные излучения в широком диапазоне частот. Внешние воздействия электромагнитных полей оказывают влияния на форму передаваемого сигнала, как в кабеле, так и в радиоканале. Также в канале связи может происходить искажение сигнала за счет несанкционированного доступа и попыток считывания информации. Полученный сигнал из канала связи поступает в модем на приемной стороне системы связи, выполняющий и дополнительную функцию формирователя эталонного принимаемого сигнала, так как модем является активным элементом, то есть помимо пассивной фильтрации и передачи цифровой информации на вход компьютера он осуществляет демодуляцию сигнала и восстановление исходной цифровой последовательности со стандартными значениями амплитуд, скоростей и фаз передаваемых видеосигналов.

Вероятность изменения математического ожидания случайного отклонения формы и параметров сигнала в случае воздействия внешней среды на канал связи крайне мала, так как для изменения математического ожидания сигнала необходимо длительное систематическое отклонение, а значит, что при индикации устройством состояния неисправности канала передачи данных и нахождении математического ожидания случайного отклонения формы и параметров сигнала в пределах допусков можно говорить о неисправности линии связи канала передачи данных, а в случае выхода математического ожидания за пределы допустимых значений искажение сигнала происходит в оконечной передающей аппаратуре.

Устройство работает следующим образом. Проходя по линии связи модулированный информационный сигнал после прохождения по кабелям претерпевает искажения, обусловленные влиянием внешней среды распространения на линию связи (шумов, изменений температуры, влажности и т.д.). Компьютер работает в симплексном режиме, то есть пока не будет принят кадр из канала связи, компьютер передавать свой информационный кадр в канал связи не будет. Заранее, перед началом работы, в регистр 7 вводится значение вероятности ошибочного приема элемента сигнала Рош, даваемое по техническому условию на контролируемый канал передачи данных, включающий в себя линию связи и оконечное передающее оборудование. Автоматический цикл контроля осуществляется в момент поступления на вход демодулятора 1.1 модулированного сигнала из линии связи. Модулированный искаженный информационный сигнал из линии связи Sк(t) поступает на вход демодулятора 1.1, где происходит его демодуляция, то есть несущая частота, модулированная определенной информационной импульсной кодовой последовательностью с помощью одной из видов модуляции (например, многоуровневой квадратурной модуляции), преобразуется в последовательность прямоугольных видеосигналов, с выхода демодулятора 1.1 поступающих параллельным кодом на вход компьютера. Одновременно параллельный сигнал поступает на входы элементов ИЛИ 4, ИЛИ-НЕ 5 и через линии задержки 25.1-25.n на первые входы элементов И 3.1-3.n. В этом случае на выходе элемента ИЛИ-НЕ 5 формируется логический ноль, а на выходе элемента ИЛИ 4 формируется логическая единица, которая подается на установочный вход триггера 6, тем самым обеспечивается на его выходе логическая «1», которая поступает на вторые входы элементов И 3.1-3.n и первый вход элемента И 20. Линии задержки 25.1-25.n задерживают параллельный демодулированный сигнал на время окончания переходных установочных процессов в элементах ИЛИ 4, ИЛИ-НЕ 5, триггере 6. Параллельный кодовый сигнал через линии задержки 25.1-25.n поступает на первые входы элементов И 3.1-3.n, проходит через них и поступает на параллельный вход модулятора 1.2. Модулятор 1.2 модулирует кодовый сигнал, который можно считать эталонным Sэ(t), так как он еще не испытал влияния отрицательных факторов среды распространения (линии связи). С выхода линии связи и с входа демодулятора 1.2 контролируемый сигнал S(к) поступает через управляемую линию задержки 26 на первые входы перемножителей 14.1 и 14.2. Управляемая линия задержки 26 будет задерживать сигнал до момента, когда на выходе ключа 27, подключенного к управляющему входу управляемой линии задержки 26, появится сигнал. Сигнал в управляемой линии задержки 26 будет задержан на время, необходимое для окончания переходных процессов в демодуляторе 1.1, элементах ИЛИ 4, ИЛИ-НЕ 5, триггере 6, элементах И 3.1-3.n, модуляторе 1.2, а также на время обработки полученного информационного сигнала в компьютере. С выхода модулятора 1.2 сигнал Sэ(t) поступает на вход ключа 27, с выхода которого на второй вход перемножителя 14.1 непосредственно и через фазовращатель 13, обеспечивающий получение сигнала, сопряженного по Гильберту с поступающим на его вход сигналом, на второй вход перемножителя 14.2. Ключ 27 открывается и пропускает сигнал с выхода модулятора, если на его управляющий вход поступает сигнал логической единицей с выхода триггера 6, то есть ключ 27 открывается на время прохождения модулированного искаженного информационного сигнала именно из линии связи Sк(i). Результаты перемножения с выходов перемножителей 14.1, 14.2 поступают на сигнальные входы интеграторов 15.1, 15.2, где происходит интегрирование на интервале времени, равном длительности модулированной кодовой последовательности. С выходов интеграторов 15.1, 15.2 сигналы поступают на входы квадраторов 16.1, 16.2, а затем с их выходов - на соответствующие входы сумматора 17. С выхода сумматора 17 сигнал поступает на информационный вход стробирующего блока 18, на управляющий вход которого при окончании получения кодовой последовательности демодулятором 1.1, с выхода элемента ИЛИ-НЕ 5 начало сформированной логической единицы является сигналом стробирования и данная логическая единица поступает на управляющие входы интеграторов 15.1, 15.2 для их сброса в нулевое состояние, с выхода стробирующего блока 18 сигнал поступает на вход нормирующего блока 19, состоящего из измерителя мощности эталонного сигнала Sэ(t) и делителя напряжения (не показаны, в соответствии с прототипом см. АС РФ №2071107, кл. 6 G05В 23/02), на другой вход нормирующего блока 19 поступает эталонный сигнал Sэ(t), на выходе нормирующего блока 19 будет присутствовать напряжение, представляющее собой результат измерения коэффициента взаимного различия контролируемого сигнала Sк(t) на входе демодулятора 1.1 из линии связи и эталонного сигнала Sэ(t) на выходе модулятора 1.2 в линию связи, описываемого следующим выражением:

где Sk(t), Sэ(t) - функции времени, определяющие структуру соответственно контролируемого и эталонного сигналов;

Sэ*(t) - функция времени, сопряженная по Гильберту с Sэ(t);

Pэ - мощность эталонного сигнала;

Т - длительность элемента эталонного сигнала.

Результат измерения g=G с выхода нормирующего блока 19 измерителя коэффициента взаимного различия 2 поступает на информационный вход аналого-цифрового преобразователя 12, откуда величина напряжения G, преобразованного в цифровую форму, поступает на первый вход компаратора 10. С выхода регистра 7 поступает ранее заданное значение Рош на второй вход элемента И 20, на первый вход которого поступает разрешающий сигнал с выхода триггера 6. С выхода элемента И 20 значение Рош поступает на вход удвоителя 21, в удвоителе 21 значение Рош удваивается и с выхода удвоителя 21 поступает на вход квадратора 22, где происходит возведение в квадрат удвоенного значения Рош, с выхода квадратора 22 полученное значение поступает на вход логарифмического устройства 23, с выхода которого сигнал поступает на второй вход делителя 24, на первый вход которого поступает сигнал, определяющий значение h2 с выхода блока измерения энергии сигнала к спектральной плотности шума (h2).

На выходе делителя 24 будет присутствовать кодовая комбинация, представляющая собой результат измерения порогового значения КВР для данной вероятности ошибки Рош исследуемого канала

С выхода делителя 24 значение gпор поступает на второй вход компаратора 10, где происходит сравнение значений g и gпор. В зависимости от полученного результата g<gпор, g=gпор, g>gпор на одном из трех соответствующих выходах компаратора 10 появится единица, которая поступает на один из входов блока 11 вывода результатов контроля (для индикации информации «Оценка: годен», «Оценка: предельное значение», «Оценка: негоден»). Принимается решение, что совокупность параметров линии связи, определяющих значение коэффициента взаимного различия g, находится в норме или не в норме, и совокупность отклонений значений этих параметров от номинальных значений не дает вероятность ошибки больше заданной, меньше заданной или равной заданной.

В случае когда получен результат g>gпор, на соответствующем выходе компаратора 11 формируется логическая единица, которая поступает на сбросовый R вход триггера 34, и тем самым обеспечивается логический нуль на выходе триггера 34. Если же полученный результат g<gпор или g=gпор, то на одном из соответствующих выходов компаратора 11 формируется логическая единица, которая поступает на один из входов элемента ИЛИ 28, и на выходе элемента ИЛИ 28 формируется логическая единица, которая поступает на установочный S вход триггера 34, тогда на выходе триггера 34 формируется логическая единица, которая поступает на входы элементов И 29 и И 30, то есть она является разрешающей. На другой вход элемента И 29 поступает величина g с выхода АЦП 12, а на вход элемента И 30 поступает значение gпор с выхода делителя 24. В случае формирования разрешающей логической единицы с выхода триггера 34 устройство для вычисления математического ожидания 31 вычисляет математическое ожидание величины g, а устройство для вычисления математического ожидания 32 - математическое ожидание величины gпор. Причем gпор будет флуктуировать по причине изменения величины спектральной плотности шума, поступающей на вход делителя 24. Далее в компараторе 33 происходит сравнение полученных математических ожиданий. В случае когда отклонение математического ожидания g от gпор выше допустимого, на первом выходе компаратора 33 формируется логическая единица, которая поступает на соответствующий вход блока вывода результатов контроля 11 для индикации информации: «Неисправна оконечная передающая аппаратура канала передачи данных», а в случае когда отклонение математического ожидания g от gпор в пределах допусков, на втором выходе компаратора 33 формируется логическая единица, которая поступает на соответствующий вход блока вывода результатов контроля 11 для индикации информации: «Неисправна линия связи канала передачи данных». Устройства для вычисления математического ожидания работают в моменты поступления сигналов на их входы, а в остальное время работы всего устройства находятся в режиме ожидания, так как для вычисления математического ожидания случайного отклонения формы и параметров сигнала необходимо использование большого промежутка времени, и чем больше промежуток времени, тем точнее будут результаты вычисления математического ожидания случайного отклонения формы и параметров сигнала, а значит, и результат работы всего устройства будет точнее.

Устройство для вычисления математического ожидания (фигура 2) работает следующим образом. На управляющий вход поступает логическая единица, а на информационный вход устройства поступает цифровая последовательность чисел, которая также поступает на входы элементов ИЛИ 35, инвертора 36 и регистра сдвига 38. На вход регистра сдвига 37 поступают всегда логические единицы, а регистр сдвига 38 заполняется исходной цифровой последовательностью. В момент, когда последний разряд регистра сдвига 37 заполняется логической единицей, эта логическая единица с последнего разряда регистра сдвига 37 поступает на вход счетчика 43, также поступает на свой сбросовый вход и поступает на входы группы элементов И 39.1-39.m, тем самым позволяя значениям разрядов регистра сдвига 38 параллельно поступить на входы соответствующих сумматоров. Разрядность регистров 37 и 38 одинакова, а разрядность регистра 41 должна быть больше разрядности регистров 37 и 38. Это связано с тем, что регистр может переполниться, а значит, чем больше разрядность регистра 41, тем выше будет максимально возможная длительность вычисления математического ожидания. Количество сумматоров 40.1-40.m-40.n превосходит количество элементов И 39.1-39.m и равно количеству разрядов регистра 41. Сумматоры 40.1-40.m-40.n выполняют сложение значений разрядов регистра 41 и значений, поступающих с элементов И 39.1-39.m, учитывая при этом переносы значений в старшие разряды. Результаты сложения записываются в регистр 41 и поступают на входы делителя 43, где по сути происходит вычисление среднего арифметического значения g или gпор, то есть вычисление математического ожидания. В случае когда последний разряд регистра 41 равен единице и на вход, соответствующий переносам, сумматора 40.n поступает логическая единица, считается, что регистр 41 переполнился, и на выходе элемента И 44 формируется логическая единица, которая поступает на сбросовый вход регистра 41 и на сбросовый вход счетчика 42, то есть происходит обнуление регистра 41 и счетчика 42. Вычисления начинаются заново. В случае когда на управляющий вход будет поступать логический ноль, вычисления производиться не будут.

Технический результат заключается в контроле уже не только линии связи канала передачи данных, но и всего канала передачи данных в целом, что позволяет повысить достоверность контроля канала передачи данных.

Устройство для автоматизированного контроля линии связи канала передачи данных, содержащее модем, состоящий из демодулятора и модулятора, измеритель коэффициента взаимного различия (ИКВР), состоящий из двух перемножителей, фазовращателя, двух интеграторов, двух квадраторов, сумматора, стробирующего блока и нормирующего блока, группу элементов И, элемент ИЛИ, элемент ИЛИ-НЕ, триггер, регистр, блок измерения отношения энергии сигнала к спектральной плотности шума, измеритель порогового значения коэффициента взаимного различия, состоящий из элемента И, удвоителя, квадратора, логарифмирующего устройства, делителя; компаратор, блок вывода результатов контроля, группу линий задержки, аналого-цифровой преобразователь, управляемую линию задержки, ключ, отличающееся тем, что с целью повышения достоверности контроля качества линии связи канала передачи данных и оконечного передающего оборудования, являющихся составными частями канала передачи данных, дополнительно введены элемент ИЛИ, два элемента И, RS-триггер, компаратор, два устройства для вычисления математического ожидания, состоящие из двух элементов ИЛИ, двух инверторов, регистра, двух регистров сдвига, группы элементов И, группы сумматоров, счетчика, делителя, элемента И, причем входы элемента ИЛИ подключены к первому и второму выходам первого компаратора, сравнивающего коэффициент взаимного различия с пороговым значением коэффициента взаимного различия (КВР), а выход элемента ИЛИ подключен к установочному S входу RS-триггера, сбросовый R вход которого соединен с третьим выходом первого компаратора, сравнивающего коэффициент взаимного различия с пороговым значением КВР, а выход RS-триггера соединен с первыми входами двух элементов И и управляющими входами устройств для вычисления математического ожидания, причем второй вход первого из них соединен с выходом аналого-цифрового преобразователя и с первым входом первого компаратора, а второй вход второго из них соединен с выходом измерителя порогового значения КВР и со вторым входом первого компаратора, а выход каждого из элементов И соединен с входами соответствующих им устройств для вычисления математического ожидания, причем выходы устройств для вычисления математического ожидания подключены к входам компаратора, сравнивающего математическое ожидание флуктуации коэффициента взаимного различия и математическое ожидание флуктуации порогового значения КВР, а выходы компаратора, сравнивающего математические ожидания, подключены к четвертому и пятому входам блока вывода результатов контроля, причем вход устройства для вычисления математического ожидания является входом первого инвертора, первым входом первого элемента ИЛИ и входом первого регистра сдвига, которые являются составными компонентами устройства для вычисления математического ожидания, причем выход первого инвертора соединен со вторым входом первого элемента ИЛИ, выход которого соединен с входом второго регистра сдвига, выход которого соединен с входом счетчика, с первым входом второго элемента ИЛИ и со вторыми входами группы элементов И, причем первые входы группы элементов И соединены с соответствующими выходами первого регистра сдвига, а выходы группы элементов И соединены с соответствующими входами группы сумматоров, вторые входы которых соединены с соответствующими выходами регистра, также сумматоры соединены последовательно между собой для осуществления переносов значений в старшие разряды, причем вход, служащий для осуществления переноса в старший разряд, последнего сумматора соединен с первым входом элемента И, второй вход которого соединен с последним выходом регистра, а выход элемента И соединен со сбросовым входом регистра и со сбросовым входом счетчика, а выходы сумматоров соединены с соответствующими входами регистра и с соответствующими входами делителя, другой вход которого соединен с выходом счетчика, а выход делителя является выходом устройства для вычисления математического ожидания; управляющие входы устройств для вычисления математического ожидания соединены с входом второго инвертора, выход которого соединен со вторым входом элемента И, причем выход элемента И соединен со сбросовым входом второго регистра сдвига.