Цифровой демодулятор сигналов с относительной фазовой манипуляцией

Иллюстрации

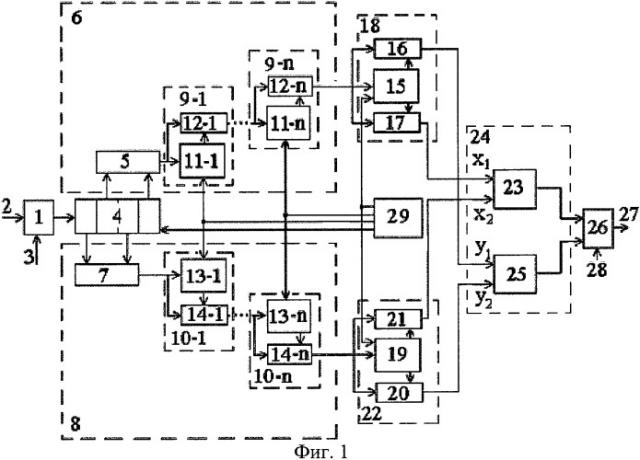

Показать всеИзобретение относится к области радиотехники и может быть использовано в устройствах приема цифровых информационных сигналов для цифровой демодуляции двоичных сигналов с относительной фазовой манипуляцией (ОФМ). Достигаемый технический результат - обеспечение высокоскоростной цифровой демодуляции сигналов с ОФМ. Цифровой демодулятор сигналов с относительной фазовой манипуляцией содержит аналого-цифровой преобразователь, регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки сигналов, первый и второй формирователи отклика канала на элементы сигнала с ОФМ, содержащие сумматор, вычитатель и регистр сдвига многоразрядных кодов, первый и второй квадратичные преобразователи и решающее устройство. 4 ил.

Реферат

Изобретение относится к области радиотехники и может быть использовано в устройствах приема цифровых информационных сигналов для цифровой демодуляции двоичных сигналов с относительной фазовой манипуляцией (ОФМ).

Известно устройство демодуляции сигналов с относительной фазовой модуляцией (см. Спилкер Дж. «Цифровая спутниковая связь». Пер. с англ. / Под ред. В.В. Маркова. М.: Связь, 1979). Устройство состоит из двух корреляторов, двух блоков стробирования, а также из блока вычисления функции arctg, решающего блока, генератора опорного колебания, фазовращателя и генератора тактовых импульсов.

Близким к предлагаемому устройству является демодулятор (А.с. 2099892. Способ демодуляции сигналов с относительной фазовой модуляцией и устройство для его осуществления), в который дополнительно введены входной фильтр и блок формирования оценки фазы.

Эти устройства осуществляют квадратурную корреляционную обработку входного сигнала с последующим сравнением фаз соседних информационных элементов.

К недостаткам известных устройств следует отнести:

- сложность реализации высокоскоростных корреляторов и нелинейного преобразователя (с функцией arctg) как в аналоговой, так и в цифровой форме;

- необходимость выполнения большого числа арифметических операций на каждый поступивший отсчет сигнала, что требует использования высокоскоростных вычислителей.

Наиболее близким по технической сущности и внутренней структуре к предлагаемому устройству является цифровой обнаружитель узкополосных сигналов (патент RU 2257671 C1, H04B 1/10, 27.07.2005, Бюл. №21, авторы Глушков А.Н., Литвиненко В.П., Проскуряков Ю.Д.), способный выполнять функции амплитудного демодулятора (детектора).

Его недостатком является отсутствие возможности высокоскоростной демодуляции фазоманипулированных сигналов.

Задачей предлагаемого технического решения является обеспечение высокоскоростной цифровой демодуляции сигналов с относительной фазовой манипуляцией.

Поставленная задача решается тем, что цифровой обнаружитель узкополосных сигналов, содержащий аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов, дополнительно содержит первый и второй формирователи отклика канала (ФОК) на элементы сигнала с ОФМ, первый и второй квадратичные преобразователи (КП) и решающее устройство (РУ). Каждый ФОК содержит сумматор, вычитатель и регистр сдвига многоразрядных кодов, входы которых соединены вместе и образуют общий вход ФОК, выход регистра сдвига соединен с вторыми входами сумматора и вычитателя, а выходы сумматора и вычитателя образуют суммарный и разностный выходы ФОК. Выход каждого ККО соединен с входом соответствующего ФОК. Суммарный выход первого ФОК и разностный выход второго ФОК подключены к входам первого КП, вычисляющего сумму квадратов соответствующих отсчетов, аналогично суммарный выход второго ФОК и разностный выход первого ФОК подключены к входам второго КП. Выходы двух КП соединены с входами решающего устройства (РУ), формирующего выходной сигнал демодулятора.

Предлагаемое техническое решение поясняется чертежами.

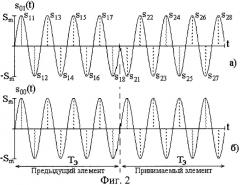

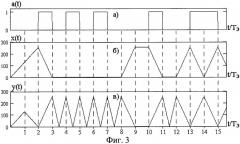

На фиг.1 представлена структурная схема предлагаемого устройства, на фиг.2 - процесс квантования, а на фиг.3 - результаты моделирования работы демодулятора при обработке сигнала с ОФМ.

Устройство содержит АЦП 1, на вход которого поступает принимаемый сигнал 2 с выхода усилителя промежуточной частоты приемника, а на управляющий вход тактовые импульсы 3. Выход АЦП 1 соединен с входом регистра 4 сдвига многоразрядных кодов на четыре отсчета, четные выходы которого соединены с соответствующими входами вычитателя 5 первого ККО 6, а нечетные выходы - с соответствующими входами вычитателя 7 второго ККО 8. Каждый ККО помимо вычитателя содержит n каскадно соединенных блоков накопления отсчетов (БНО). Количество БНО n зависит от числа N периодов сигнала в информационном символе и определяется двоичным логарифмом N {n=log2N). Такое построение устройства обеспечивает минимальное количество БНО, при этом число обрабатываемых периодов сигнала равно N=2n.

Первый ККО 6 содержит последовательно соединенные БНО 9-1, …, 9-n, а второй ККО 8 - последовательно соединенные БНО 10-1, …, 10-n. Каждый из БНО состоит из регистра сдвига многоразрядных кодов и сумматора. Блоки 9-1, …, 9-n накопления отсчетов содержат регистры 11-1, …, 11-n сдвига многоразрядных кодов и сумматоры 12-1, …, 12-n соответственно, а БНО 10-1, …, 10-n - соответственно регистры 13-1, …, 13-n сдвига многоразрядных кодов и сумматоры 14-1, …, 14-n. В каждом блоке 9 (10) накопления отсчетов первый вход регистра 11 (13) сдвига является входом блока 9 (10) накопления отсчетов. Второй вход сумматора 12 (14) соединен с выходом регистра 11 (13) сдвига. Выход сумматора 12 (14) является выходом блока 9 (10) накопления отсчетов, а тактовый вход регистра 11 (13) сдвига является управляющим входом блока 9 (10) накопления отсчетов. Выход вычитателя 5 соединен с входом блока 9-1 накопления отсчетов ККО 6, а выход блока 9-n накопления отсчетов ККО 6 - с первым входом регистра сдвига многоразрядных кодов 15, первым входом вычитателя 16 и первым входом сумматора 17 ФОК 18, а тактовый вход регистра сдвига многоразрядных кодов 15 является управляющим входом ФОК 18. Первый выход регистра 15 сдвига многоразрядных кодов первого ФОК 18 соединен со вторым входом вычитателя 16 и вторым входом сумматора 17. Выход вычитателя 7 соединен с входом БНО 10-1 ККО 8, а выход БНО 10-n ККО 8 - с первым входом регистра сдвига многоразрядных кодов 19, первым входом вычитателя 20 и первым входом сумматора 21 ФОК 22, а тактовый вход регистра сдвига многоразрядных кодов 19 является управляющим входом ФОК 22. Первый выход регистра сдвига многоразрядных кодов 19 соединен со вторым входом вычитателя 20 и вторым входом сумматора 21. Выход сумматора 17 ФОК 18 ККО 6 соединен с первым входом квадратичного преобразователя 21, а выход сумматора 19 ФОК 20 ККО 8 - со вторым входом квадратичного преобразователя 23 блока квадратичных вычислений 24. Выход вычитателя 16 ФОК 18 ККО 6 соединен с первым входом квадратичного преобразователя 25, а выход вычитателя 20 ФОК 22 ККО 8 - со вторым входом квадратичного преобразователя 25 блока квадратичных вычислений 24. Выход квадратичного преобразователя 23 блока квадратичных вычислений 24 соединен с первым входом решающего устройства 26, а выход квадратичного преобразователя 25 блока квадратичных вычислений 24 - со вторым входом решающего устройства 26, выход которого является выходом 27 цифрового демодулятора. На управляющий вход решающего устройства 26 поступают тактовые синхроимпульсы 28 от генератора синхронизирующих импульсов 29. Управляющие входы АЦП 1, регистра 4 сдвига многоразрядных кодов на четыре отсчета, блоков 9 (10) накопления отсчетов, ФОК 18 (22) соединены с соответствующими входами генератора 29 синхронизирующих импульсов.

Устройство работает следующим образом.

Входной сигнал с ОФМ на входе 2 демодулятора вида s(t)=Smsin(2πf0t+a(t)π+φ0), где Sm - амплитуда, f0 - несущая частота, φ0 - начальная фаза, a(t) - двоичный модулирующий фазу сигнал со значениями 0 или 1, поступает на вход аналого-цифрового преобразователя (АЦП) 1, который формирует по четыре отсчета входного сигнала на период повторения T=1/f0 в соответствии с тактовыми импульсами 3 от генератора 29. Информационный элемент сигнала длительностью ТЭ содержит N периодов T несущего колебания, N=2n, n - целое число.

Процесс квантования показан на фиг.2 пунктирными линиями для двух последовательных информационных элементов длительностью ТЭ (Т=4) с изменением фазы s01(t) и с непрерывной фазой s00(t). В этом примере сигналы относятся к одному из квадратурных каналов в случае, когда в другом канале отсчеты сигнала равны нулю (точки квантования соответствуют моментам перехода сигнала через ноль). Результаты работы устройства не зависят от величины начальной фазы φ0 сигнала с ОФМ.

На вход вычитателя 5 сначала поступают отсчеты s11 и s12, (s12<0, фиг.2), а на его выходе формируется сумма s11-s11=Sm-(-Sm)=2Sm, которая запоминается в регистре 11. В следующем периоде сигнала на выходе вычитателя 5 получим величину s13+s14=2Sm (фиг.2), а на выходе сумматора 12-1 - s11+s12+s13+s14=4Sm. После поступления N периодов входного сигнала при отсутствии помех на выходе сумматора 12-n получим результат R1=s11+s12+…+s1,2N=2NSm обработки 2N отсчетов информационного элемента длительностью ТЭ.

Далее принимается следующий информационный элемент и в сумматоре 12-n накапливается сумма отсчетов R2=s21+s22+…+s2,2N=2NSm со знаком минус для сигнала, показанного на фиг.2а, и плюс - на фиг.2б. Аналогичная сумма R1 для предыдущего информационного элемента продвигается на выход регистра сдвига 15. После поступления второго информационного элемента на выходе вычитателя 16 получим величину y1=R2-R1, а на выходе сумматора 17 соответственно x1=R2+R1. Если при отсутствии помех передавался сигнал, показанный на фиг.2а, то y1=4NSm, а х1=0, а для сигнала на фиг.2б соответственно y1=0, а х1=4NSm.

В предлагаемом демодуляторе за один период сигнала необходимо выполнить всего 2(log2N+3) операций сложения/вычитания многоразрядных кодов и запоминать 4N полученных значений. Обеспечивается минимум арифметических операций на период сигнала для решения поставленной задачи и, следовательно, высокая скорость обработки сигнала с ОФМ. Технически устройство может быть реализовано либо как специализированная интегральная схема, либо как микропроцессорное устройство. Регистры сдвига многоразрядных кодов могут выполняться на базе однобитовых регистров сдвига либо оперативных запоминающих устройств.

На фиг.3 показаны результаты моделирования работы демодулятора при обработке сигнала с ОФМ при модулирующем сигнале a(t) (фиг.3а) для N=64 в зависимости от нормированного времени t/ТЭ. Целочисленные значения t/ТЭ определяют границы информационных элементов (моменты тактовой синхронизации). Интервал t/ТЭ от 0 до 2 соответствует переходному процессу заполнения регистров сдвига многоразрядных кодов. На фиг.3б и фиг.3в представлены зависимости от времени откликов и каналов обработки двух соседних информационных элементов с совпадающими и противоположными фазами соответственно при отсутствии помех. В точке t/ТЭ=2 получим x=4N=256, а y=0, то есть два предыдущих информационных элемента имели одинаковую фазу, при t/ТЭ=3 наоборот x=0, а y=4N=256, следовательно два предыдущих элемента имели противоположные фазы и т.д. Как видно, предлагаемый демодулятор полностью реализует свойство ортогональности сигнала с бинарной ОФМ.

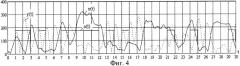

На фиг.4 показаны результаты статистического имитационного моделирования демодулятора сигнала и ОФМ при наличии шумовых помех при N=64 с учетом влияния узкополосного тракта приемника (оно проявляется и в небольшом смещении откликов каналов относительно модулирующего сигнала на фиг 4).

Расчеты показывают, что в канале с независимыми отсчетами нормального шума с нулевым средним значением и дисперсией вероятность ошибки определяется выражением

где h2 - отношение сигнал/шум на входе демодулятора, что совпадает с потенциальной помехоустойчивостью процедуры некогерентной обработки сигналов с активной паузой [4].

Литература

1. Спилкер Дж. Цифровая спутниковая связь. Пер. с англ. / Под ред. В.В. Маркова. М. Связь, 1979.

2. А.с. 2099892. Способ демодуляции сигналов с относительной фазовой модуляцией и устройство для его осуществления.

3. Патент RU 2257671 C1, H04B 1/10, 27.07.2005 «Цифровой обнаружитель узкополосных сигналов», Бюл. №21, авторы Глушков А.Н., Литвиненко В.П., Проскуряков Ю.Д.

4. Финк Л.М. Теория передачи дискретных сообщений. М., «Сов. Радио», 1970.

Цифровой демодулятор сигналов с относительной фазовой манипуляцией (ОФМ), содержащий аналого-цифровой преобразователь (АЦП), регистр сдвига многоразрядных кодов на четыре отсчета, первый и второй n-каскадные каналы квадратурной обработки (ККО) сигналов, отличающийся тем, что он дополнительно содержит первый и второй формирователи отклика канала (ФОК) на элементы сигнала с ОФМ, первый и второй квадратичные преобразователи (КП) и решающее устройство (РУ), при этом каждый ФОК содержит сумматор, вычитатель и регистр сдвига многоразрядных кодов, входы которых соединены вместе и образуют общий вход ФОК, выход регистра сдвига соединен с вторыми входами сумматора и вычитателя, а выходы сумматора и вычитателя образуют суммарный и разностный выходы ФОК, кроме того, выход каждого ККО соединен с входом соответствующего ФОК, а суммарный выход первого ФОК и разностный выход второго ФОК подключены к входам первого КП, вычисляющего сумму квадратов соответствующих отсчетов, аналогично суммарный выход второго ФОК и разностный выход первого ФОК подключены к входам второго КП, выходы двух КП соединены с входами решающего устройства (РУ), формирующего выходной сигнал демодулятора.