Пиковый детектор

Иллюстрации

Показать всеИзобретение относится к импульсной технике и может быть использовано в устройствах автоматики и силовой техники для детектирования, а также для определения канала с экстремальным напряжением и его полярности. Техническим результатом заявленного изобретения выступает расширение функциональных возможностей, за счет изменения структуры схемы и введения дополнительных элементов происходит выделение не только максимального пикового значения из k входных каналов, но и полярности и номера канала с максимальной амплитудой. Технический результат достигается благодаря тому, что пиковый детектор содержит шину питания, две входные шины, два блока сравнения напряжений и сравнения токов, аналоговый ключ, n-p-n-транзистор, конденсатор, резистор, повторитель напряжения, первую выходную шину, второй резистор, первый диод, управляющий вход, четыре вторых диода, четыре схемы задержки импульса, вторую выходную шину, третий резистор, логический элемент ИЛИ, формирователь коротких импульсов, четыре RS-триггера, преобразователь кода в напряжение. 2 ил.

Реферат

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и силовой техники для детектирования, а также для определения канала с экстремальным напряжением и его полярности.

Известно устройство для определения канала с экстремальным напряжением (G06G 7/02, SU №1385130 А1, БИ №12, 1988 г, авторов Воронова В.Г., Гунбина М.В.), содержащее n компараторов, первые входы которых являются входами устройства, вторые входы соединены с выходом интегрирующего фильтра, а выходы соединены с входами элемента ИЛИ, источник опорных напряжений, выходы положительного и отрицательного напряжений которого через переключатель соединены с входом интегрирующего фильтра, запоминающий регистр и формирователь импульса, вход которого соединен с выходом положительного напряжения источника опорных напряжений, а выход - с входом обнуления регистра, выход элемента ИЛИ соединен с управляющим входом переключателя и входом управления записью запоминающего регистра, а выходы n компараторов соединены каждый с входом соответствующего разряда запоминающего регистра, кодовый выход которого является выходом устройства.

Недостатками известного устройства являются ограниченные функциональные возможности из-за:

- невозможности определения полярности экстремального напряжения, т.к. компараторы его работают с положительным сигналом;

- отсутствия функции пикового детектора, т.к. его интегрирующий фильтр не обеспечивает функцию элемента аналоговой памяти;

- невозможность сжатия информации из-за отсутствия указателя номера канала с экстремальным напряжением, т.к. кодовые выходы запоминающего регистра обеспечивают многоразрядный цифровой код.

Наиболее близким по технической сущности к заявляемому изобретению является пиковый детектор (патент РФ №2409818 приоритет от 22.06.2009 авторов Гутникова А.И., Давлетчина Д.З., Пикаевой Л.А., МПК G01R 19/04 опубликовано 20.01.2011), содержащий шину питания, k входных шин, где k=1, 2, …, и k блоков сравнения напряжений и сравнения токов (БСНиСТ), включающих в себя компараторы напряжений, аналоговый ключ, n-p-n-транзистор, повторитель напряжения, первые диод, конденсатор и резистор, вторые диоды, второй, третий и четвертый резисторы, пороговый элемент, третий диод, триггер Шмитта, схемы задержки, включающие в себя интегрирующие цепи.

Каждая входная шина соединена с первым входом соответствующего блока сравнения напряжений и сравнения токов. Первый выход аналогового ключа соединен с общей шиной, а второй выход соединен с эмиттером n-p-n-транзистора, через последовательно соединенные первые конденсатор и резистор с общей шиной и с входом повторителя напряжения, выход которого соединен с выходной шиной, со вторыми входами БСНиСТ, входом порогового элемента и через второй резистор с базой n-p-n-транзистора и анодом первого диода. Катод первого диода соединен с управляющим входом аналогового ключа и выходом триггера Шмитта, вход которого соединен через второй конденсатор с общей шиной и через третий резистор с анодом третьего диода и первым выводом четвертого резистора, второй вывод которого соединен с катодом третьего диода и выходом порогового элемента. Каждый выход каждого БСНиСТ соединен с анодом соответствующего второго диода и входом соответствующей схемы задержки импульса. Шина питания соединена с коллектором n-p-n-транзистора, база которого соединена с объединенными катодами вторых диодов.

Недостатками пикового детектора являются:

- невозможность определения полярности экстремального напряжения из-за особенностей структуры схемы;

- невозможность определения номера канала с экстремальным напряжением из-за особенностей структуры схемы;

- наличие ложного импульса на выходе пикового детектора из-за произвольного состояния аналогового ключа при включении питания.

Технический результат, на достижение которого направлено изобретение, заключается в расширении функциональных возможностей.

Данный технический результат достигается тем, что в пиковом детекторе, содержащем шину питания, k входных шин, каждая из которых соединена с первым входом соответствующего БСНиСТ, где k=1, 2, …, аналоговый ключ, первый выход которого соединен с общей шиной, а второй выход соединен с эмиттером n-p-n-транзистора, через последовательно соединенные конденсатор и первый резистор с общей шиной и с входом повторителя напряжения, выход которого соединен с первой выходной шиной, со вторыми входами БСНиСТ и через второй резистор с базой n-p-n-транзистора и анодом первого диода, катод которого соединен с управляющим входом аналогового ключа, выходы каждого БСНиСТ соединены с анодом соответствующего второго диода и входом соответствующей схемы задержки импульса, шина питания соединена с коллектором n-p-n-транзистора, новым является то, что дополнительно введены вторая выходная шина, третий резистор, логический элемент ИЛИ, формирователь коротких импульсов (ФКИ), 2k RS-триггеров, преобразователь кода в напряжение (ПКН), выход каждой схемы задержки импульса соединен с соответствующим S-входом соответствующего RS-триггера, выходы каждого БСНиСТ соединены с соответствующим входом логического элемента ИЛИ, выход которого через формирователь коротких импульсов соединен с объединенными R-входами RS-триггеров, выходы которых через ПКН соединены со второй выходной шиной, база n-p-n-транзистора через третий резистор соединена с объединенными катодами вторых диодов.

Расширенные функциональные возможности обеспечиваются за счет:

- возможности определения полярности экстремального напряжения и номера канала с экстремальным напряжением из-за изменения структуры схемы, в которой вновь введенный третий резистор и компараторы из состава БСНиСТ обеспечили нормированными логическими уровнями вновь введенные логический элемент ИЛИ и S-входы 2k RS-триггеров. Отмечено, что при выделении экстремального значения на выходах компараторов БСНиСТ образуется унитарный код, позволяющий выделить как номер входа с экстремальным напряжением, так и его полярность, из-за общего повторителя напряжения в цепи обратной связи всех компараторов БСНиСТ пикового детектора. Благодаря введенному периодическому сбросу в нуль конденсатора пикового детектора в совокупности с вышеуказанными признаками, возникает режим отслеживания экстремального из входных напряжений на участке после очередного сброса в нуль конденсатора, причем в каждом цикле переключений срабатывают любые компараторы БСНиСТ, что обнуляет все RS-триггеры через логический элемент ИЛИ и ФКИ. Последующая с задержкой установка в единицу по S-входу одного из RS-триггеров соответствует номеру входной шины с максимальной амплитудой и с заданной полярностью и осуществляется с одного из компараторов БСНиСТ, имеющего на входе максимальную амплитуду. При этом остальные компараторы БСНиСТ с меньшей амплитудой на входе сброшены в нуль по цепи обратной связи. Устойчивая работа RS-триггеров обеспечивается схемой задержки, при этом сначала производится их установка в нуль, а затем установка в единицу с задержкой. Наличие единицы в унитарном коде на одном из входов преобразователя кода в напряжение (на остальных входах нули) с одного из многих выходов 2k RS-триггеров обеспечивает аналоговое напряжение по одной второй шине, чем обеспечено сжатие информации;

- отсутствия ложного импульса на выходе пикового детектора из-за обеспечения нулевого состояния аналогового ключа при включении питания одиночным импульсом по шине установки нуля или по управляющему входу аналогового ключа.

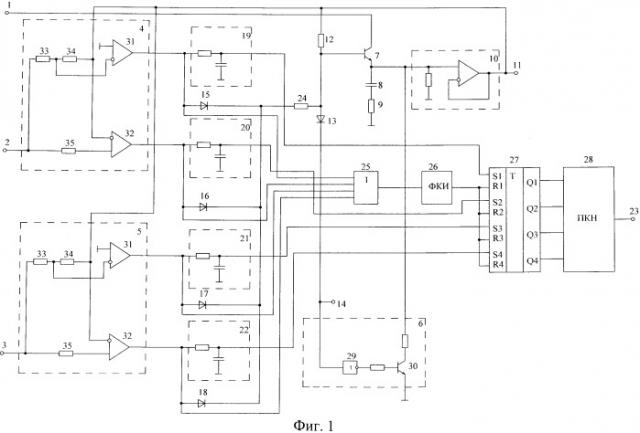

На фиг.1 представлен пример реализации функциональной схемы пикового детектора при k=2. На фиг.2 приведены временные диаграммы работы пикового детектора.

Пиковый детектор (фиг.1) содержит шину 1 питания, две входные шины 2 и 3, два БСНиСТ 4, 5 (с двумя выходами каждый), аналоговый ключ 6, n-p-n-транзистор 7, конденсатор 8, первый резистор 9, повторитель напряжения 10, первую выходную шину 11, второй резистор 12, первый диод 13, управляющий вход 14 аналогового ключа 6, вторые диоды 15, 16, 17, 18, схемы задержки импульса 19, 20, 21, 22, вторую выходную шину 23, третий резистор 24, логический элемент ИЛИ 25, ФКИ 26, четыре независимых RS-триггера 27, ПКН 28. Входные шины 2 и 3 соединены с первыми входами БСНиСТ 4, 5 соответственно. Первый выход аналогового ключа 6 соединен с общей шиной, а второй выход соединен с эмиттером n-p-n-транзистора 7 и с входом повторителя напряжения 10, а через последовательно соединенные конденсатор 8 и первый резистор 9 с общей шиной. Выход повторителя напряжения 10 соединен с первой выходной шиной 11, со вторыми входами БСНиСТ 4, 5 и через второй резистор 12 с базой n-p-n-транзистора 7 и анодом первого диода 13. Катод диода 13 соединен с управляющим входом 14 аналогового ключа 6, выходы каждого БСНиСТ 4, 5 соединены с анодами вторых диодов 15, 16 и 17, 18 соответственно и входом соответствующей схемы задержки импульса 19, 20, 21, 22. Шина питания 1 соединена с коллектором n-p-n-транзистора 7. Выход каждой схемы задержки импульса 19, 20, 21, 22 соединен с соответствующим S-входом RS-триггеров 27. Выходы каждого БСНиСТ 4, 5 соединены с соответствующими входами логического элемента ИЛИ 25, выход которого через ФКИ 26 соединен с объединенными R-входами RS-триггеров 27, выходы которых через ПКН 28 соединены со второй выходной шиной 23. База n-p-n-транзистора 7 через третий резистор 24 соединена с объединенными катодами вторых диодов 15, 16, 17, 18.

ПКН 28 выполнен на стандартном цифро-аналоговом преобразователе. ФКИ выполнен на дифференцирующей RC-цепи.

Аналоговый ключ 6 выполнен на последовательно соединенных логическом элементе НЕ 29, вход которого является неинвертирующим управляющим входом 14 аналогового ключа 6, и разрядном ключе с общим эмиттером на n-p-n-транзисторе 30.

Схема задержки импульса 19, 20, 21, 22 однотипна, каждая выполнена на интегрирующей RC-цепи, вход которой является входом, выход которой является выходом схемы задержки импульса 19, 20, 21, 22. Применимы и активные схемы задержки импульса, выполненные на последовательно соединенных логических элементах или специальных микросхемах.

БСНиСТ 4, 5 однотипны, каждый выполнен на двух дифференциальных компараторах напряжения (ДКН) 31, 32. Неинвертирующий вход компаратора 31 подключен к общей шине, инвертирующий вход компаратора 31 подключен к точке объединения резисторов 33, 34. Второй вывод резистора 33 является первым входом БСНиСТ 4, 5 и подключен через резистор 35 к неинвертирующему входу компаратора 32. Второй вывод резистора 34 является вторым входом БСНиСТ 4, 5 и подключен к инвертирующему входу компаратора 31.

Положительные выводы питания БСНиСТ 4, 5 и повторителя напряжения 10 подключены к общей шине 1 питания, а отрицательные их выводы питания - к общей шине (на фиг. не показано).

На фигуре 2 представлены временные диаграммы работы пикового детектора (фиг.2), где:

U2, U3 - разнополярные импульсы напряжений широкого диапазона амплитуд и длительности на входных шинах 2 и 3, начиная с момента t1 до момента t9;

U14 - периодические импульсы длительностью Сброса на управляющем входе 14 для сброса в 0 конденсатора 8 пикового детектора после считывания информации в запоминающее устройство (на фиг.1 не показано);

U11 - выходные импульсы на шине 11, равные максимальным амплитудам импульсов с входных шин 2 и 3, расширенные по длительности до заданной временем записи запоминающего устройства (на фиг.1 не показано) txpah;

U23 - выходные импульсы на шине 23, отражающие полярность максимальных импульсов и номер входной шины 2, 3, содержащей максимальный по амплитуде импульс в моменты t1, t4, t5, t6, t7, t8, t9.

Пиковый детектор работает следующим образом.

В исходном статическом состоянии до момента t0 на фиг.2 напряжение на входных шинах 2, 3 равно нулю, на шину 1 питание подано. Нулевым уровнем на шине управления 14 аналогового ключа 6 конденсатор 8 разряжен практически до нулевого (несколько милливольт) напряжения. ДКН 31, 32 находятся в состоянии логического нуля по выходу за счет небольшого (несколько милливольт) напряжения смещения на их инвертирующих входах, образуемого входным вытекающим током смещения повторителя напряжения 10, протекающим по его большому входному сопротивлению. На выходах компараторов БСНиСТ 4, 5 и выходе логического элемента ИЛИ 25 логический ноль. На выходе ФКИ 26 и на объединенных R-входах RS-триггеров 27 логический ноль. Одиночным импульсом положительной полярности по шине R установки нуля (на фиг.1 не показано) RS-триггеры 27 установлены в нуль по прямым Q-выходам, чем обеспечено нулевое напряжение на выходе ПКН 28 и выходной шине 23.

На объединенные катоды диодов 15, 16 и 17, 18, базу n-p-n-транзистора 7 через резистор 12 также подано «нулевое» (несколько милливольт) напряжение с выхода повторителя напряжения 10.

При отрицательной полярности входного сигнала на входных шинах 2, 3 для ограничения сигналов на компараторах 32 БСНиСТ 4, 5 устанавливаются резисторы 35. Схемы задержки импульса 19, 20, 21, 22 обеспечивают задержку импульсов, поступающих после момента t1 с выхода компараторов 31, 32 на S-входы RS-триггеров 27, на величину, большую длительности импульса ФКИ. Компараторы 32 выполняют функцию сравнения напряжений для положительного входного напряжения, а компараторы 31 с резисторами 33, 34 выполняют функцию сравнения токов для отрицательного входного напряжения.

В момент t0 на управляющем входе 14 установлено напряжение логической единицы, которым заперт диод 13, и через логический элемент НЕ 29 логическим нулем заперт n-p-n-транзистор 30 аналогового ключа 6.

При поступлении на входные шины 2, 3 и инвертирующие входы компараторов 31 отрицательных импульсов (см. t1 на U2, U3 на фиг.2) компараторы 31 переключаются в состояние логической единицы по выходу и через открытые диоды 15, 17 и n-p-n-транзистор 7 заряжается конденсатор 8. Через повторитель напряжения 10 это напряжение в виде выходного сигнала U11 (сигнала отрицательной обратной связи) подается через резисторы 34 на инвертирующие входы компараторов 31, возвращая их последовательно по мере нарастания выходного сигнала U11 в состояние логического нуля (при выравнивании амплитуд импульсов токов на инвертирующих входах в резисторах 33, 34).

Схемы задержки импульса 19, 21 обеспечивают задержку фронта и спада импульсов компараторов 31, поступающих на соответствующие S-входы RS-триггеров 27 в моменты t1, t5, t8, для превышения на спаде длительности импульсов на объединенных R-входах RS-триггеров 27 при возвращении компараторов 31 из состояния логической единицы в состояние логического нуля и выделении максимального значения с установкой единственного RS-триггера в единицу.

В течение отрицательных входных импульсов, поступающих на неинвертирующие входы компараторов 32 БСНиСТ 4, 5, которые находятся в состоянии логического нуля, диоды 16, 18 закрыты и не участвуют в работе.

Напряжение на конденсаторе 8 существует в течение времени хранения tXPAH; длительность которого определяется периодом импульсов сброса Сброса на управляющем входе 14. Импульс сброса (логический ноль) с управляющего входа 14 (см. U14 на фиг.2) через элемент НЕ 29 открывает разрядный ключ на n-p-n-транзисторе 30, разряжая конденсатор 8 за короткое время t2-t3. При этом диод 13 открыт, а значит, напряжение на базе n-p-n-транзистора 7 равно 0,3 В, что недостаточно для его отпирания и, следовательно, n-p-n-транзистор 7 защищен от токовой перегрузки даже в случае длинных входных отрицательных импульсов на входных шинах 2, 3 (на фиг.2 не показаны).

При поступлении на входные шины 2, 3 и неинвертирующие входы компараторов 32 БСНиСТ 4, 5 положительных импульсов (см. t4 на U2, U3 на фиг.2) компараторы 32 переключаются в состояние логической единицы по выходу и через диоды 16, 18 и n-p-n-транзистор 7 заряжают конденсатор 8. Через повторитель напряжения 10 это напряжение в виде выходного сигнала U11 (сигнала отрицательной обратной связи) подается на инвертирующие входы компараторов 32, возвращая их последовательно по мере нарастания выходного сигнала U11 в состояние логического нуля (при выравнивании напряжений на входах компараторов 32).

Схемы задержки импульса 20, 22 обеспечивают задержку фронта и спада импульсов компараторов 32, поступающих на соответствующие S-входы RS-триггеров 27 в моменты t4, t6, t7, t9 для превышения на спаде длительности импульсов ФКИ 26 на объединенных R-входах RS-триггеров 27 при возвращении компараторов 32 из состояния логической единицы в состояние логического нуля и выделении максимального значения с установкой единственного RS-триггера в единицу.

В течение положительных входных импульсов, поступающих через резисторы 33 на инвертирующие входы компараторов 31 БСНиСТ 4, 5, которые находятся в состоянии логического нуля, диоды 15, 17 закрыты и не участвуют в работе.

Величина tXPAH на порядок меньше, чем постоянная времени разряда запоминающего конденсатора 8 на высоком входном сопротивлении повторителя напряжения 10, что обеспечивает стабильность запомненной амплитуды. Импульсы на управляющем входе 14 аналогового ключа 6 периодические (см. U14 на фиг.2). Длительность импульсов tXPAH (время задержки сброса) должна быть достаточна для переноса во внешнее запоминающее устройство максимальной амплитуды очередных запомненных импульсов.

Определение полярности экстремального напряжения и номера канала с экстремальным напряжением осуществляется за счет изменения структуры схемы, в которой вновь введенный третий резистор 24 и компараторы 31, 32 из состава БСНиСТ 4, 5 обеспечили нормированными логическими уровнями вновь введенные логический элемент ИЛИ 25 и S-входы четырех RS-триггеров 27 (за счет повышения входного сопротивления n-p-n-транзистора 7). При выделении экстремального значения на выходах четырех компараторов БСНиСТ 4, 5 и RS-триггеров 27 образуется унитарный код, позволяющий выделить как номер входа с экстремальным напряжением, так и его полярность, за счет общего повторителя напряжения 10 в цепи обратной связи всех компараторов БСНиСТ 4, 5 пикового детектора. Благодаря введенному периодическому сбросу в нуль конденсатора 8 пикового детектора в совокупности с вышеуказанными признаками, возникает режим отслеживания экстремального из входных напряжений на участке после очередного сброса в нуль конденсатора 8, причем в каждом цикле переключений срабатывают любые компараторы БСНиСТ 4, 5, что обнуляет все RS-триггеры 27 через логический элемент ИЛИ 25 и ФКИ 26. Последующая с задержкой установка в единицу по S-входу одного из RS-триггеров 27 соответствует номеру входной шины 2 или 3 с максимальной амплитудой заданной полярности и осуществляется с одного из четырех компараторов БСНиСТ 4, 5, имеющего на входе максимальную амплитуду. При этом остальные три компаратора БСНиСТ 4, 5 с меньшей амплитудой на входе сброшены в нуль по цепи обратной связи. Устойчивая работа RS-триггеров 27 обеспечивается схемами задержки импульсов 19, 20, 21, 22, при этом сначала производится их установка в нуль, а затем установка в единицу с задержкой. Наличие единицы в унитарном коде на одном из входов ПКН 28 (на остальных входах нули) с одного из четырех выходов четырех RS-триггеров 27 обеспечивает соответствующее ступенчатое напряжение по второй шине 23, чем обеспечено сжатие информации.

Отсутствие ложного импульса (при включении питания) на выходе 11 пикового детектора обеспечивается обнулением напряжения на конденсаторе 8 аналоговым ключом 6 по одиночному импульсу на шине установки нуля (на фиг.1 не показана) или на управляющем входе 14 аналогового ключа 6.

Испытания макета пикового детектора подтвердили его работоспособность и заявленные преимущества в диапазоне рабочих температур от -40° до +50°C.

Пиковый детектор, содержащий шину питания, k входных шин, каждая из которых соединена с первым входом соответствующего блока сравнения напряжений и токов, где k=1, 2,…, аналоговый ключ, первый выход которого соединен с общей шиной, а второй выход соединен с эмиттером n-p-n-транзистора, через последовательно соединенные конденсатор и первый резистор - с общей шиной и с входом повторителя напряжения, выход которого соединен с первой выходной шиной, со вторыми входами блока сравнения напряжений и токов и через второй резистор - с базой n-p-n-транзистора и анодом первого диода, катод которого соединен с управляющим входом аналогового ключа, каждый выход каждого блока сравнения напряжений и токов соединен с анодом соответствующего второго диода и входом соответствующей схемы задержки импульса, шина питания соединена с коллектором n-p-n-транзистора, отличающийся тем, что дополнительно введены вторая выходная шина, третий резистор, логический элемент ИЛИ, формирователь коротких импульсов, 2k RS-триггеров, преобразователь кода в напряжение, выход каждой схемы задержки импульса соединен с соответствующим S-входом соответствующего RS-триггера, выходы каждого блока сравнения напряжений и токов соединены с соответствующим входом логического элемента ИЛИ, выход которого через формирователь коротких импульсов соединен с объединенными R-входами RS-триггеров, выходы которых через преобразователь кода в напряжение соединены со второй выходной шиной, база n-p-n-транзистора через третий резистор соединена с объединенными катодами вторых диодов.