Триггер, регистр сдвига, схема возбуждения устройства отображения, устройство отображения и панель устройства отображения

Иллюстрации

Показать всеИзобретения относятся к вычислительной технике и могут быть использованы в устройствах отображения. Техническим результатом является уменьшение размеров устройства. Триггер содержит первый (p-типа), второй (n-типа), третий (p-типа) и четвертый (p-типа) транзисторы; входные клеммы; первую и вторую выходные клеммы, первый и второй транзисторы составляют первую КМОП-схему, затворы транзисторов соединены один с другим и стоки транзисторов соединены один с другим, третий и четвертый транзисторы составляют вторую КМОП-схему, затворы транзисторов соединены один с другим и стоки транзисторов соединены один с другим, первая выходная клемма соединена с затворной стороной первой КМОП-схемы и стоковой стороной второй КМОП-схемы, вторая выходная клемма соединена с затворной стороной второй КМОП-схемы и стоковой стороной первой КМОП-схемы, по меньшей мере, один входной транзистор, включенный в группу указанных транзисторов с первого по четвертый, исток входного транзистора соединен с одной из входных клемм. 9 н. и 30 з.п. ф-лы, 75 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к триггеру и к различным схемам возбуждения устройства отображения.

Уровень техники

На фиг.75 (а) показана схема известного триггера, используемого в качестве схемы возбуждения затворов для жидкокристаллического устройства отображения или аналогичного устройства. Известный триггер (FF) 900, показанный на фиг.75 (а), включает пять p-канальных транзисторов (р100, р101, р102, р103, р104), пять n-канальных транзисторов (n100, n101, n102, n103, n104), клемму SB инвертированного сигнала установки, клемму R сигнала сброса, выходную клемму Q, клемму QB инвертированного выхода и клемму INITB инвертированного сигнала инициализации. В дальнейшем сигнал, поступающий на клемму SB, будет именоваться "SB-сигнал" (инвертированный сигнал установки), сигнал, поступающий на клемму R, будет именоваться "R-сигнал" (сигнал сброса), сигнал, поступающий на клемму INITB, (инвертированный сигнал инициализации) будет именоваться "INITB-сигнал", сигнал, снимаемый (выходящий) с клеммы Q, (выходной сигнал) будет именоваться "Q-сигнал" и сигнал, снимаемый (выходящий) с клеммы QB, (клеммы инвертированного выхода) будет именоваться "QB-сигнал". Далее, электрический потенциал VDD (источник питания высокого напряжения) будет именоваться "Vdd" и электрический потенциал VSS (источник питания низкого напряжения) будет именоваться "Vss".

Здесь, в схеме триггера FF900 (i) исток транзистора р100 соединен с клеммой VDD (источник питания высокого напряжения), (ii) сток транзистора р100, сток транзистора n100, сток транзистора р102, сток транзистора nl02, затвор транзистора р104, затвор транзистора n104 и клемма Q соединены одно с другими, (hi) исток транзистора n100 и сток транзистора nl01 соединены один с другим и (iv) исток транзистора nl01 соединен с клеммой VSS (источник питания низкого напряжения). Далее, в триггере FF900 (i) исток транзистора р101 соединен с клеммой VDD, (ii) сток транзистора р101 и исток транзистора р102 соединены один с другим, (iii) исток транзистора n102 и сток транзистора n103 соединены один с другим, (iv) исток транзистора n103 соединен с клеммой VSS, (v) исток транзистора p104 соединен с клеммой VDD, (vi) сток транзистора р104 и сток транзистора n104 соединены один с другим и (vii) исток транзистора n104 соединен с клеммой VSS. Кроме того, в триггере FF 900 (i) затвор транзистора р101, затвор транзистора n100 и клемма R соединены одно с другим, (ii) затвор транзистора р100, затвор транзистора n101, затвор транзистора n103 и клемма SB соединены одно с другим, (iii) исток транзистора р103 соединен с клеммой VDD, (iv) затвор транзистора р103 соединен с клеммой INITB и (v) затвор транзистора р102, затвор транзистора n102, сток транзистора р103 и клемма QB соединены одно с другим. В схеме триггера FF900 (i) транзистор р100 составляет схему SC установки, (ii) транзистор n100 составляет схему RC сброса, (iii) транзистор n101 составляет схему PDC определения приоритета, (iv) транзистор р103 составляет схему IC инициализации, (v) транзистор р101 и транзистор n103, соответственно, составляет схемы LRC освобождения защелки и (vi) транзистор р102, транзистор n102, транзистор р104 и транзистор n104 составляют схему LC защелки.

Фиг.75 (b) представляет временную диаграмму, иллюстрирующую работу триггера FF900, и фиг.75 (с) представляет таблицу истинности для триггера FF900.

Когда SB-сигнал активен (=низкий уровень) и R-сигнал неактивен (=высокий уровень) (период t1 времени, показанный на фиг.75 (b)), триггер FF900 работает, как описано ниже. Когда SB-сигнал становится активным (=низкий уровень), транзистор р100 (схема SC установки) отпирается. Это приводит к электрическому соединению клеммы Q с клеммой VDD (источник питания высокого напряжения) через транзистор р100. В результате Q-сигнал становится активным (=высокий уровень). Клемма SB электрически соединена с затвором транзистора n103. Поскольку транзистор n103 (схема LRC освобождения защелки) заперт в течение периода времени, когда SB-сигнал имеет низкий уровень, клемма Q не имеет короткого замыкания на клемму VSS (источник питания низкого напряжения). Соответственно, можно устойчиво поддерживать Q-сигнал в активном состоянии (=высокий уровень). Клемма Q соединена с затвором транзистора р104 и затвором транзистора n104. По этой причине, в течение периода времени, когда Q-сигнал имеет высокий уровень, транзистор р104 заперт, а транзистор n104 открыт. Соответственно, клемма QB электрически соединена с клеммой VSS (источник питания низкого напряжения) через транзистор n104, так что QB-сигнал стал активным (=низкий уровень). Клемма QB соединена с затвором транзистора р102 и затвором транзистора n10. По этой причине, в течение периода времени, когда QB-сигнал имеет низкий уровень, транзистор р102 открыт, а транзистор n10 заперт. Кроме того, в течение периода времени, когда R-сигнал имеет низкий уровень, транзистор р101 (схема LRC освобождения защелки) открыт. Соответственно, клемма Q электрически соединена с клеммой VDD (источник питания высокого напряжения) через транзистор р101 и транзистор р102. Как описано выше, в течение периода t1 времени Q-сигнал активен (=высокий уровень), в то время как QB-сигнал тоже активен (=низкий уровень) (см. А на фиг.75 (с)).

Если SB-сигнал неактивен (=высокий уровень) и R-сигнал неактивен (=низкий уровень) (период t2 времени, показанный на фиг.75 (b)), триггер FF900 работает, как описано ниже. Когда R-сигнал перешел на низкий уровень и SB-сигнал перешел на высокий уровень, транзистор n103 отпирается. В этом случае оба транзистора р101 и n103 (схемы LRC освобождения защелки) открыты, так что эта схема защелки образована (i) инвертором, составленным из транзистора р102 и транзистора n102, и (ii) другим инвертором, составленным из транзистора р104 и транзистора n104 (схема LC защелки включена). Здесь, поскольку оба транзистора - транзистор р100 (схема SC установки), передающий напряжение от клеммы VDD к клемме Q, и транзистор n100 (схема RC сброса) передающий напряжение Vss к клемме Q, заперты, электрическое напряжение в схему LC защелки не поступает. В таком защелкнутом состоянии сохраняется состояние, в котором SB-сигнал не изменялся, т.е. состояние, имевшее место в период t1 времени (Q-сигнал имеет высокий уровень, когда QB-сигнал имеет низкий уровень), сохраняется в течение периода t2 времени (см. С на фиг.75 (с)).

Когда SB-сигнал неактивен (=высокий уровень) и R-сигнал активен (=высокий уровень) (период t3 времени показан на фиг.75 (b)), триггер FF 900 работает, как описано ниже. Когда R-сигнал стал активным (=высокий уровень), транзистор n100 (схема RC сброса) отпирается. Поскольку SB-сигнал имеет высокий уровень, транзистор n101 (схема PDC определения приоритета) открыт. Поскольку оба транзистора - транзистор n100 и транзистор n101, открыты, клемма Q электрически соединена с источником напряжения VSS. Транзистор р101 (схема определения защелки) заперт в течение периода времени, когда R-сигнал имеет высокий уровень, так что клемма Q и клемма VDD не будут короткозамкнуты одна с другой. Соответственно, можно устойчиво поддерживать Q-сигнал в неактивном состоянии (=низкий уровень). Далее, поскольку транзистор n104 заперт и транзистор р104 открыт в течение периода времени, когда Q-сигнал имеет низкий уровень, клемма QB оказывается соединена с клеммой VDD электрически. В результате QB-сигнал переходит на высокий уровень. Более того, поскольку в период времени, когда QB-сигнал имеет высокий уровень и SB-сигнал имеет высокий уровень, (i) оба транзистора - транзистор n102 и транзистор n103, (схема LRC освобождения защелки) открыты и (ii) транзистор р102 заперт. Соответственно, клемма Q электрически соединена с клеммой VSS через транзистор n102 и транзистор n103. Как описано выше, в течение периода t3 времени Q-сигнал неактивен (=низкий уровень) и QB-сигнал неактивен (=высокий уровень) (см. D на фиг.75 (с)).

Когда SB-сигнал неактивен (=высокий уровень) и R-сигнал неактивен (=низкий уровень) (период t4 времени, показанный на фиг.75 (b)), триггер FF900 работает, как описано ниже. Когда SB-сигнал перешел на высокий уровень и R-сигнал перешел на низкий уровень, оба транзистора - транзистор р101 и транзистор n103, (схемы LRC освобождения защелки) отпираются. Это включает схему LC защелки. Соответственно, состояние, в котором R-сигнал не изменил свое состояние, сохраняется, т.е. состояние, имевшее место в течение периода t3 времени (Q-сигнал имеет низкий уровень, когда QB-сигнал имеет высокий уровень), сохраняется в течение периода t4 времени.

Инвертированный сигнал инициализации, т.е. INITB-сигнал, в нормальном состоянии неактивен (=высокий уровень), так что транзистор р103 (схема 1C инициализации) в нормальном состоянии заперт. Для инициализации триггера можно принудительно установить выходной сигнал (Q-сигнал) триггера, переведя INITB-сигнал в активное состояние. В триггере FF900, когда INITB-сигнал стал активным (=низкий уровень), транзистор р103 отпирается. В результате клемма QB и клемма VDD оказываются электрически соединены одна с другой, так что QB-сигнал переходит на высокий уровень. Транзистор n10 открыт в течение периода времени, когда QB-сигнал имеет высокий уровень. Далее, транзистор n103 открыт в течение периода времени, когда SB-сигнал неактивен (высокий уровень). Соответственно, клемма Q оказывается электрически соединена с клеммой VSS через транзистор n102 и транзистор n103, так что Q-сигнал становится неактивным (=низкий уровень).

Отметим, что транзистор n101 (схема определения приоритета) задает, какой из сигналов - SB-сигнал или R-сигнал, имеет приоритет, в случае, когда оба сигнала - SB-сигнал и R-сигнал, стали активными одновременно. В триггере FF900, когда SB-сигнал стал активным (=низкий уровень) и R-сигнал стал активным (=высокий уровень), оба транзистора - транзистор р100 и транзистор n100, отпираются. В этом случае транзистор n101 (схема определения приоритета) запирается, так что схема RC сброса и клемма VSS оказываются отделены электрически одна от другой, а клемма Q электрически соединена с клеммой VDD через транзистор р100. Другими словами, SB-сигнал имеет приоритет.

Перечень литературы

[Патентная литература]

Патентная литература 1

Публикация заявки на патент Японии, Tokukai, No. 2001-135093 А (дата публикации: 18 мая 2001 г.)

Сущность изобретения

Техническая проблема

В описанном выше известном триггере схема занимает большую площадь. Это было препятствием для уменьшения размеров устройства (такого как регистр сдвига и различные схемы возбуждения устройства отображения), включающего такой известный триггер.

Целью настоящего изобретения является создание компактного триггера или различных компактных схем возбуждения устройства отображения.

Решение проблемы

Триггер согласно настоящему изобретению включает: первый транзистор, представляющий собой p-канальный транзистор; второй транзистор, представляющий собой n-канальный транзистор; третий транзистор, представляющий собой p-канальный транзистор; четвертый транзистор, представляющий собой n-канальный транзистор; несколько входных клемм; первую выходную клемму; вторую выходную клемму; и входной транзистор, первый транзистор и второй транзистор составляют первую КМОП-схему, так что затворы этих транзисторов соединены один с другим и стоки соединены один с другим, третий транзистор и четвертый транзистор составляют вторую КМОП-схему, так что затворы этих транзисторов соединены один с другим и стоки соединены один с другим, первая выходная клемма соединена с затворной стороной первой КМОП-схемы и стоковой стороной второй КМОП-схемы, вторая выходная клемма соединена с затворной стороной второй КМОП-схемы и стоковой стороной первой КМОП-схемы, затвор входного транзистора соединен с одной из нескольких входных клемм, а исток этого транзистора соединен с другой из этих нескольких входных клемм. Отметим, что сток входного транзистора соединен с первой выходной клеммой прямо или не прямо (через релейный транзистор).

В настоящем описании один (на выходной стороне) из двух электропроводных электродов транзистора (p-канального транзистора или n-канального транзистора) называется «сток». В описанной выше конфигурации, если оба сигнала, поступающие на разные входные клеммы, стали активными одновременно, один из этих сигналов, поступающих на разные входные клеммы, может быть передан на выход, поскольку указанный один из сигналов имеет приоритет и без использования схемы определения приоритета, которая была нужна в известном триггере. Это делает возможным создание еще более компактного триггера.

Преимущества изобретения

Как описано выше, при использовании такой схемы становится возможным создать компактный триггер, компактный регистр сдвига или компактную схему возбуждения устройства отображения.

Краткое описание чертежей

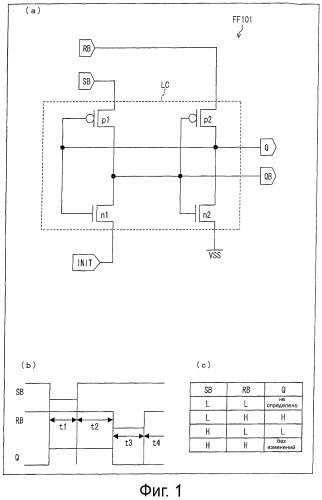

Фиг.1 представляет пояснительный вид, иллюстрирующий триггер в соответствии с вариантом 1 настоящего изобретения: фиг.1 (а) показывает электрическую схему, фиг.1 (b) показывает временную диаграмму и фиг.1 (с) показывает таблицу истинности.

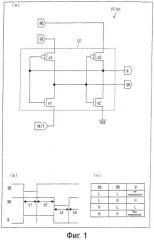

Фиг.2 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.2 (а) показывает электрическую схему, фиг.2 (b) показывает временную диаграмму и фиг.2 (с) показывает таблицу истинности.

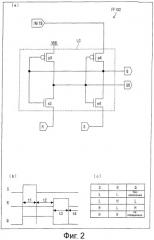

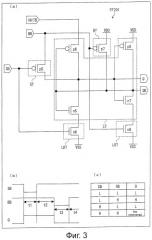

Фиг.3 представляет пояснительный вид, иллюстрирующий триггер в соответствии с вариантом 2 настоящего изобретения: фиг.3 (а) показывает электрическую схему, фиг.3 (b) показывает временную диаграмму и фиг.3 (с) показывает таблицу истинности.

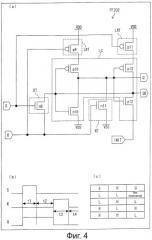

Фиг.4 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.4 (а) показывает электрическую схему, фиг.4 (b) показывает временную диаграмму и фиг.4 (с) показывает таблицу истинности.

Фиг.5 представляет пояснительный вид, иллюстрирующий триггер в соответствии с вариантом 3 настоящего изобретения: фиг.5 (а) показывает электрическую схему, фиг.5 (b) показывает временную диаграмму и фиг.5 (с) показывает таблицу истинности.

Фиг.6 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.6 (а) показывает электрическую схему, фиг.6 (b) показывает временную диаграмму и фиг.6 (с) показывает таблицу истинности.

Фиг.7 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.7 (а) показывает электрическую схему, фиг.7 (b) показывает временную диаграмму и фиг.7 (с) показывает таблицу истинности.

Фиг.8 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.8 (а) показывает электрическую схему, фиг.8 (b) показывает временную диаграмму и фиг.8 (с) показывает таблицу истинности.

Фиг.9 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.9 (а) показывает электрическую схему, фиг.9 (b) показывает временную диаграмму и фиг.9 (с) показывает таблицу истинности.

Фиг.10 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.10 (а) показывает электрическую схему, фиг.10 (b) показывает временную диаграмму и фиг.10 (с) показывает таблицу истинности.

Фиг.11 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.11 (а) показывает электрическую схему, фиг.11 (b) показывает таблицу истинности.

Фиг.12 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.12 (а) показывает электрическую схему, фиг.12 (b) показывает таблицу истинности.

Фиг.13 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.13 (а) показывает электрическую схему, фиг.13 (b) показывает таблицу истинности.

Фиг.14 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.14 (а) показывает электрическую схему, фиг.14 (b) показывает таблицу истинности.

Фиг.15 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.15 (а) показывает электрическую схему, фиг.15 (b) показывает таблицу истинности.

Фиг.16 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.16 (а) показывает электрическую схему, фиг.16 (b) показывает таблицу истинности.

Фиг.17 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.17 (а) показывает электрическую схему, фиг.17 (b) показывает таблицу истинности.

Фиг.18 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.18 (а) показывает электрическую схему, фиг.18 (b) показывает таблицу истинности.

Фиг.19 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.19 (а) показывает электрическую схему, фиг.19 (b) показывает таблицу истинности.

Фиг.20 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.20 (а) показывает электрическую схему, фиг.20 (b) показывает таблицу истинности.

Фиг.21 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.21 (а) показывает электрическую схему, фиг.21 (b) показывает таблицу истинности.

Фиг.22 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 2 настоящего изобретения: фиг.22 (а) показывает электрическую схему, фиг.22 (b) показывает таблицу истинности.

Фиг.23 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.23 (а) показывает электрическую схему, фиг.23 (b) показывает таблицу истинности.

Фиг.24 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.24 (а) показывает электрическую схему, фиг.24 (b) показывает таблицу истинности.

Фиг.25 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.25 (а) показывает электрическую схему, фиг.25 (b) показывает таблицу истинности.

Фиг.26 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.26 (а) показывает электрическую схему, фиг.26 (b) показывает таблицу истинности.

Фиг.27 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 1 настоящего изобретения: фиг.27 (а) показывает электрическую схему, фиг.27 (b) показывает таблицу истинности.

Фиг.28 представляет вид, схематично иллюстрирующий конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.29 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.28.

Фиг.30 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.28.

Фиг.31 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.32 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.33 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.32.

Фиг.34 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.32.

Фиг.35 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.36 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.37 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.38 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.37.

Фиг.39 представляет электрическую схему, показывающую D-защелку в схеме возбуждения G-Gs устройства отображения, изображенного на фиг.37.

Фиг.40 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.37.

Фиг.41 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.37.

Фиг.42 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.43 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.42.

Фиг.44 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.42.

Фиг.45 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.42.

Фиг.46 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.47 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.46.

Фиг.48 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.46.

Фиг.49 представляет электрическую схему, иллюстрирующую модифицированный пример схемы, изображенной на фиг.43.

Фиг.50 представляет временную диаграмму, показывающую модифицированный пример временной диаграммы, изображенной на фиг.40 или фиг.44.

Фиг.51 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.52 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.51.

Фиг.53 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.51.

Фиг.54 представляет электрическую схему, иллюстрирующую схему И-НЕ в регистре сдвига в устройстве отображения, изображенном на фиг.51.

Фиг.55 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.56 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.55.

Фиг.57 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.55.

Фиг.58 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.59 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.58.

Фиг.60 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.58.

Фиг.61 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.62 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.61.

Фиг.63 представляет временную диаграмму, показывающую сигналы управления устройством отображения, изображенным на фиг.61.

Фиг.64 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.65 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.64.

Фиг.66 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.67 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.68 представляет вид, схематично иллюстрирующий другую конфигурацию устройства отображения согласно настоящему изобретению.

Фиг.69 представляет электрическую схему, иллюстрирующую каждый из нескольких каскадов регистра сдвига в устройстве отображения, показанном на фиг.68.

Фиг.70 представляет пояснительный вид, иллюстрирующий другой триггер, используемый в устройстве отображения согласно настоящему изобретению: фиг.70 (а) показывает электрическую схему, фиг.70 (b) показывает временную диаграмму и фиг.70 (с) показывает таблицу истинности.

Фиг.71 представляет пояснительный вид, иллюстрирующий другой триггер, используемый в устройстве отображения согласно настоящему изобретению: фиг.71 (а) показывает электрическую схему, фиг.71 (b) показывает таблицу истинности.

Фиг.72 представляет пояснительный вид, иллюстрирующий другой триггер в соответствии с вариантом 3 настоящего изобретения: фиг.72 (а) показывает электрическую схему, фиг.72 (b) показывает таблицу истинности.

Фиг.73 представляет временную диаграмму, показывающую другой модифицированный пример временной диаграммы, изображенной на фиг.40 или фиг.44.

Фиг.74 представляет временную диаграмму, показывающую другой модифицированный пример временной диаграммы, изображенной на фиг.40 или фиг.44.

Фиг.75 представляет электрическую схему, иллюстрирующую известный триггер.

Подробное описание изобретения

Варианты настоящего изобретения описаны ниже со ссылками на фиг.1-74. В последующем описании RS-триггер (в дальнейшем обозначаемый триггер "FF", где это подходит) принимает (i) сигнал установки (S-сигнал или SB-сигнал) через клемму установки (клемма S или клемма SB), (ii) сигнал сброса (R-сигнал или RB-сигнал) через клемму сброса (клемма R или клемма RB) и (iii) сигнал инициализации (INIT-сигнал или INITB-сигнал) через клемму инициализации (клемма INIT или клемма INITB). Кроме того, RS-триггер передает на выход (i) Q-сигнал через выходную клемму (клемму Q) и (ii) QB-сигнал через клемму инвертированного выхода (клемма QB). Отметим, что электрическое напряжение источника питания высокого напряжения (VDD) равно Vdd (в дальнейшем именуется «высокое», где это подходит), а электрическое напряжение источника питания низкого напряжения (VSS) равно Vss (в дальнейшем именуется «низкое», где это подходит). Указанные S-сигнал (сигнал установки), R-сигнал (сигнал сброса), INIT-сигнал (сигнал инициализации) и Q-сигнал (выходной сигнал) имеют высокий уровень, когда они активны. Указанные SB-сигнал (инвертированный сигнал установки), RB-сигнал (инвертированный сигнал сброса), INITB-сигнал (инвертированный сигнал инициализации) и QB-сигнал (инвертированный выходной сигнал) имеют низкий уровень, когда они активны.

[Триггер согласно варианту 1]

Фиг.1 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера согласно варианту 1 настоящего изобретение. Триггер FF 101, показанный на фиг.1 (а), включает (i) p-канальный транзистор р1 и n-канальный транзистор n1, которые составляют КМОП-схему, (n) p-канальный транзистор р2 и n-канальный транзистор n2, которые составляют другую КМОП-схему, (iii) клемму SB, (iv) клемму RB, (v) клемму Q, (vi) клемму QB и (vii) клемму INIT. В схеме триггера FF 101 (i) затвор транзистора р1, затвор транзистора n1, сток транзистора р2, сток транзистора n2 и клемма Q соединены одно с другим, (ii) сток транзистора р1, сток транзистора n1, затвор транзистора р2, затвор транзистора n2 и клемма QB соединены одно с другим, (iii) исток транзистора р1 соединен с клеммой SB, (iv) исток транзистора р2 соединен с клеммой RB, (v) исток транзистора n1 соединен с клеммой INIT и (vi) исток транзистора n2 соединен с клеммой VSS (источник питания низкого напряжения). Здесь транзистор р1, транзистор n1, транзистор р2 и транзистор n2 составляют схему LC защелки.

Фиг.1 (b) представляет временную диаграмму, показывающую работу триггера FF 101 (когда INIT-сигнал неактивен), и фиг.1 (с) представляет таблицу истинности для триггера FF 101 (когда INIT-сигнал неактивен).

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал активен (=низкий уровень) и RB-сигнал неактивен (=высокий уровень) (период t1 времени). Когда выходной 0-сигнал имеет низкий уровень и выходной QB-сигнал имеет высокий уровень, транзистор р1 открыт. В таких условиях, когда SB-сигнал стал активным (=низкий уровень), электрический потенциал клеммы QB снижается до уровня Vss + Vth (пороговое напряжение). Когда электрический потенциал клеммы QB уменьшается и становится по существу равным Vss, транзистор р2 отпирается, а транзистор n2 запирается (если пороговое напряжение транзистора n2 не меньше напряжения Vth, транзистор n2 запирается полностью). Здесь, поскольку RB-сигнал неактивен (=высокий уровень =Vdd), выходной Q-сигнал перешел на высокий уровень. Клемма Q соединена с затвором транзистора р1 и с затвором транзистора n1. Соответственно, когда клемма Q переходит на высокий уровень, транзистор р1 запирается, а транзистор n1 отпирается. В течение периода времени, отличного от периода времени инициализации, INIT-сигнал имеет низкий уровень (Vss). Соответственно, когда транзистор n1 отпирается, выходной QB-сигнал тоже переходит на низкий уровень (Vss). Когда QB-сигнал имеет низкий уровень, транзистор р2 открыт, а транзистор n2 заперт. В этом случае клемма Q оказывается отсоединена электрически от клеммы VSS и передает на выход RB-сигнал (=высокий уровень =Vdd). Как описано выше, выходной QB-сигнал начинает сразу же смещаться к уровню напряжения Vss + Vth, но выходной Q-сигнал поступает по цепи обратной связи назад через схему LC защелки. В результате выходной QB-сигнал устойчиво остается на низком (Vss) уровне. Отметим, что когда SB-сигнал сдвигается от состояния высокого уровня к состоянию низкого уровня, сток транзистора р1 не имеет электрического соединения с каким-либо открытым транзистором. Соответственно, схема освобождения защелки не нужна.

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал неактивен (=высокий уровень) и RB-сигнал неактивен (=высокий уровень) (период t2 времени). Указанный INIT-сигнал имеет низкий уровень (Vss) в течение периода времени, отличного от периода времени инициализации. Вследствие этого, когда SB-сигнал и RB-сигнал имеют высокий уровень, схема LC защелки оказывается включена. Соответственно, состояние, в котором SB-сигнал не изменялся, сохраняется. Иными словами, состояние, имевшее место в периоде t1 (выходной Q-сигнал имеет высокий уровень, и выходной QB-сигнал имеет низкий уровень) сохраняется в периоде t2.

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал неактивен (=высокий уровень) и RB-сигнал активен (=низкий уровень) (период t3 времени). Когда выходной Q-сигнал имеет высокий уровень и выходной QB-сигнал имеет низкий уровень, транзистор р2 открыт. В такой ситуации, когда RB-сигнал стал активным (=низкий уровень), электрический потенциал клеммы Q уменьшается до уровня Vss + Vth (пороговое напряжение). Когда электрический потенциал клеммы Q уменьшился и стал по существу равным напряжению Vss, транзистор р1 открывается, а транзистор n1 запирается (если пороговое напряжение транзистора n1 не меньше напряжения Vth, транзистор n1 запирается полностью). Здесь SB-сигнал неактивен (=высокий уровень =Vdd), так что выходной QB-сигнал переходит на высокий уровень. Клемма QB соединена с затвором транзистора р2 и с затвором транзистора n2. Соответственно, когда выходной QB-сигнал переходит на высокий уровень, транзистор р2 запирается, а транзистор n2 открывается. Когда транзистор n2 открыт, клемма Q оказывается электрически соединена с клеммой VSS, вследствие чего Q-сигнал переходит на низкий уровень (Vss). Когда клемма Q имеет низкий уровень, транзистор р1 открыт, а транзистор n1 заперт. Соответственно, клемма QB отсоединена электрически от клеммы EMIT и передает на выход SB-сигнал (высокий уровень =Vdd). Как описано выше, выходной Q-сигнал сразу же начинает смещаться к уровню напряжения Vss + Vth, но выходной QB-сигнал поступает по цепи обратной связи назад через схему LC защелки, вследствие чего выходной Q-сигнал устойчиво остается на низком уровне (Vss). Отметим, что сток транзистора р2 не имеет электрического соединения с каким-либо открытым транзистором, когда RB-сигнал сдвигается от состояния с высоким уровнем к состоянию с низким уровнем. Соответственно, схема освобождения защелки не нужна.

Последующее описание относится к работе триггера FF 101 в случае, когда SB-сигнал неактивен (=высокий уровень) и RB-сигнал неактивен (=высокий уровень) (период t4 времени). Указанный INIT-сигнал имеет низкий уровень (Vss) в течение периода времени, отличного от периода времени инициализации. Вследствие этого, когда SB-сигнал имеет высокий уровень и RB-сигнал имеет высокий уровень, схема LC защелки оказывается включена. Соответственно, состояние, в котором SB-сигнал не изменялся, сохраняется. Иными словами, состояние, имевшее место в периоде t3 (выходной Q-сигнал имеет низкий уровень, и выходной QB-сигнал имеет высокий уровень) сохраняется в периоде t4.

Последующее описание относится к работе триггера FF 101, когда INIT-сигнал активен (=высокий уровень) (инициализация). Когда выходной Q-сигнал имеет низкий уровень и выходной QB-сигнал имеет высокий уровень, транзистор n1 заперт. В такой ситуации, когда INIT-сигнал перешел на высокий уровень, нет никакого влияния на выходные сигналы триггера (Q-сигнал имеет низкий уровень, и QB-сигнал имеет высокий уровень). Когда выходной Q-сигнал имеет высокий уровень и выходной QB-сигнал имеет низкий уровень, транзистор n1 открыт. В такой ситуации, когда INIT-сигнал перешел на высокий уровень, электрический потенциал клеммы QB увеличивается до уровня Vdd-Vth (пороговое напряжение). Когда электрический потенциал клеммы QB увеличивается и становится по существу равен Vdd, транзистор n2 отпирается и транзистор р2 запирается (когда пороговое напряжение транзистора р2 не меньше Vth, транзистор р2 полностью запирается). В этом случае клемма Q оказывается электрически соединена с клеммой VSS, так что выходной Q-сигнал переходит на низкий уровень (=Vss). Клемма Q соединена с затвором транзистора р1 и затвором транзистора n1. Соответственно, когда выходной Q-сигнал переходит на низкий уровень, транзистор n1 запирается, а транзистор р1 отпирается. Здесь SB-сигнал неактивен (=высокий уровень =Vdd), так что выходной QB-сигнал переходит на высокий уровень. Когда выходной QB-сигнал имеет высокий уровень, транзистор n2 открыт, а транзистор р2 заперт. Соответственно, клемма Q оказывается электрически отделена от клеммы RB и передает на выход низкий уровень (Vss). Как описано выше, выходной QB-сигнал сразу же начинает сдвигаться к уровню потенциала Vdd-Vth, но выходной Q-сигнал поступает по цепи обратной связи назад через схему LC защелки. Соответственно, выходной QB-сигнал устойчиво остается на высоком уровне (Vdd). Применение описанного выше способа позволяет осуществлять инициализацию без использования схемы инициализации.

Когда оба сигнала, SB-сигнал и RB-сигнал, активны (=низкий уровень), транзистор р1, транзистор р2, транзистор n1 и транзистор n2 оказываются заперты (плавающее состояние), когда потенциалы обеих клемм, клеммы Q и клеммы QB, становятся равны напряжению Vss + Vth. В этом случае выходные сигналы (Q-сигнал и QB-сигнал) находятся в неопределенном состоянии.

Как описано выше, в схеме триггера FF 101 (i) транзистор р1, транзистор n1, транзистор р2 и транзистор n2 (две CMOS-схемы) составляют схему защелки, (ii) исток транзистора р1 соединен с клеммой SB, (iii) исток транзистора р2 соединен с клеммой RB и (iv) исток транзистора n1 соединен с клеммой INIT. В такой схеме можно выполнять операцию установки, операцию защелкивания, операцию сброса и операцию инициализации без использования схемы установки, схемы сброса, схемы освобождения защелки и схемы инициализации, каждая из которых была необходима в известном триггере (см. фиг.70).

Можно модифицировать схему, представленную на фиг.1 (а), чтобы соединить исток транзистора n1 с клеммой VSS, как это сделано в триггере FF 105, показанном на фиг.21 (а). На фиг.21 (b) представлена таблица истинности для триггера FF 105.

Фиг.2 (а) представляет электрическую схему, иллюстрирующую конфигурацию триггера FF 102, который представляет собой модифицированный пример триггера, показанного на фиг.1 (а). Триггер FF 102, показанный на фиг.2 (а), включает (i) p-канальный транзистор р3 и n-канальный транзистор n3, которые составляют КМОП-схему, (ii) p-канальный транзистор р4 и n-канальный транзистор n4, которые составляют другую КМОП-схему, (iii) клемму S, (iv) клемму R, (v) к