Входной каскад быстродействующего операционного усилителя

Иллюстрации

Показать всеИзобретение относится к устройствам усиления аналоговых сигналов. Техническим результатом является расширение диапазона активной работы входного каскада операционного усилителя (ОУ) для дифференциального сигнала. Входной каскад ОУ содержит первый (1) и второй (2) входные транзисторы, первый (3) и второй (4) выходные транзисторы, первый (5) и второй (6) вспомогательные транзисторы, первый (7) и второй (8) входы устройства, первый (9) и второй (10) прямосмещенные p-n-переходы, первый (11) токостабилизирующий двухполюсник, токовые выходы устройства (12), (13), (14), (15), первую (16) шину источника питания (ИП), где между вторым (10) p-n-переходом, включенным в эмиттер второго (6) транзистора, и второй (17) шиной ИП включен первый (11) двухполюсник, между первым (9) p-n-переходом, включенным в эмиттер первого (5) транзистора, и второй (17) шиной ИП включен второй (18) двухполюсник, между общим узлом (19) первого (9) p-n-перехода и второго (18) двухполюсника, а также общим узлом (20) второго (12) p-n-перехода и первого (11) двухполюсника последовательно включены третий (21) и четвертый (22) резисторы, общий узел (23) которых соединен с базами первого (3) и второго (4) входных транзисторов. 18 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы входных каскадов ОУ, выполненных в виде дифференциальных усилителей (ДУ) на n-p-n- и p-n-p-транзисторах с так называемой «архитектурой входного каскада операционного усилителя µA741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом

[29-30], стали основным усилительным элементом многих аналоговых интерфейсов. Это связано с тем, что в таких ДУ минимизируется входная емкость из-за отсутствия эффекта Миллера. Предлагаемое изобретение относится к данному подклассу устройств.

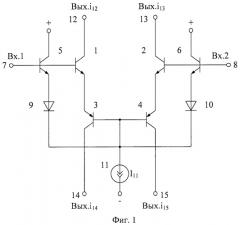

Ближайшим прототипом (фиг.1) заявляемого устройства является входной каскад быстродействующего операционного усилителя по патенту US 4.901.031, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов с объединенными базами, первый 5 и второй 6 вспомогательные транзисторы, базы которых соединены с соответствующими базами первого 1 и второго 2 входных транзисторов и подключены к соответствующим первому 7 и второму 8 входам устройства, первый 9 и второй 10 прямосмещенные p-n-переходы, включенные в эмиттеры соответствующих первого 5 и второго 6 вспомогательных транзисторов, первый 11 токостабилизирующий двухполюсник, токовые выходы устройства 12, 13, 14, 15, связанные с коллекторами первого 1 и второго 2 входных транзисторов, а также коллекторами первого 3 и второго 4 выходных транзисторов, причем коллекторы первого 5 и второго 6 вспомогательных транзисторов связаны с первой 16 шиной источника питания.

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно узкий динамический диапазон (Uгр) линейного усиления дифференциальных сигналов (Uвx.max<Uгp≈100÷150 мВ). Как показано в [31], это обстоятельство является главной причиной невысокого быстродействия современных операционных усилителей, обусловленной нелинейным режимом работы входного каскада ОУ. При этом для большинства ОУ с высокоимпедансным узлом и одним корректирующим конденсатором максимальная скорость нарастания выходного напряжения

υ в ы х = 2 π f с р U г р , ( 1 )

где fср - частота единичного усиления (частота среза) скорректированного ОУ;

Uгр - напряжение ограничения проходной характеристики iвых=f(uвх) входного каскада (для классических ДУ Uгр=50÷100 мВ). Из (1) следует, что повышение uвых можно осуществить двумя качественно разными путями:

1. Увеличением диапазона активной работы входного ДУ (Uгр) без изменения крутизны преобразования входного напряжения в выходные токи ДУ;

2. Повышением fср за счет улучшения частотных свойств транзисторов, что связано, прежде всего, с использованием более высокочастотных техпроцессов (SG25VD, SG25H1, SG25RH и др.). Заявляемый входной каскад ОУ решает задачу повышения быстродействия за счет увеличения (без изменения крутизны) более чем на порядок диапазона линейной работы Uгр=1÷2B.

Таким образом, основная задача предлагаемого изобретения состоит в расширении диапазона активной работы входного каскада ОУ для дифференциального сигнала - получении Uгр>>100 мВ.

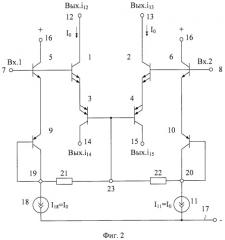

Поставленная задача достигается тем, что входной каскад быстродействующего операционного усилителя, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов с объединенными базами, первый 5 и второй 6 вспомогательные транзисторы, базы которых соединены с соответствующими базами первого 1 и второго 2 входных транзисторов и подключены к соответствующим первому 7 и второму 8 входам устройства, первый 9 и второй 10 прямосмещенные p-n-переходы, включенные в эмиттеры соответствующих первого 5 и второго 6 вспомогательных транзисторов, первый 11 токостабилизирующий двухполюсник, токовые выходы устройства 12, 13, 14, 15, связанные с коллекторами первого 1 и второго 2 входных транзисторов, а также коллекторами первого 3 и второго 4 выходных транзисторов, причем коллекторы первого 5 и второго 6 вспомогательных транзисторов связаны с первой 16 шиной источника питания, отличается тем, что между вторым 10 прямосмещенным p-n-переходом, включенным в эмиттер второго 6 вспомогательного транзистора, и второй 17 шиной источника питания включен первый 11 токостабилизирующий двухполюсник, между первым 9 прямосмещенным p-n-переходом, включенным в эмиттер первого 5 вспомогательного транзистора, и второй 17 шиной источника питания включен второй 18 токостабилизирующий двухполюсник, между общим узлом 19 первого 9 прямосмещенного p-n-перехода и второго 18 токостабилизирующего двухполюсника, а также общим узлом 20 второго 12 прямосмещенного p-n-перехода и первого 11 токостабилизирующего двухполюсника последовательно включены третий 21 и четвертый 22 дополнительные резисторы, общий узел 23 которых соединен с базами первого 3 и второго 4 входных транзисторов.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с формулой изобретения.

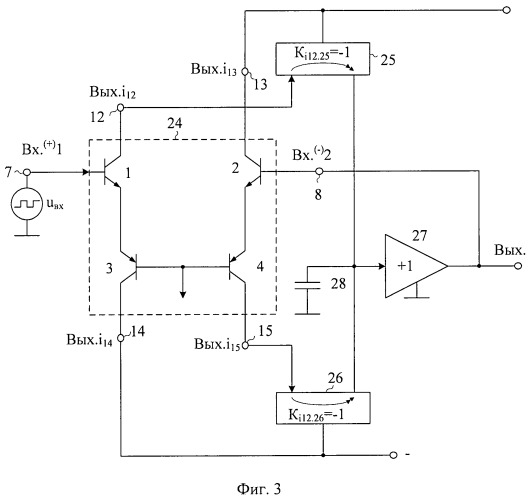

На фиг.3 приведена возможная архитектура быстродействующего операционного усилителя с предлагаемым входным каскадом.

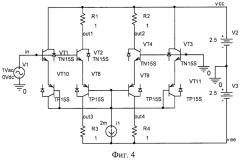

На фиг.4 показана схема ДУ-прототипа фиг.1 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.5 приведена зависимость разности выходных токов (I(out1)-I(out2)) и (I(out3)-I(out4)) ДУ-прототипа фиг.4 от входного напряжения uвх.

На фиг.6 представлена зависимость абсолютных значений выходных токов I(out1) и I(out2) ДУ-прототипа фиг.4 от входного напряжения uвх. Зависимость выходных токов I(out3) и I(out4) ДУ-прототипа фиг.4 от входного напряжения uвх представлена на фиг.7.

На фиг.8 показана схема заявляемого ДУ фиг.2 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.9 - фиг.12 - зависимости разностей выходных токов (I(out1)-I(out2)) и (I(out3)-I(out4)) от входного напряжения uвх ДУ фиг.8 при различных значениях сопротивлений дополнительных резисторов 21, 22 (Rvar).

На фиг.13 представлена зависимость абсолютных значений выходных токов I(out1) и I(out2) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 21, 22 Rvar=200 Ом, а на фиг.14 - зависимость выходных токов I(out3) и I(out4) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 21, 22 Rvar=200 Ом.

На фиг.15 показана зависимость абсолютных значений выходных токов I(out1) и I(out2) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 21, 22 Rvar=1 кОм, а на фиг.16 - зависимость выходных токов I(out1) и I(out2) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 21, 22 Rvar=1 кОм в увеличенном масштабе.

На фиг.17 представлена зависимость абсолютных значений выходных токов I(out3) и I(out4) заявляемого ДУ от входного напряжения uвх при Rvar=1 кОм, а на фиг.18 - зависимость выходных токов I(out3) и I(out4) заявляемого ДУ от входного напряжения uвх при Rvar=1 кОм в увеличенном масштабе.

Входной каскад (ДУ) быстродействующего операционного усилителя фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов с объединенными базами, первый 5 и второй 6 вспомогательные транзисторы, базы которых соединены с соответствующими базами первого 1 и второго 2 входных транзисторов и подключены к соответствующим первому 7 и второму 8 входам устройства, первый 9 и второй 10 прямосмещенные p-n-переходы, включенные в эмиттеры соответствующих первого 5 и второго 6 вспомогательных транзисторов, первый 11 токостабилизирующий двухполюсник, токовые выходы устройства 12, 13, 14, 15, связанные с коллекторами первого 1 и второго 2 входных транзисторов, а также коллекторами первого 3 и второго 4 выходных транзисторов, причем коллекторы первого 5 и второго 6 вспомогательных транзисторов связаны с первой 16 шиной источника питания. Между вторым 10 прямосмещенным p-n-переходом, включенным в эмиттер второго 6 вспомогательного транзистора, и второй 17 шиной источника питания включен первый 11 токостабилизирующий двухполюсник, между первым 9 прямосмещенным p-n-переходом, включенным в эмиттер первого 5 вспомогательного транзистора, и второй 17 шиной источника питания включен второй 18 токостабилизирующий двухполюсник, между общим узлом 19 первого 9 прямосмещенного p-n-перехода и второго 18 токостабилизирующего двухполюсника, а также общим узлом 20 второго 12 прямосмещенного p-n-перехода и первого 11 токостабилизирующего двухполюсника последовательно включены третий 21 и четвертый 22 дополнительные резисторы, общий узел 23 которых соединен с базами первого 3 и второго 4 входных транзисторов.

На фиг.3 заявляемый входной каскад фиг.2 (24) включен в структуру быстродействующего ОУ, которая содержит дополнительные токовые зеркала 25, 26, выходной буфер 27 и корректирующий конденсатор 28. При этом ОУ охвачен 100% отрицательной обратной связью.

Рассмотрим работу заявляемого устройства фиг.2.

В связи с тем, что падение напряжения на резисторах 21, 22, создаваемое токами базы транзисторов 3 и 4, мало, статические токи всех транзисторов схемы определяются токами токостабилизирущих двухполюсников 18 и 11. При этом за счет увеличения площадей эмиттерных переходов транзисторов 1, 2 и 3, 4 можно при нулевом входном напряжении ДУ обеспечить равенство всех эмиттерных токов схемы:

I э 1 = I э 2 = I э 3 = I э 4 = I э 5 = I э 6 ≈ I э 0 , ( 1 )

где I0=I18=I11.

Если напряжение на первом 7 входе (Вх.1) ДУ становится больше напряжения на втором 8 входе ДУ, то коллекторные токи транзистора 1 и 3 увеличиваются, а транзисторов 2 и 4 - уменьшаются. При этом входное дифференциальное напряжение uвх «выделяется» на резисторах 21 и 22, что приводит к увеличению «открывающего» напряжения между базой транзистора 1 и базой транзистора 3:

u б 1 − 3 ≈ u в х 2 . ( 2 )

Таким образом коллекторные (выходные) токи транзисторов 1 и 3 будут пропорциональны входному напряжению в широком диапазоне uвх:

i 12 = i 14 ≈ u в х r э 1 + r э 2 + R э + R 21 2 β 3 , ( 3 )

где rэ1, rэ2 - сопротивления эмиттерных переходов транзисторов 1 и 3;

R21=R22 - сопротивления резисторов 21 и 22;

β3 - коэффициент усиления по току базы транзистора 3;

Rэ - сопротивление объемного низкоомного эмиттерного резистора или дополнительного резистора Rd=10÷20 Ом, включаемого в ряде случаев в эмиттерную цепь транзисторов 1 и 3 (фиг.8).

Учитывая, что при увеличении Iэi сопротивления rэ1 и rэ2 существенно уменьшаются, из (3) можно найти, что при больших uвх

i 12 = i 14 ≈ u в х 2 ( R э + R 21 2 β 3 ) = u в х S , ( 4 )

где S = 1 2 ( R э + R 21 2 β 3 ) - крутизна ДУ.

Уравнение (4) справедливо для следующих амплитуд входных напряжений

U в х . м а х ≤ U г р = I 0 R 21 = I 0 R 22 . ( 5 )

Таким образом, диапазон активной работы ДУ фиг.2 определяется произведением (5) и может выбираться в соответствии с требуемыми значениями к υвых операционного усилителя (1). Данные выводы подтверждаются графиками (фиг.9-17), из которых следует, что диапазон активной работы заявляемого ДУ увеличивается на порядок в сравнении с Uгр ДУ-прототипа.

Таким образом, проходная характеристика iвых=f(uвх) заявляемого ДУ «продлевается» в область больших токов (фиг.9-17), значительно превышающих статические токи транзисторов ДУ. Это характерно для транзисторных каскадов класса «АВ».

При отрицательном uвх ДУ фиг.2 работает аналогично.

Результаты компьютерного моделирования ДУ (фиг.8), представленные на графиках (фиг.9-17), подтверждают полученные выше теоретические выводы.

Предлагаемый ДУ может использоваться в структуре быстродействующих операционных усилителей различного функционального назначения, а также в аналоговых микросхемах с широким диапазоном линейной работы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.786.362.

2. Патент США №4.030.044.

3. Патент США №4.059.808, фиг.5.

4. Патент США №4.286.227.

5. Авт.свид. СССР №375754, H03f 3/38.

6. Авт.свид. СССР №843164, H03f 3/30.

7. Патент США №3.660.773.

8. Патент США №4.560.948.

9. Патент РФ №2930041, H03f 1/32.

10. Патент Японии №57-5364, H03f 3/343.

11. Патент ЧССР №134845, кл. 21a2 18/08.

12. Патент ЧССР №134849, кл. 21a2 18/08.

13. Патент ЧССР №135326, кл. 21а2 18/08.

14. Патент США №4.389.579.

15. Патент Англии №1543361, НЗТ.

16. Патент США №5.521.552 (фиг.3а).

17. Патент США №4.059.808.

18. Патент США №5.789.949.

19. Патент США №4.453.134.

20. Патент США №4.760.286.

21. Авт.свид. СССР №1283946.

22. Патент РФ №2019019.

23. Патент США №4.389.579.

24. Патент США №4.453.092.

25. Патент США №3.566.289.

26. Патент США №4.059.808 (фиг.2).

27. Патент США №3.649.926.

28. Патент США №4.714.894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

31. Операционные усилители с непосредственной связью каскадов [Текст] / В.И.Анисимов, М.В.Капитонов, Н.Н.Прокопенко, Ю.М.Соколов. - Л., 1979. - 148 с.

Входной каскад быстродействующего операционного усилителя, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого (3) и второго (4) выходных транзисторов с объединенными базами, первый (5) и второй (6) вспомогательные транзисторы, базы которых соединены с соответствующими базами первого (1) и второго (2) входных транзисторов и подключены к соответствующим первому (7) и второму (8) входам устройства, первый (9) и второй (10) прямосмещенные p-n-переходы, включенные в эмиттеры соответствующих первого (5) и второго (6) вспомогательных транзисторов, первый (11) токостабилизирующий двухполюсник, токовые выходы устройства (12), (13), (14), (15), связанные с коллекторами первого (1) и второго (2) входных транзисторов, а также коллекторами первого (3) и второго (4) выходных транзисторов, причем коллекторы первого (5) и второго (6) вспомогательных транзисторов связаны с первой (16) шиной источника питания, отличающийся тем, что между вторым (10) прямосмещенным p-n-переходом, включенным в эмиттер второго (6) вспомогательного транзистора, и второй (17) шиной источника питания включен первый (11) токостабилизирующий двухполюсник, между первым (9) прямосмещенным p-n-переходом, включенным в эмиттер первого (5) вспомогательного транзистора, и второй (17) шиной источника питания включен второй (18) токостабилизирующий двухполюсник, между общим узлом (19) первого (9) прямосмещенного p-n-перехода и второго (18) токостабилизирующего двухполюсника, а также общим узлом (20) второго (12) прямосмещенного p-n-перехода и первого (11) токостабилизирующего двухполюсника последовательно включены третий (21) и четвертый (22) дополнительные резисторы, общий узел (23) которых соединен с базами первого (3) и второго (4) входных транзисторов.