Логический элемент "и" с многозначным внутренним представлением сигналов

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники, автоматики и может быть использовано в различных цифровых структурах и системах автоматического управления, передачи информации. Техническим результатом является повышение быстродействия и создание элементной базы вычислительных устройств, работающих на принципах многозначной линейной алгебры. Устройство содержит входные логические источники тока, токовые зеркала, шины источника питания. 10 ил.

Реферат

Предлагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах используются транзисторные усилительные каскады, реализованные на основе трех токовых зеркал [1-17], работающие в нелинейном режиме по законам булевой алгебры и имеющие по выходу три логических токовых состояния «0», «1», «-1».

В работе [18], а также монографиях соавтора настоящей заявки [19-20] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока. Заявляемое устройство относится к этому типу логических элементов.

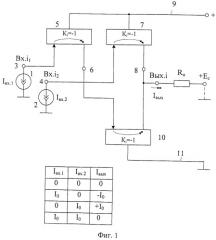

Ближайшим прототипом заявляемого устройства является логический элемент, представленный в патенте US 4.799.026, структура которого присутствует во многих других патентах [1-17]. Он содержит первый 1 и второй 2 входные логические источники тока, связанные с первым 3 и вторым 4 токовыми входами устройства, первое 5 токовое зеркало с основным 6 токовым выходом, вход которого соединен с первым 3 токовым входом устройства, второе 7 токовое зеркало с основным 8 токовым выходом, вход которого соединен со вторым 4 токовым входом устройства, первую 9 шину источника питания, согласованную с первым 5 и вторым 7 токовыми зеркалами, третье 10 токовое зеркало, согласованное со второй 11 шиной источника питания, вход которого соединен с основным 6 токовым выходом первого 5 токового зеркала.

Существенный недостаток известного устройства состоит в том, что он не реализует функцию логического элемента «И».

Основная задача предлагаемого изобретения состоит в создании логического элемента «И», в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [19-20].

Поставленная задача решается тем, что в логическом элементе «И» (фиг.1), содержащем первый 1 и второй 2 входные логические источники тока, связанные с первым 3 и вторым 4 токовыми входами устройства, первое 5 токовое зеркало с основным 6 токовым выходом, вход которого соединен с первым 3 токовым входом устройства, второе 7 токовое зеркало с основным 8 токовым выходом, вход которого соединен со вторым 4 токовым входом устройства, первую 9 шину источника питания, согласованную с первым 5 и вторым 7 токовыми зеркалами, третье 10 токовое зеркало, согласованное со второй 11 шиной источника питания, вход которого соединен с основным 6 токовым выходом первого 5 токового зеркала, предусмотрены новые элементы и связи - первое 5 токовое зеркало содержит первый 12 и второй 13 дополнительные токовые выходы, идентичные его основному 6 токовому выходу, второе 7 токовое зеркало содержит первый 14 и второй 15 дополнительные токовые выходы, идентичные его основному 8 токовому выходу, основной 8 токовый выход второго 7 токового зеркала соединен со входом третьего 10 токового зеркала, первый 12 дополнительный токовый выход первого 5 токового зеркала соединен с инвертирующим входом первого 16 дополнительного токового зеркала, согласованного со второй 11 шиной источника питания, первый 14 дополнительный токовый выход второго 7 токового зеркала соединен с неинвертирующим входом 17 первого 16 дополнительного токового зеркала, второй 13 дополнительный токовый выход первого 5 токового зеркала соединен с неинвертирующим входом 18 второго 19 дополнительного токового зеркала, согласованного со второй 11 шиной источника питания, токовый выход которого соединен с токовым выходом первого 16 дополнительного токового зеркала и подключен к неинвертирующему входу 20 третьего 21 дополнительного токового зеркала, согласованного с первой 9 шиной источника питания, второй 15 дополнительный токовый выход второго 7 токового зеркала соединен с инвертирующим входом второго 19 дополнительного токового зеркала, токовый выход третьего 10 токового зеркала соединен с инвертирующим входом третьего 21 дополнительного токового зеркала, токовый выход которого подключен ко входу четвертого 22 дополнительного токового зеркала, согласованного со второй 11 шиной источника питания, причем токовый выход четвертого 22 дополнительного токового зеркала является токовым выходом устройства 23.

Схема известного устройства показана на чертеже фиг.1.

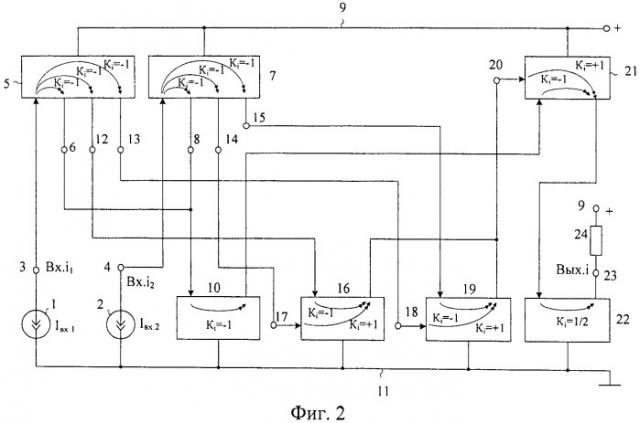

На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

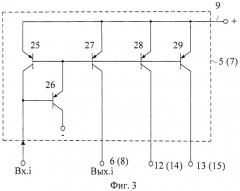

На чертеже фиг.3 приведена схема первого 5 и второго 7 токовых зеркал.

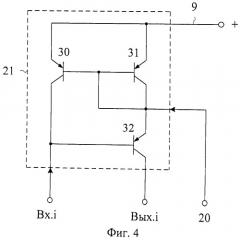

На чертеже фиг.4 представлен возможный вариант построения третьего 21 дополнительного токового зеркала.

Возможный вариант построения третьего 10 токового зеркала и четвертого 22 дополнительного токового зеркала показан на чертеже фиг.5.

Схема фиг.6 характеризует возможные варианты построения первого 16 и второго 19 дополнительных токовых зеркал.

На чертеже фиг.7 приведена схема заявляемого устройства для моделирования в среде МС9.

На чертеже фиг.8 показаны временные диаграммы входных токов и выходного тока функции min (xl, х2) схемы фиг.7.

На чертеже фиг.9 показан выходной ток схемы фиг.7 в увеличенном временном масштабе в момент включения входного тока.

Логический элемент «И» с многозначным представлением внутренних сигналов фиг.2 содержит первый 1 и второй 2 входные логические источники тока, связанные с первым 3 и вторым 4 токовыми входами устройства, первое 5 токовое зеркало с основным 6 токовым выходом, вход которого соединен с первым 3 токовым входом устройства, второе 7 токовое зеркало с основным 8 токовым выходом, вход которого соединен со вторым 4 токовым входом устройства, первую 9 шину источника питания, согласованную с первым 5 и вторым 7 токовыми зеркалами, третье 10 токовое зеркало, согласованное со второй 11 шиной источника питания, вход которого соединен с основным 6 токовым выходом первого 5 токового зеркала. Первое 5 токовое зеркало содержит первый 12 и второй 13 дополнительные токовые выходы, идентичные его основному 6 токовому выходу, второе 7 токовое зеркало содержит первый 14 и второй 15 дополнительные токовые выходы, идентичные его основному 8 токовому выходу, основной 8 токовый выход второго 7 токового зеркала соединен со входом третьего 10 токового зеркала, первый 12 дополнительный токовый выход первого 5 токового зеркала соединен с инвертирующим входом первого 16 дополнительного токового зеркала, согласованного со второй 11 шиной источника питания, первый 14 дополнительный токовый выход второго 7 токового зеркала соединен с неинвертирующим входом 17 первого 16 дополнительного токового зеркала, второй 13 дополнительный токовый выход первого 5 токового зеркала соединен с неинвертирующим входом 18 второго 19 дополнительного токового зеркала, согласованного со второй 11 шиной источника питания, токовый выход которого соединен с токовым выходом первого 16 дополнительного токового зеркала и подключен к неинвертирующему входу 20 третьего 21 дополнительного токового зеркала, согласованного с первой 9 шиной источника питания, второй 15 дополнительный токовый выход второго 7 токового зеркала соединен с инвертирующим входом второго 19 дополнительного токового зеркала, токовый выход третьего 10 токового зеркала соединен с инвертирующим входом третьего 21 дополнительного токового зеркала, токовый выход которого подключен ко входу четвертого 22 дополнительного токового зеркала, согласованного со второй 11 шиной источника питания, причем токовый выход четвертого 22 дополнительного токового зеркала является токовым выходом устройства 23.

Схема первого 5 и второго 7 токовых зеркал, приведенная на чертеже фиг.3, содержит транзисторы 25, 26, 27, 28 и 29.

Представленный на чертеже фиг.4 возможный вариант построения третьего 21 дополнительного токового зеркала содержит транзисторы 30, 31, 32.

Возможный вариант построения третьего 10 токового зеркала и четвертого 22 дополнительного токового зеркала, показанный на чертеже фиг.5, содержит транзисторы 33-35.

Схема фиг.6, характеризующая возможные варианты построения первого 16 и второго 19 дополнительных токовых зеркал, содержит транзисторы 36, 37, 38.

Рассмотрим работу предлагаемой схемы ЛЭ фиг.2.

Синтез логической функции «2-И» производится на основе ее многозначного аналога, описываемого выражением

& x 1 x 2 = min ( x 1 , x 2 ) k = 2 = | x 1 + x 2 | − | x 1 − x 2 | 2 , ( 1 )

где k - значность логики [19, 20],

х1, х2 - входные логические токовые сигналы.

Входные логические сигналы логического элемента «2-И» поступают от источников токов 1 и 2 в виде квантов тока I0 на входы токовых зеркал 5 и 7. Если входные сигналы (по отдельности или вместе) равны «лог.0» (отсутствие кванта тока), то на выходах токовых зеркал 5 и 7 и схемы в целом кванты тока также будут отсутствовать. При наличии квантов входного тока на выходах токовых зеркал также появляются кванты тока.

Уменьшаемое числителя (модуль суммы входных сигналов) в выражении (1) реализуется монтажным соединением выхода 6 токового зеркала 5 и выхода 8 токового зеркала 7. Результат сложения поступает на вход токового зеркала 10, с помощью которого формируется нужное направление суммы квантов тока I0. Вычитаемое числителя (модуль разности входных сигналов) в выражении (1) представляется в виде

| x 1 − x 2 | = [ x 1 − x 2 ] + [ x 2 − x 1 ] , ( 2 )

при этом принимается x i − x j = { 0 е с л и x ≤ i x j 1 е с л и x i > x j } .

Первая квадратная скобка выражения (2) реализуется монтажным объединением выхода 12 токового зеркала 5 и выхода 14 токового зеркала 7 с помощью дополнительного токового зеркала 16. Аналогично, вторая квадратная скобка выражения (2) реализуется монтажным объединением выхода 13 токового зеркала 5 и выхода 15 токового зеркала 7 с помощью дополнительного токового зеркала 19. Результаты вычитания сигналов в квадратных скобках выражения (2) с выходов токовых зеркал 16 и 19 суммируются с помощью дополнительного токового зеркала 21, а затем делятся на 2 с помощью дополнительного токового зеркала 22. С выхода 23 токового зеркала 22 снимается выходной сигнал схемы в виде кванта втекающего тока.

Как видно из приведенного описания, реализация логической функции «2-И» здесь производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивает малую зависимость функционирования схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Показанные на чертежах фиг.8, фиг.9, фиг.10 результаты моделирования подтверждают указанные свойства заявляемых схем.

Таким образом, рассмотренные схемотехнические решения логического элемента «И» характеризуются многозначным состоянием внутренних сигналов и двоичным представлением сигнала на его токовых входе и токовом выходе и могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US 2009/0237163 fig. 2.

2. Патент US 4.361.815 fig. 3.

3. Патент US 5.371.476 fig. 1.

4. Патентная заявка US 2006/0006910.

5. Патентная заявка US 2008/0032656 fig. 6.

6. Патент US 3.921.090 fig. 2.

7. Патентная заявка US 2010/0097141 fig. 7.

8. Патент US 4.241.315 fig. 4.

9. Патент US RE 030587.

10. Патент США №3.439.542.

11. Патент США №5.880.639.

12. А.св. СССР №361605.

13. Патент ФРГ №2551068.

14. Патент ФРГ №2620999.

15. Патент США №4.267.519.

16. Патент США №4.783.602.

17. Патент США №4.176.323.

18. Малюгин В. Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С.84-93.

19. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

20. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог.- ТРТУ, 2004 г., 118 с.

Логический элемент «И» с многозначным внутренним представлением сигналов, содержащий первый (1) и второй (2) входные логические источники тока, связанные с первым (3) и вторым (4) токовыми входами устройства, первое (5) токовое зеркало с основным (6) токовым выходом, вход которого соединен с первым (3) токовым входом устройства, второе (7) токовое зеркало с основным (8) токовым выходом, вход которого соединен со вторым (4) токовым входом устройства, первую (9) шину источника питания, согласованную с первым (5) и вторым (7) токовыми зеркалами, третье (10) токовое зеркало, согласованное со второй (11) шиной источника питания, вход которого соединен с основным (6) токовым выходом первого (5) токового зеркала, отличающийся тем, что первое (5) токовое зеркало содержит первый (12) и второй (13) дополнительные токовые выходы, идентичные его основному (6) токовому выходу, второе (7) токовое зеркало содержит первый (14) и второй (15) дополнительные токовые выходы, идентичные его основному (8) токовому выходу, основной (8) токовый выход второго (7) токового зеркала соединен со входом третьего (10) токового зеркала, первый (12) дополнительный токовый выход первого (5) токового зеркала соединен с инвертирующим входом первого (16) дополнительного токового зеркала, согласованного со второй (11) шиной источника питания, первый (14) дополнительный токовый выход второго (7) токового зеркала соединен с неинвертирующим входом (17) первого (16) дополнительного токового зеркала, второй (13) дополнительный токовый выход первого (5) токового зеркала соединен с неинвертирующим входом (18) второго (19) дополнительного токового зеркала, согласованного со второй (11) шиной источника питания, токовый выход которого соединен с токовым выходом первого (16) дополнительного токового зеркала и подключен к неинвертирующему входу (20) третьего (21) дополнительного токового зеркала, согласованного с первой (9) шиной источника питания, второй (15) дополнительный токовый выход второго (7) токового зеркала соединен с инвертирующим входом второго (19) дополнительного токового зеркала, токовый выход третьего (10) токового зеркала соединен с инвертирующим входом третьего (21) дополнительного токового зеркала, токовый выход которого подключен ко входу четвертого (22) дополнительного токового зеркала, согласованного со второй (11) шиной источника питания, причем токовый выход четвертого (22) дополнительного токового зеркала является токовым выходом устройства (23).