Матричный потенциальный дешифрато1ьсгъс.шэнлй 1|| пдтс

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 250996

ИЗОБРЕТЕНИЯ

R АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическик

Республик

Зависимое от авт, свидетельства №

Заявлено 16.1.1967 (№ 1126540/18-24) с присоединением заявки №

Приоритет

Опубликовано 26Х111.1969. Бюллетень № 27

Дата опубликования описания ЗОЛ.1970

Кл. 21ат, 36(18

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК Н 03k

УДК 681.325.53(088.8) Авторы изобретения

В. И. Черников и Ю. В. Максимов

Заявитель!

I . 1ъг зйя Я

МАТРИЧНЫЙ ПОТЕНЦИАЛЬНЫЙ ДЕШИФРАТОР Ц

ЬИИИОТЕцд

Предмет изобретения

Изобретение относится к автоматике и вычислительной технике.

Известны дешифраторы, содержащие источник питания, подключенный через резисторы к выходным шинам дешифратора.

В описываемом дешифраторе между источником питания и точками соединения резисторов и выходных шин дешифратора включены ключ и параллельные цепочки, состоящие из последовательно соединенных резисторов и диодов.

Это повышает быстродействие дешифратор а.

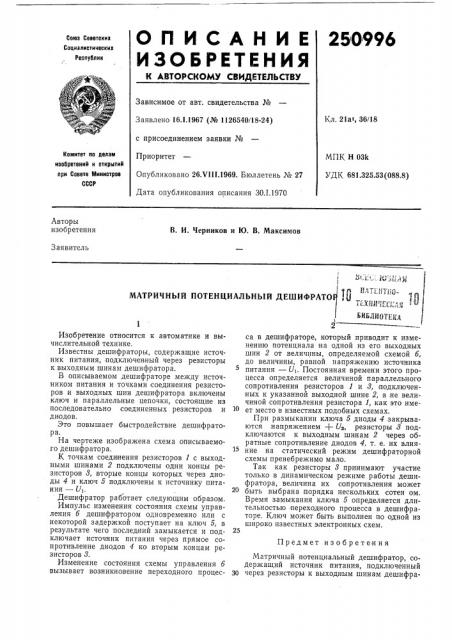

На чертеже изображена схема описываемого дешифратора.

К точкам соединения резисторов 1 с выходными шинами 2 подключены одни концы резисторов 8, вторые концы которых через диоды 4 и ключ 5 подключены к источнику питания — U .

Дешифратор работает следующим образом.

Импульс изменения состояния схемы управления б дешифратором одновременно или с некоторой задержкой поступает на ключ 5, в результате чего последний замыкается и подключает источник питания через прямое сопротивление диодов 4 ко вторым .концам резисторов 8.

Изменение состояния схемы управления б вызывает возникновение переходного процесса в дешифраторе, который приводит к изменению потенциала на одной из его выходных шин 2 от величины, определяемой схемой б, до величины, равной напряжению источника питания — U . Постоянная времени этого процесса определяется величиной параллельного сопротивления резисторов 1 и 8, подключенных к указанной выходной шине 2, а,не величиной сопротивления резистора 1, как это имеет место в известных подобных схемах.

При размыкании ключа 5 диоды 4 закрываются напряжением + U>, резисторы 8 подключаются к выходным шинам 2 через обратные сопротивление диодов 4, т. е. их влияние на статический режим дешифраторн ой схемы пренебрежимо мало.

Так как резисторы 8 принимают участие только в динамическом режиме работы дешифратора, величина их сопротивления может

2о быть выбрана порядка нескольких сотен ом.

Время замыкания ключа 5 определяется длительностью переходного процесса в дешифраторе. Ключ может быть выполнен по одной из широко известных электронных схем.

Матричный потенциальный дешифратор, содержащий источник питания, подключенный

Зо через резисторы к выходным шинам дешифра250996

Г 1

Составитель В. Щеглов

Техред Л. К. Малова Корректоры: А. Николаева и М. Коробова

Редактор П. Метельский

Заказ 3922/9 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва 5К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 тора, отличающийся тем, что, с целью повышения быстродействия, между источником питания и точками соединения резисторов и выходных шин дешифратора включены ключ и параллельные цепочки, состоящие из последовательно соединенных резисторов и диодов.