Запоминающее устройство

Иллюстрации

Показать всеРеферат

25ЮО4

ОПИСАНИЕ

И ЗОБ РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союв Соеетскик

Социалистические

Республик

Зависимое от авт. свидетельства №

Заявлено 05. ?t .1968 (№ 1239073 18-24) Кл. 21а?, 37/04 с присоединением за??в?.?? №

Приоритет

Опубликовано 26Л 111.1969. Бюллетень ¹ 27

Дата опубликован;?я описания 30.1.1970

МПК 6 11с

УД1 681.327.66(088.8) Комитет аа делам изобретений и открытий ари Совете Министров

СССР

Автор изобретения

С. Ь. Торотенков

Заявитель

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

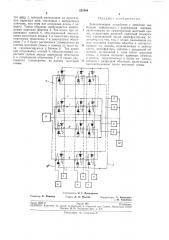

1Р Диоды 1 адресного коммутатора объединяются по группам адресными шинами 5, связаннымц с разрешающими ключами 6. При этом каждая группа диодов 1 состоит из,двух половин, одна половина группы подключена к четным адресным обмоткам, связанным с разрядной обмоткой 7, включенной в одно плечо мостовой схемы, а другая половина группы подключена к нечетным адресным обмоткам, связанным с разрядной обмоткой 8, включсн2Р ной в противоположное плечо мостовой схемы.

Блоки 9 разрядного управления формиру?о? разрядные токи при записи информации и усиливают информационные сигналы при c÷??T?.?ванин информации. Ток по всем адресам задается единым для всего ЗУ формирователем !

О импульсов тока.

При выборке адреса открывается один из ключей 4 и один из ключей 6. Ток, сформиро3р ванный формирователем !О, замыкается через

Изобретение относится к области вычислительной техники, а именно к запоминающим устройствам цифровых вычислительных машин.

Известны запоминающие устройства с линейной выборкой информации, с разрядными шинами, включенными по симметричной мостовой схеме, содержащие диодный адресный коммутатор, управляемый двумя дешифраторами.

В таких устройствах не компенсируется помеха, обусловленная паразитными емкостями запертых диодов диодного адресного коммутатора и емкостями между адресными и разрядными обмотками.

Предло>кенное устройство отличается тем, что половина адресных обмоток и соответствующих им диодов, подключенных к любому ключу дешифратора, связана с разрядной оомоткой, включенной в одно плечо мостовой схемы, а вторая половина адресных обмоток и диодов, подключенных к этому же кл?очу, связана с разрядной обмоткой, включенной в противоположное плечо мостовой схемы. Это позволяет уменьшить помехи при считывании информации.

На черте>ке приведена схема одного разряда запоминающего устройства.

Диоды 1 адресного коммутатора включены последовательно с адресными обмотками 2, выходные контакты которых объединяются по группам адресными шинами 8, подключенны. ми к подготовительным ключам 4. Подготовительные ключи условно разбиваются через од ??? на четные и нечетные. Все адресные обмотки 2, связанные с четными ключами 4, считаются четными, а все обмотки, связанные с нечетными ключами, — нечетными.

251004

Предмет изобретения

Составитель Н. С. Прокофьева

Техред Л. К. Малова

Редактор Б. Нанкина

Корректоры: А. Николаева и М, Коробова

Заказ 3922/17 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва К-35, Раушская наб., д. 4у5

Типография, пр. Сапунова, 2 тот диод 1, который расположен на пересечении адресных шин, связанных с выбранными ключами, при этом все остальные диоды 1 заперты. Таким образом, возбуждается необходимая адресная обмотка 2. Ток помех при открывании ключей б, обусловленный паразитными емкостями диодов 1 и емкостями между адресными обмотками 2 и разрядными обмотками 7 и 8 будет растекаться симметрично по плечам мостовой схемы, и помехи от этого тока скомпенсируются в блоках 9. Ток помех при открывании ключей 4, обусловленный емкостной связью между адресными обмотками

2 и разрядными обмотками 7 и 8 также растекается симметрично по плечам мостовой схемы.

Запоминающее устройство с линейной выборкой информации, с разрядными шинами, включенными по симметричной мостовой схеме, содержащее диодный адресный коммутатоп, управляемый двумя дешифраторами, отлпчаюжессл тем, что, с целью уменьшения помех, половина адресных обмоток и соответст10 вующих им диодов, подключенных к любому кл:очу дешифратора, связана с разрядной обмоткой, вксиоченной в одно плечо мостовой схемы, а вторая половина адресных обмоток и диодов, подключенных к этому же ключу, 15 связана с разрядной обмоткой, включенной в противоположное плечо мостовой схемы.