Троичный d-триггер (варианты)

Иллюстрации

Показать всеГруппа изобретений относится к устройствам цифровой вычислительной техники, в частности к недвоичной схемотехнике, и предназначена для создания троичных триггеров. Техническим результатом заявляемой группы изобретений является реализация схемотехнических средств, используемых для создания троичных логических устройств в среде интегральной полупроводниковой электроники, за счет включения в их состав троичных D-триггеров. В одном из вариантов троичный D-триггер с записью по уровню содержит узел троичной схемотехники и семь пороговых элементов троичной логики. 4 н.п.ф-лы, 5 ил., 6 табл.

Реферат

Группа изобретений относится к устройствам цифровой вычислительной техники, в частности к недвоичной технике, и предназначена для создания реализуемых в среде полупроводниковой интегральной электроники троичных D-триггеров.

Известной успешной реализацией недвоичных цифровых устройств являются троичные ЦВМ "Сетунь" и "Сетунь 70" [1, 2]. Логические элементы этих ЦВМ выполнены на основе устаревшей электромагнитной техники [6, 7], имеют малое быстродействие, большие потребляемую мощность и размеры. Реализация устройств на этих элементах не может быть выполнена в среде современной полупроводниковой интегральной электроники.

Известен функциональный аналог элементов ЦВМ "Сетунь" - "Пороговый Элемент Троичной Логики" (ПЭТЛ), реализуемый в среде современной полупроводниковой интегральной электроники [4]. На основе ПЭТЛ, используя специальную ПЭТЛ-схемотехнику [3], можно создавать троичные цифровые устройства. Ассортимент типовых узлов и схемных решений, которыми располагает на данный момент ПЭТЛ-схемотехника, недостаточен для реализации всего спектра троичных устройств. В частности, в нем отсутствуют троичные триггеры, без которых нельзя построить троичные регистры и счетчики.

Задача, решаемая заявляемой группой изобретений, направлена на пополнение ассортимента средств ПЭТЛ-схемотехники триггерами, благодаря чему становится возможной реализация полного набора логических и операционных устройств, использующих симметричную троичную систему с цифрами -1, 0, +1, в среде интегральной полупроводниковой электроники.

Наиболее близкими техническими решениями к заявляемой группе изобретений являются: "Пороговый Элемент Троичной Логики и устройства на его основе" [4] и "Узел Троичной схемотехники и дешифраторы-переключатели на его основе" [5].

Известная группа изобретений имеет ограниченные возможности, так как позволяет реализовывать только комбинационные схемы: троичную схему "И", троичный полусумматор, троичные дешифраторы и переключатели разной разрядности и на разное число направлений. Реализацию троичных триггеров известная группа изобретений не раскрывает.

Техническим результатом заявляемой группы изобретений является пополнение ассортимента средств ПЭТЛ-схемотехники четырьмя вариантами троичных D-триггеров: два варианта с записью по уровню сигнала управления и два варианта с записью по фронту сигнала управления.

Раскрытие изобретения

Первым аспектом изобретения являются два варианта Троичного D-триггера с записью по уровню сигнала управления (ТЗУ).

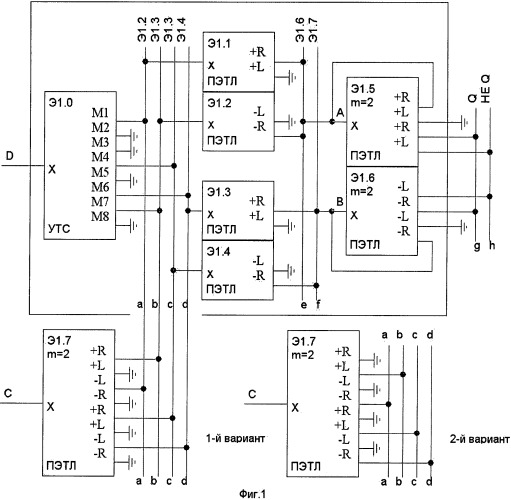

1. Троичный D-триггер с запись по уровню содержит Узел троичной схемотехники (УТС) и семь Пороговых элементов троичной логики (ПЭТЛ), причем пятый, шестой и седьмой ПЭТЛ имеют по две группы выходов, причем вход УТС является входом данных ТЗУ, управляющий вход которого является входом седьмого ПЭТЛ, причем первый выход УТС через первую сборку соединен с входом первого ПЭТЛ, четвертый выход УТС через третью сборку соединен с входом четвертого ПЭТЛ, шестой выход УТС через четвертую сборку соединен с входом третьего ПЭТЛ, седьмой выход УТС через вторую сборку соединен с входом второго ПЭТЛ, +R выход второй группы пятого ПЭТЛ соединен с входом пятого ПЭТЛ, +R выход первой группы пятого ПЭТЛ и -R выход первой группы шестого ПЭТЛ соединены с выходом "Q" ТЗУ, -R выход первой группы шестого ПЭТЛ соединен с входом шестого ПЭТЛ, -R выход второй группы шестого ПЭТЛ и +R выход первой группы пятого ПЭТЛ соединены с выходом "НЕ Q" ТФУ, +R выход второй группы седьмого ПЭТЛ соединен с второй сборкой, +R выход первой группы седьмого ПЭТЛ соединен с третьей сборкой, -L выход второй группы седьмого ПЭТЛ соединен с первой сборкой, -L выход первой группы седьмого ПЭТЛ соединен с четвертой сборкой.

2. Троичный D-триггер с запись по уровню из п.1, отличающийся тем, что +L выход второй группы седьмого ПЭТЛ соединен с второй сборкой, +L выход первой группы седьмого ПЭТЛ соединен с третьей сборкой, -R выход второй группы седьмого ПЭТЛ соединен с первой сборкой, -R выход первой группы седьмого ПЭТЛ соединен с четвертой сборкой.

Вторым аспектом изобретения являются два варианта Троичного D-триггера с записью по фронту сигнала управления (ТЗФ).

3. Троичный D-триггер с записью по фронту содержит троичный D-триггер с записью по уровню из п.1 и троичный D-триггер с записью по уровню из п.2, причем вход данных первого ТЗУ является входом данных ТЗФ, причем управляющий вход первого ТЗУ является управляющим входом ТЗФ, причем +R выход первой группы выходов и -R выход второй группы выходов первого ТЗУ соединены с входом данных второго ТЗУ, причем +R выход первой группы выходов и -R выход второй группы выходов второго ТЗУ соединены с выходом "Q" ТЗФ, +L выход первой группы выходов и -L выход второй группы выходов второго ТФ соединены с выходом "НЕ Q" ТЗФ, причем -L выход второй группы выходов ПЭТЛ соединен с первой сборкой первого ТЗУ, +R выход второй группы выходов ПЭТЛ соединен с второй сборкой первого ТЗУ, +R выход первой группы выходов ПЭТЛ соединен с третьей сборкой первого ТЗУ, -L выход первой группы выходов ПЭТЛ соединен с четвертой сборкой первого ТЗУ, -R выход второй группы выходов ПЭТЛ соединен с первой сборкой второго ТЗУ, +L выход второй группы выходов ПЭТЛ соединен с второй сборкой второго ТЗУ, +L выход первой группы выходов ПЭТЛ соединен с третьей сборкой второго ТЗУ, -R выход первой группы выходов ПЭТЛ соединен с четвертой сборкой второго ТЗУ.

4. Троичный D-триггер с записью по фронту из п.3, отличающийся тем, что -L выход второй группы выходов ПЭТЛ соединен с первой сборкой второго ТЗУ, +R выход второй группы выходов ПЭТЛ соединен с второй сборкой второго ТЗУ, +R выход первой группы выходов ПЭТЛ соединен с третьей сборкой второго ТЗУ, -L выход первой группы выходов ПЭТЛ соединен с четвертой сборкой второго ТЗУ, -R выход второй группы выходов ПЭТЛ соединен с первой сборкой первого ТЗУ, +L выход второй группы выходов ПЭТЛ соединен с второй сборкой первого ТЗУ, +L выход первой группы выходов ПЭТЛ соединен с третьей сборкой первого ТЗУ, -R выход первой группы выходов ПЭТЛ соединен с четвертой сборкой первого ТЗУ.

В описании встречаются термины, требующие пояснений: "Пороговый Элемент Троичной Логики" (ПЭТЛ), "Узел троичной схемотехники" (УТС) и "ПЭТЛ-схемотехника". Хотя необходимые сведения о них содержатся в публикациях и патентах [3, 4, 5], здесь даются краткие объяснения.

1. ПЭТЛ - функциональный аналог логического элемента (ячейки) троичных ЭВМ "Сетунь" и "Сетунь-70" [1, 2]. Прототипом ПЭТЛ является элемент ЭСЛ-схемотехники [8], модифицированный добавлением симметричной реплики на р-n-р транзисторах.

2. УТС - многофункциональный узел, содержащий три ПЭТЛ.

3. ПЭТЛ-схемотехника - совокупность элементов и узлов, правил их соединения, схемных решений и изобразительных средств, применяя которые можно реализовывать цифровые устройства, использующие троичную систему с цифрами +1, 0, -1, в среде интегральной полупроводниковой электроники.

ПЭТЛ-схемотехника появилась недавно (патент на ПЭТЛ получен 2009 г., а на УТС - в 2012 г.). На момент подачи заявки описаны лишь комбинационные схемы на ПЭТЛ.

ПЭТЛ является функциональным аналогом ячеек "Сетуней", однако использовать схемные решения "Сетуней" при создании устройств на ПЭТЛ нельзя.

Прототипом ПЭТЛ является ЭСЛ-элемент, однако решения из арсенала ЭСЛ-схемотехники не применимы в устройствах на ПЭТЛ. У ПЭТЛ сигналами межэлементных связей являются дискретные разнополярные токи, на которых реализуется троичная пороговая логика [6].

ПЭТЛ и УТС изображены на Фиг.1 в виде прямоугольников, внутри которых внизу указан тип. Они имеют один вход Х и несколько выходов. Как преобразователи дискретных троичных значений на входах ПЭТЛ и УТС описываются следующим образом. На вход Х поступают в параллель n дискретных сигналов, каждый из которых имеет одно из трех значений: +1, 0 или -1 (на физическом уровне это дискретные токи +Iф, 0, -Iф).

n=n+1+n-1+n0,

где n+1 - число сигналов, текущие значения которых +1;

n-1 - число сигналов, текущие значения которых -1;

n0 - число сигналов, текущие значения которых 0.

Выполняемое на входе Х преобразование описывается трехзначной функцией TS(n+1,n-1), определенной выражением:

T S ( n + 1 , n − 1 ) = { + 1, е с л и ( n + 1 − n − 1 ) > 0 0, е с л и ( n + 1 − n − 1 ) = 0 − 1, е с л и ( n + 1 − n − 1 ) < 0 ( 1 )

Значениям TS(n+1,n-1) на входах ПЭТЛ и УТС соответствуют двоичные значения на их выходах: +R, +L, -R, -L (ПЭТЛ) и М1, М2, М3, М4, М5, М6, М7, М8 (УТС). Это соответствие дано в Таблицах 1 и 2.

| Таблица 1 (ПЭТЛ) | |||

| TS(n+1,n-1) | +1 | 0 | -1 |

| +R | +1 | 0 | 0 |

| -R | 0 | 0 | -1 |

| +L | 0 | +1 | +1 |

| -L | -1 | -1 | 0 |

| Таблица 2 (УТС) | |||

| TS(n+1,n-1) | +1 | 0 | -1 |

| M1 | +1 | 0 | 0 |

| M2 | 0 | +1 | +1 |

| M3 | -1 | -1 | 0 |

| M4 | 0 | 0 | -1 |

| M5 | 0 | 0 | +1 |

| М6 | +1 | +1 | 0 |

| М7 | 0 | -1 | -1 |

| М8 | -1 | 0 | 0 |

Хотя в таблицах 1 и 2 фигурируют троичные значения, значения на каждом из выходов ПЭТЛ и УТС двоичные: +1 или 0 на выходах +R, +L, M1, M2, M5, M6; -1 или 0 на выходах -R, -L, M3, M4, М7, М8.

Возможна ситуация, когда из четырех выходов ПЭТЛ в конкретном устройстве используется только два: +R, +L или -R, -L. В таких случаях не используемые выходы не изображаются. На Фиг.1 у Э1.1,3,5 (не показаны -R, -L), у Э1.2,4,6 (не показаны +R, +L).

ПЭТЛ и УТС могут иметь более одной группы выходов: +R, +L, -R, -L и M1, М2, М3, М4, М5, М6, М7, М8. Текущие значения на одноименных выходах групп тождественны. Если число групп m>1, оно указывается вверху слева (на Фиг.1 m=2 у 31.5,6,1).

Пороговое преобразование TS(n+1,n-1) (1) и объединение (сборка) выходов ПЭТЛ и УТС составляют ассортимент средств ПЭТЛ-схемотехники. Например, объединяя +R и -R, получим на выходе повторение входного троичного значения, объединяя +L и -L - нециклическую инверсию входного троичного значения, объединяя +R и +L или -R и -L - постоянные значения +1 или -1 для любого значения на входе. Допускается объединение выходов разных ПЭТЛ и УТС. Так реализованы, в частности, троичная двухвходовая схема "И", троичный полусумматор, троичные дешифраторы-переключатели, описанные в [4, 5].

Выходы в ПЭТЛ-схемотехнике - высокоомные источники тока. Свободные выходы должны быть присоединены к земляной шине.

Терминология троичной цифровой техники не устоялась. Используются термины из двоичной техники и из лексикона "Сетуней". Для исключения двусмысленностей необходимо руководствоваться таблицами истинности.

Для изображения устройств на основе ПЭТЛ-схемотехники применен следующий графический прием: объединения (сборки) выходов имеют вид вертикальных линий, нижние концы которых помечены буквами, а верхние (необязательно) либо наименованием элемента, к входу которого данная сборка подключена, либо названием сигнала на выходе устройства. Слева от сборки располагаются элементы, выходы которых к ней подключены, справа - элементы или выходы, на которые поступают сформированные сигналы.

Триггеры в цифровой технике обычно реализуются соединением "в кольцо" двух инверторов [8]. Образующийся усилитель с сильной положительной обратной связью имеет два устойчивых состояния. Аналогичным образом можно реализовать устройство с тремя устойчивыми состояниями, соединив "в кольцо" два ПЭТЛ, включенных как нециклические инверторы (+L и -L объединены). В ПЭТЛ-схемотехнике имеется другая возможность выполнения триггеров. Эта возможность реализована в заявке.

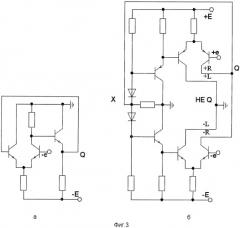

На Фиг.3,а приведена упрощенная электрическая схема двоичного ЭСЛ-элемента (прототипа ПЭТЛ), в которой выход Q соединен со входом. Схема представляет собой двоичный триггер с эмиттерной связью и может находиться в одном из двух устойчивых состояний (ток, втекающий в объединенные эмиттеры, проходит либо через правый, либо через левый транзисторы).

На Фиг.3,б дана упрощенная электрическая схема ПЭТЛ. Соединив повторяющий выход Q (+R и -R объединены) со входом X, получим триггерный узел с тремя устойчивыми состояниями +1, 0, -1 (токи, втекающие в объединенные эмиттеры р-n-р и n-р-n транзисторов, проходят по ветвям +R, -L; +L, -L; +L, -R соответственно).

Триггерный узел на Фиг.1 реализован на двух ПЭТЛ (Э1.5 и Э1.6). Он имеет два входа А и В и один выход Q. Манипулируя сигналами А и В, можно управлять верхней и нижней половинами триггера по отдельности в соответствии с Таблицей 3.

| Таблица 3 | ||||

| А | +1 | -1 | -1 | 0 |

| В | +1 | +1 | -1 | 0 |

| Q | +1 | 0 | -1 | Б/И |

В нижней строке Таблицы 3 даны состояния (сигналы) на выходе Q триггера, в которые он устанавливается при подаче на входы А и В сигналов +1, 0, -1. Сигналы +1 на обоих входах устанавливают верхний триггер и сбрасывают нижний; сигналы -1 устанавливают нижний триггер и сбрасывают верхний. Если на входах А и В нуль - текущее состояние триггера не изменяется (Б/И).

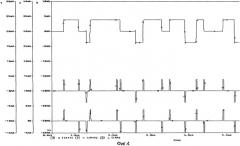

На Фиг.4 даны результаты моделирования триггерного узла, на двух ПЭТЛ, в системе Pspice [9]. Эпюры 1 и 2 - токовые сигналы, подаваемые соответственно на входы А и В, эпюра 3 - токовый сигнал на выходе Q. Моделирование подтверждает функционирование троичного триггера в соответствии с приведенным описанием.

Троичный D-триггер с записью по уровню (ТЗУ) изображен на Фиг.1. Триггер запоминает троичное значение +1, 0, -1 на входе D в зависимости от значений сигнала на входе С. Описываются два варианта ТЗУ.

В 1-м варианте триггер запоминает значение на входе D, если С=+1. Если С=-1, вход D отключен и триггер сохраняет старое значение.

Функционирование ТЗУ описывается Таблицей 4, алгоритм заполнения которой следующий:

1) для данной ячейки таблицы фиксируют текущие значения D и С;

2) определяют текущие значения на выходах элементов, подключенных к сборке этой ячейки, соответствующие текущим значениям D и С;

3) к этим значениям применяют преобразование (1); результат заносят в ячейку;

4) переходят к другой ячейке сборки, по завершении - к ячейкам других сборок.

| Таблица 4 | ||||||

| С | -1 | +1 | ||||

| D | +1 | 0 | -1 | +1 | 0 | -1 |

| а | 0 | -1 | -1 | +1 | 0 | 0 |

| b | +1 | 0 | 0 | 0 | -1 | -1 |

| с | +1 | +1 | 0 | 0 | 0 | -1 |

| d | 0 | 0 | -1 | +1 | +1 | 0 |

| е (А) | 0 | 0 | 0 | +1 | -1 | -1 |

| f (В) | 0 | 0 | 0 | +1 | +1 | -1 |

| g (Q) | Предшествующие значения | +1 | 0 | -1 | ||

| h (HE Q) | -1 | 0 | +1 |

Примечание: при заполнении ячеек в строках А и В Таблицы 4 не учитываются сигналы обратной связи с выходов ПЭТЛ Э1.5 и Э1.6.

Во 2-м варианте триггер запоминает значение на входе D, если С=-1. Если С=+1, вход D отключен и триггер сохраняет старое значение. Работа ТЗУ также описывается Таблицей 3, если поменять в верхней строке знаки С на противоположные.

Приведенное формальное описание работы ТЗУ основано на формальном описании УТС и ПЭТЛ. Дадим содержательное описание.

Сигналы на входах А и В формирует УТС Э1.0 на сборках a, b, c, d и входах ПЭТЛ Э1.1-Э1.4 (для каждого из входов А и В отдельно положительные и отрицательные). Если С=+1, на сборки a, b, c, d с выходов ПЭТЛ Э1.7 подаются нули и сигналы с выходов ПЭТЛ Э1.1-Э1.4 поступают на сборки е и f и на входы А и В. Если С=-1, на сборки a и d поступают -1, на сборки b и с - +1. ПЭТЛ Э1.1 -Э1.4 при этом заперты по входам, а на их выходах, сборках е и f и входах А и В - нули. Изменения состояний триггера не происходит. Ситуация С=0 запрещена.

Троичный D-триггер с записью по фронту (ТЗФ) изображен на Фиг.2. Описываются два варианта ТЗФ.

В 1-м варианте триггер запоминает значение на входе D в момент, когда значение на управляющем входе С изменяется с -1 на +1 (т.е. по положительному фронту).

В 2-м варианте триггер запоминает значение на входе D в момент, когда значение на управляющем входе С изменяется с +1 на -1 (т.е. по отрицательному фронту).

ТЗФ представляет собой два ТЗУ (совпадающие части схем обоих триггеров, чтобы не загромождать рисунка, показаны без детализации в незамкнутых прямоугольных рамках). Выход первого ТЗУ соединен с входом второго.

Опишем функционирование ТЗФ по 1-му варианту.

Таблица 5 связывает значения на входе С с значениями на двух четверках сборок: a, b, c, d (первый ТЗУ) и a1, b1, c1, d1 (второй ТЗУ), подключенных к выходам ПЭТЛ Э2.3.

| Таблица 5 | ||||||||

| С | а | b | с | d | a1 | b1 | d | d1 |

| +1 | +1 | -1 | -1 | +1 | 0 | 0 | 0 | 0 |

| -1 | 0 | 0 | 0 | 0 | +1 | -1 | -1 | +1 |

Если С=-1, то a=b=c=d=0 и разрешена запись в первый ТЗУ с входа D. Если С=+1, то a1=b1=c1=d1=0 и разрешена запись в второй ТЗУ с выхода Q1 первого ТЗУ, который в это время заперт по входу. Когда в один из ТЗУ запись разрешена, в другой запрещена. Данные на входе D сохраняются в первом триггере (С=-1), а затем, когда он отключается от входа D (С=+1), копируются во второй. Ситуация С=0 запрещена.

Сказанное иллюстрируется Таблицей 6, на которой видно, как данные с входа D перемещаются от первого триггера ко второму при последовательных изменениях на управляющем входе С с -1 на +1.

| Таблица 6 | ||||||||

| С | -1 | +1 | -1 | +1 | -1 | +1 | -1 | +1 |

| D | D1 | D2 | D3 | D4 | ||||

| Q1 | D1 | D2 | D3 | D4 | ||||

| Q | D0 | D1 | D2 | D3 | D4 |

D0, D1, D2, D3 и D4 - произвольные троичные значения на входе D. Функционирование ТЗФ по 2-му варианту отличается тем, что запись в первый ТЗУ с входа D происходит при С=+1. Если С=-1, разрешена запись в второй ТЗУ с выхода Q1 первого ТЗУ, который в это время заперт по входу. Для описания ТЗФ по 2-му варианту следует в Таблицах 5 и 6 поменять знаки всех С на противоположные.

Литература

1. Брусенцов Н.П., Маслов С.П., Розин В.П., Тишулина A.M. Малая цифровая вычислительная машина "Сетунь". - М.: Изд-во Московского университета, 1965. 145 с.

2. Брусенцов Н.П., Жоголев Е.А., Маслов С.П., Рамиль Альварес X. Опыт создания троичных цифровых машин. // Компьютеры в Европе. Прошлое, настоящее и будущее. - Киев: Феникс, 1998. С.67-71.

3. Маслов С.П. Об одной возможности реализации троичных цифровых устройств. Тематический сборник №12 "Программные системы и инструменты". М.: Изд-во факультета ВМиК МГУ, 2011.

4. Маслов С.П. Пороговый элемент троичной логики и устройства на его основе. Патент РФ на изобретение №2394366 С1. Зарегистрирован: 10.07.2010.

5. Маслов С.П. Узел троичной схемотехники и дешифраторы-переключатели на его основе. Патент РФ на изобретение №2461122 С1. Зарегистрирован: 10.09.2012.

6. Брусенцов Н.П. Пороговая реализация трехзначной логики электромагнитными средствами. // Вычислительная техника и вопросы кибернетики. Вып.9. - М.: Изд-во Моск. ун-та, 1972. С.3-35.

7. Брусенцов Н.П. Электромагнитные цифровые устройства с однопроводной передачей трехзначных сигналов. - В кн.: Магнитные элементы автоматики и вычислительной техники. XIV Всесоюзное совещание (Москва, сентябрь 1972 г.). М.: "Наука", 1972, с.242-244.

8. Шило В.Л. Популярные цифровые микросхемы. Изд-во "Металлург", Челябинское отд., 1989, 352 с.: (Массовая радиобиблиотека Вып.1111), с.285-295.

9. Хайнеман Р. Визуальное моделирование электронных схем в PSPICE. Пер. с нем. - М.: "ДМК Пресс", 2008. - 336 с.

1. Троичный D-триггер с записью по уровню сигнала управления (ТЗУ), состоящий из Узла троичной схемотехники (УТС) и семи Пороговых элементов троичной логики (ПЭТЛ), причем пятый, шестой и седьмой ПЭТЛ имеют по две группы выходов, причем вход УТС является входом данных ТЗУ, управляющий вход которого является входом седьмого ПЭТЛ, причем первый выход УТС через первую сборку соединен с входом первого ПЭТЛ, четвертый выход УТС через третью сборку соединен с входом четвертого ПЭТЛ, шестой выход УТС через четвертую сборку соединен с входом третьего ПЭТЛ, седьмой выход УТС через вторую сборку соединен с входом второго ПЭТЛ, второй, третий, пятый и восьмой выходы УТС соединены с земляной шиной, положительный R выход первого ПЭТЛ и отрицательный R выход второго ПЭТЛ через пятую сборку соединены с входом пятого ПЭТЛ и положительный L выход первого ПЭТЛ и отрицательный L выход второго ПЭТЛ соединены с земляной шиной, положительный R выход третьего ПЭТЛ и отрицательный R выход четвертого ПЭТЛ через шестую сборку соединены с входом шестого ПЭТЛ и положительный L выход третьего ПЭТЛ и отрицательный L выход четвертого ПЭТЛ соединены с земляной шиной, положительный R выход второй группы пятого ПЭТЛ соединен с входом пятого ПЭТЛ, положительный R выход первой группы пятого ПЭТЛ и отрицательный R выход первой группы шестого ПЭТЛ соединены с выходом "Q" ТЗУ, положительный L выход первой группы пятого ПЭТЛ соединен с земляной шиной, отрицательный R выход первой группы шестого ПЭТЛ соединен с входом шестого ПЭТЛ, отрицательный L выход первой группы шестого ПЭТЛ и положительный L выход второй группы пятого ПЭТЛ соединены с выходом "НЕ Q" ТЗУ, положительный R выход второй группы седьмого ПЭТЛ соединен с второй сборкой, положительный R выход первой группы седьмого ПЭТЛ соединен с третьей сборкой, отрицательный L выход второй группы седьмого ПЭТЛ соединен с первой сборкой, отрицательный L выход первой группы седьмого ПЭТЛ соединен с четвертой сборкой, положительный L выход и отрицательный R выход второй группы седьмого ПЭТЛ, положительный L выход и отрицательный R выход первой группы седьмого ПЭТЛ соединены с земляной шиной.

2. Троичный D-триггер с записью по уровню сигнала управления (ТЗУ), состоящий из Узла троичной схемотехники (УТС) и семи Пороговых элементов троичной логики (ПЭТЛ), причем пятый, шестой и седьмой ПЭТЛ имеют по две группы выходов, причем вход УТС является входом данных ТЗУ, управляющий вход которого является входом седьмого ПЭТЛ, причем первый выход УТС через первую сборку соединен с входом первого ПЭТЛ, четвертый выход УТС через третью сборку соединен с входом четвертого ПЭТЛ, шестой выход УТС через четвертую сборку соединен с входом третьего ПЭТЛ, седьмой выход УТС через вторую сборку соединен с входом второго ПЭТЛ, второй, третий, пятый и восьмой выходы УТС соединены с земляной шиной, положительный R выход первого ПЭТЛ и отрицательный R выход второго ПЭТЛ через пятую сборку соединены с входом пятого ПЭТЛ и положительный L выход первого ПЭТЛ и отрицательный L выход второго ПЭТЛ соединены с земляной шиной, положительный R выход третьего ПЭТЛ и отрицательный R выход четвертого ПЭТЛ через шестую сборку соединены с входом шестого ПЭТЛ и положительный L выход третьего ПЭТЛ и отрицательный L выход четвертого ПЭТЛ соединены с земляной шиной, положительный R выход второй группы пятого ПЭТЛ соединен с входом пятого ПЭТЛ, положительный R выход первой группы пятого ПЭТЛ и отрицательный R выход первой группы шестого ПЭТЛ соединены с выходом "Q" ТЗУ, положительный L выход первой группы пятого ПЭТЛ соединен с земляной шиной, отрицательный R выход первой группы шестого ПЭТЛ соединен с входом шестого ПЭТЛ, отрицательный L выход первой группы шестого ПЭТЛ и положительный L выход второй группы пятого ПЭТЛ соединены с выходом "НЕ Q" ТЗУ, положительный L выход второй группы седьмого ПЭТЛ соединен с второй сборкой, положительный L выход первой группы седьмого ПЭТЛ соединен с третьей сборкой, отрицательный R выход второй группы седьмого ПЭТЛ соединен с первой сборкой, отрицательный R выход первой группы седьмого ПЭТЛ соединен с четвертой сборкой, положительный R выход и отрицательный L выход второй группы седьмого ПЭТЛ, положительный R выход и отрицательный L выход первой группы седьмого ПЭТЛ соединены с земляной шиной.

3. Троичный D-триггер с записью по фронту сигнала управления (ТЗФ), состоящий из троичного D-триггера с записью по уровню из п.1 и троичного D-триггера с записью по уровню из п.2, причем вход данных первого ТЗУ является входом данных ТЗФ, причем управляющий вход первого ТЗУ является управляющим входом ТЗФ, причем положительный R выход первой группы выходов и отрицательный R выход второй группы выходов первого ТЗУ соединены с входом данных второго ТЗУ, причем положительный R выход первой группы выходов и отрицательный R выход второй группы выходов второго ТЗУ соединены с выходом "Q" ТЗФ, положительный L выход первой группы выходов и отрицательный L выход второй группы выходов второго ТФ соединены с выходом "НЕ Q" ТЗФ, причем положительный L выход первой группы выходов, положительный L выход второй группы выходов, отрицательный L выход первой группы выходов и отрицательный L выход второй группы выходов первого ТЗУ соединены с земляной шиной, причем отрицательный L выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с первой сборкой первого ТЗУ, положительный R выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с второй сборкой первого ТЗУ, положительный R выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с третьей сборкой первого ТЗУ, отрицательный L выход первой группы выходов ПЭТЛ соединен с четвертой сборкой первого ТЗУ, отрицательный R выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с первой сборкой второго ТЗУ, положительный L выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с второй сборкой второго ТЗУ, положительный L выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с третьей сборкой второго ТЗУ, отрицательный R выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с четвертой сборкой второго ТЗУ.

4. Троичный D-триггер с записью по фронту сигнала управления (ТЗФ), состоящий из троичного D-триггера с записью по уровню из п.1 и троичного D-триггера с записью по уровню из п.2, причем вход данных первого ТЗУ является входом данных ТЗФ, причем управляющий вход первого ТЗУ является управляющим входом ТЗФ, причем положительный R выход первой группы выходов и отрицательный R выход второй группы выходов первого ТЗУ соединены с входом данных второго ТЗУ, причем положительный R выход первой группы выходов и отрицательный R выход второй группы выходов второго ТЗУ соединены с выходом "Q" ТЗФ, положительный L выход первой группы выходов и отрицательный L выход второй группы выходов второго ТФ соединены с выходом "НЕ Q" ТЗФ, причем положительный L выход первой группы выходов, положительный L выход второй группы выходов, отрицательный L выход первой группы выходов и отрицательный L выход второй группы выходов первого ТЗУ соединены с земляной шиной, отрицательный L выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с первой сборкой второго ТЗУ, положительный R выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с второй сборкой второго ТЗУ, положительный R выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с третьей сборкой второго ТЗУ, отрицательный L выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с четвертой сборкой второго ТЗУ, отрицательный R выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с первой сборкой первого ТЗУ, положительный L выход второй группы выходов седьмого ПЭТЛ первого ТЗУ соединен с второй сборкой первого ТЗУ, положительный L выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с третьей сборкой первого ТЗУ, отрицательный R выход первой группы выходов седьмого ПЭТЛ первого ТЗУ соединен с четвертой сборкой первого ТЗУ.