Устройство отображения

Иллюстрации

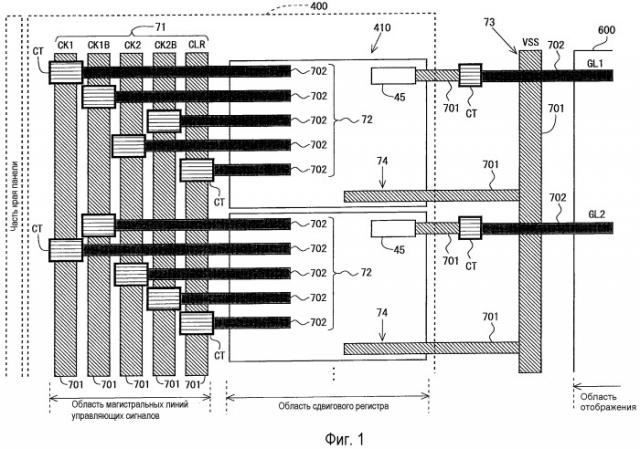

Показать всеИзобретение относится к устройствам отображения с активной матрицей. Устройство отображения содержит магистральные соединительные линии (71) управляющих сигналов, которые передают управляющие сигналы, такие как тактовые сигналы, сформированные из металлической пленки (701) истока в области на противоположной стороне области отображения относительно области сдвигового регистра. Магистральная соединительная линия (73) VSS для передачи низкоуровневого потенциала электропитания постоянного тока сформирована из металлической пленки (701) истока в области между областью сдвигового регистра и областью отображения. Каждая из бистабильных схем, формирующих сдвиговый регистр (410), и магистральная соединительная линия (71) управляющего сигнала соединены ответвленной соединительной линией (72) управляющего сигнала, сформированным из металлической пленки (702) затвора. Каждая бистабильная схема и магистральная соединительная линия (73) VSS соединены ответвленной соединительной линией (74) VSS, сформированным из металлической пленки (701) истока. Технический результат заключается в уменьшении расхода энергии питания без ухудшения качества отображения. 8 з.п. ф-лы, 20 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение имеет отношение к устройству отображения с активной матрицей и, в частности, имеет отношение к схеме расположения компонентов управляющей схемы линии сигналов сканирования и области вблизи нее в устройстве отображения.

УРОВЕНЬ ТЕХНИКИ

Традиционно в жидкокристаллическом устройстве отображения, использующем жидкокристаллическую панель c аморфным кремнием для полупроводниковых слоев тонкопленочных транзисторов, поскольку мобильность аморфного кремния относительно мала, драйвер затвора для управления линиями шин затвора (линиями сигналов сканирования) установлен в области вокруг подложки, составляющей панель, как интегральная микросхема (IC). Однако в последние годы, чтобы достигнуть миниатюризации, сокращения стоимости устройства и т.д., было выполнено формирование драйвера затвора непосредственно на подложке. Такой драйвер затвора называют "монолитным драйвером затвора" и т.д. Панель, включающая в себя монолитный драйвер затвора, называют "монолитной панелью с драйвером затвора" и т.д.

Фиг.21 показывает иллюстративную схему расположения компонентов драйвера затвора (монолитного драйвера затвора) в традиционном жидкокристаллическом устройстве отображения, использующем монолитную панель с драйвером затвора. Как показано на Фиг.21, драйвер затвора включает в себя сдвиговый регистр, сформированный множеством каскадов для последовательного управления множеством линий шин затвора (линий сигналов сканирования), расположенных в блоке отображения; и соединительные линии, которые передают тактовые сигналы и т.д. для того, чтобы дать возможность работать сдвиговому регистру. Каждый каскад сдвигового регистра представляет собой бистабильную схему, которая находится в одном из двух состояний (первое состояние и второе состояние) в каждый момент времени и выдает сигнал, указывающий состояние (сигнал состояния), когда сигнал сканирования проходит через выходной транзистор (транзистор, соединенный одним своим выводом с выходным выводом сигнала сканирования и управляющий потенциалом сигнала состояния посредством изменения потенциала на выводе управления транзистора). Следует отметить, что Фиг.21 показывает схему расположения компонентов только двух каскадов сдвигового регистра. Для соединительных линий на подложке сформированы магистральные соединительные линии управляющих сигналов, которые передают тактовые сигналы CK1, CK1B, CK2 и CK2B и сигнал очистки CLR для инициализации состояния каждой бистабильной схемы; магистральная соединительная линия VSS, которая передает низкоуровневый потенциал электропитания постоянного тока VSS; и ответвленные соединительные линии, которые соединяют магистральные соединительные линии управляющих сигналов и магистральную соединительную линию VSS с каждой бистабильной схемой. Следует отметить, что в дальнейшем область, в которой сформирован сдвиговый регистр, называется "областью сдвигового регистра", область, в которой сформированы магистральные соединительные линии для управляющего сигнала и VSS, называется "областью магистральных соединительных линий", и область, соответствующая блоку отображения, называется "областью отображения".

Между тем в общем случае, когда схема формируется, часть схемы размещена таким образом, что она является смежной с входной секцией, и выходная секция расположена таким образом, что она является смежной с секцией схемы. В традиционном монолитном драйвере затвора, как показано на Фиг.21, область магистральной соединительной линии, соответствующая входной секции, обеспечена таким образом, что она является смежной с областью сдвигового регистра, и секции, соответствующие выходным секциям, и обозначенные номером 90, также обеспечены таким образом, что они являются смежными с областью сдвигового регистра. Такое размещение является традиционным, и магистральные соединительные линии для различных сигналов сформированы вместе в описанной выше области магистральной соединительной линии. В конфигурации, показанной на Фиг.21, при рассмотрении конкретного размещения каждой соединительной линии магистральные соединительные линии управляющего сигнала и магистральная соединительная линия VSS сформированы в области на противоположной стороне области отображения относительно области сдвигового регистра. При рассмотрении позиционного отношения между магистральными соединительными линиями управляющего сигнала и магистральной соединительной линией VSS область, в которой сформирована магистральная соединительная линия VSS, находится ближе к краю панели, чем область, в которой сформированы магистральные соединительные линии управляющих сигналов. Кроме того, в примере, показанном на Фиг.21, магистральная соединительная линия VSS и ответвленные соединительные линии сформированы в одном и том же слое и магистральные соединительные линии управляющего сигнала и ответвленные соединительные линии сформированы в разных слоях. Таким образом, магистральная соединительная линия управляющего сигнала и ответвленная соединительная линия соединены друг с другом через контакт.

Следует отметить, что в связи с изобретением, относящимся к этому вопросу, известны следующие документы предшествующего уровня техники. Опубликованная заявка на патент Японии № 2006-79041, опубликованная заявка на патент Японии № 2007-316642 и опубликованный японский перевод заявки PCT № 2005-527856 раскрывают примеры схемы расположения компонентов двух каскадов сдвигового регистра в драйвере затвора. В частности, Фиг.2 опубликованной заявки на патент Японии № 2006-79041 и Фиг.6 опубликованного японского перевода заявки PCT № 2005-527856 раскрывают примеры схемы расположения компонентов, в которых магистральные соединительные линии выполнены таким образом, что они становятся более узкими, когда они приближаются к области сдвигового регистра от края панели.

ДОКУМЕНТЫ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЕ ДОКУМЕНТЫ

[Патентный документ 1] Опубликованная заявка на патент Японии № 2006-79041

[Патентный документ 2] Опубликованная заявка на патент Японии № 2007-316642

[Патентный документ 3] Опубликованный японский перевод заявки PCT № 2005-527856

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ПРОБЛЕМЫ, КОТОРЫЕ ДОЛЖНЫ БЫТЬ РЕШЕНЫ ПОСРЕДСТВОМ ИЗОБРЕТЕНИЯ

Однако в соответствии с традиционной конфигурацией между ответвленной соединительной линией для подачи потенциала электропитания постоянного тока VSS на бистабильную схему от магистральной соединительной линии VSS и магистральными соединительными линиями управляющих сигналов имеется участок наложения как секция, обозначенная номером 91 на Фиг.21. Поскольку участок наложения становится емкостью нагрузки, могут возникнуть показанные ниже явления. Во-первых, хотя потенциал VSS, который является постоянным потенциалом, должен быть существенно подан на бистабильную схему от магистральной соединительной линии VSS, потенциал VSS изменяется вследствие изменений форм тактовых сигналов. Кроме того, вследствие емкости нагрузки участка наложения происходит искажение формы тактовых сигналов и т.д., которое передается через магистральные соединительные линии управляющего сигнала. В соответствии с традиционной конфигурацией могут произойти описанные выше явления, и, таким образом, имеется проблема ухудшения качества отображения. Кроме того, когда обеспечены те же самые магистральные соединительные линии управляющего сигнала, которые показаны в конфигурации Фиг.21, если магистральная соединительная линия VSS расположена между магистральной соединительной линией для сигнала очистки CLR и областью сдвигового регистра, то между ответвленной соединительной линией управляющего сигнала и магистральной соединительной линией VSS имеется участок наложения. Таким образом, потенциал VSS изменяется вследствие изменений форм тактовых сигналов. Поэтому в конфигурации, показанной на Фиг.21, имеется проблема ухудшения качества отображения. Кроме того, традиционно имеется высокий спрос на сокращение расхода энергии питания и миниатюризацию устройства отображения.

Задача настоящего изобретения состоит в том, чтобы достигнуть миниатюризации при уменьшении расхода энергии питания без ухудшения качества отображения в устройстве отображения, включающем в себя драйвер затвора.

СРЕДСТВО ДЛЯ РЕШЕНИЯ ПРОБЛЕМ

Первый аспект настоящего изобретения направлен на

устройство отображения, содержащее:

подложку;

схему пикселей, сформированную в области отображения, для отображения изображения, область отображения является частью всей области на подложке;

множество линий сигналов сканирования, сформированных в области отображения и образующих часть схемы пикселей;

сдвиговый регистр, который сформирован в части всей области на подложке, кроме области отображения, и который включает в себя множество бистабильных схем, имеющих первое состояние и второе состояние, и который последовательно управляет множеством линий сигналов сканирования посредством множества бистабильных схем, последовательно помещаемых в первое состояние на основе множества тактовых сигналов, множество бистабильных схем последовательно соединены друг с другом и обеспечены таким образом, что они имеют взаимно однозначное соответствие с множеством линий сигналов сканирования;

магистральные соединительные линии управляющих сигналов, сформированные в области на противоположной стороне области отображения относительно области сдвигового регистра, и передающие управляющие сигналы сдвигового регистра, включающие в себя множество тактовых сигналов, область сдвигового регистра является областью, в которой сформирован сдвиговый регистр, и управляющие сигналы сдвигового регистра являются сигналами для управления работой множества бистабильных схем;

ответвленные соединительные линии управляющих сигналов, которые соединяют магистральные соединительные линии управляющих сигналов с каждой бистабильной схемой;

магистральную соединительную линию потенциала электропитания постоянного тока, которая передает потенциал электропитания постоянного тока, который должен быть подан на множество бистабильных схем; и

ответвленная соединительная линия потенциала электропитания постоянного тока, которая соединяет магистральную соединительную линию потенциала электропитания постоянного тока с каждой бистабильной схемой, причем

магистральная соединительная линия потенциала электропитания постоянного тока сформирована в области между областью сдвигового регистра и областью отображения.

В соответствии со вторым аспектом настоящего изобретения в первом аспекте настоящего изобретения

подложка имеет многоуровневую структуру, включающую в себя первую металлическую пленку и вторую металлическую пленку, причем первая металлическая пленка формирует схемы соединительных линий, включающие в себя электроды истока тонкопленочных транзисторов, обеспеченных во множестве бистабильных схем, и вторая металлическая пленка формирует схемы соединительных линий, включающие в себя электроды затвора тонкопленочных транзисторов, и

магистральная соединительная линия потенциала электропитания постоянного тока и ответвленная соединительная линия потенциала электропитания постоянного тока сформированы из одной и той же металлической пленки, одна и та же металлическая пленка является либо первой металлической пленкой, либо второй металлической пленкой.

В соответствии с третьим аспектом настоящего изобретения во втором аспекте настоящего изобретения

магистральная соединительная линия потенциала электропитания постоянного тока включает в себя первую магистральную соединительную линию потенциала электропитания постоянного тока, которая передает низкоуровневый потенциал электропитания постоянного тока, который должен быть подан на множество бистабильных схем.

В соответствии с четвертым аспектом настоящего изобретения в третьем аспекте настоящего изобретения

первая магистральная соединительная линия потенциала электропитания постоянного тока сформирована из первой металлической пленки.

В соответствии с пятым аспектом настоящего изобретения в третьем аспекте настоящего изобретения

магистральная соединительная линия потенциала электропитания постоянного тока дополнительно включает в себя вторую магистральную соединительную линию потенциала электропитания постоянного тока, которая передает высокоуровневый потенциал электропитания постоянного тока, который должен быть подан на множество бистабильных схем.

В соответствии с шестым аспектом настоящего изобретения в пятом аспекте настоящего изобретения

ответвленная соединительная линия потенциала электропитания постоянного тока дополнительно включает в себя: первую ответвленную соединительную линию потенциала электропитания постоянного тока, которая соединяет первую магистральную соединительную линию потенциала электропитания постоянного тока с каждой бистабильной схемой; и вторая ответвленная соединительная линия потенциала электропитания постоянного тока, которая соединяет вторую магистральную соединительную линию потенциала электропитания постоянного тока с каждой бистабильной схемой,

первая магистральная соединительная линия потенциала электропитания постоянного тока и первая ответвленная соединительная линия потенциала электропитания постоянного тока сформированы из одной и той же металлической пленки, которая является либо первой металлической пленкой, либо второй металлической пленкой,

вторая магистральная соединительная линия потенциала электропитания постоянного тока и вторая ответвленная соединительная линия потенциала электропитания постоянного тока сформированы из одной и той же металлической пленки, которая является либо первой металлической пленкой, либо второй металлической пленкой, и

первая магистральная соединительная линия потенциала электропитания постоянного тока и вторая магистральная соединительная линия потенциала электропитания постоянного тока сформированы из разных металлических пленок.

В соответствии с седьмым аспектом настоящего изобретения во втором аспекте настоящего изобретения

магистральные соединительные линии управляющего сигнала сформированы из первой металлической пленки.

В соответствии с восьмым аспектом настоящего изобретения в первом аспекте настоящего изобретения

соединительные линии, которые формируют магистральную соединительную линию потенциала электропитания постоянного тока и магистральные соединительные линии управляющего сигнала все равны друг другу по ширине соединительной линии.

В соответствии с девятым аспектом настоящего изобретения в первом аспекте настоящего изобретения

магистральная соединительная линия для передачи сигнала, который является одним из управляющих сигналов сдвигового регистра, кроме множества тактовых сигналов, и формирует пять или менее импульсов в течение одного периода кадра, сформирована в области между областью сдвигового регистра и областью отображения.

ЭФФЕКТЫ ИЗОБРЕТЕНИЯ

В соответствии с первым аспектом настоящего изобретения магистральная соединительная линия потенциала электропитания постоянного тока сформирована в области между областью сдвигового регистра и областью отображения и магистральные соединительные линии управляющих сигналов сформированы в области на противоположной стороне области отображения относительно области сдвигового регистра. Таким образом, в отличие от традиционной конфигурации нет участка наложения между ответвленной соединительной линией потенциала электропитания постоянного тока для подачи потенциала электропитания постоянного тока на бистабильные схемы от магистральной соединительной линии потенциала электропитания постоянного тока и магистральных соединительных линий управляющего сигнала. Поэтому не возникает емкость нагрузки, получающаяся в результате такого участка наложения, что подавляет изменение потенциала электропитания постоянного тока в результате изменения в формах управляющих сигналов, таких как тактовые сигналы. Посредством этого магистральная соединительная линия потенциала электропитания постоянного тока может быть сделана более узкой, чем в традиционной конфигурации. Кроме того, поскольку не возникает емкость нагрузки, получающаяся в результате участка наложения между ответвленной соединительной линией потенциала электропитания постоянного тока и магистральными соединительными линиями управляющего сигнала, подавляется возникновение искажения формы управляющих сигналов, таких как тактовые сигналы, которые передаются через магистральные соединительные линии управляющих сигналов. Посредством этого магистральные соединительные линии управляющих сигналов могут быть сделаны более узкими, чем в традиционной конфигурации. Кроме того, поскольку емкость нагрузки уменьшена по сравнению с традиционной конфигурацией, может быть достигнуто сокращение расхода энергии питания. Кроме того, поскольку, как описано выше, магистральная соединительная линия потенциала электропитания постоянного тока и магистральная соединительная линия управляющего сигнала могут быть сделаны более узкими, чем в традиционной конфигурации, рамка панели может быть сужена.

В соответствии со вторым аспектом настоящего изобретения, поскольку нет необходимости контакта для соединения магистральной соединительной линии потенциала электропитания постоянного тока с ответвленной соединительной линией потенциала электропитания постоянного тока, подавляется увеличение сопротивления в результате того, что соединительная линия становится узкой на участке контакта.

В соответствии с третьим аспектом настоящего изобретения в устройстве отображения, включающем в себя сдвиговый регистр, на который подается низкоуровневый потенциал электропитания постоянного тока, могут быть получены те же самые полезные эффекты, которые получены в первом аспекте настоящего изобретения, и те же самые полезные эффекты, которые получены во втором аспекте настоящего изобретения.

В соответствии с четвертым аспектом настоящего изобретения магистральная соединительная линия, которая передает низкоуровневый потенциал электропитания постоянного тока, сформирована из той же самой металлической пленки, как и электроды истока тонкопленочных транзисторов в бистабильных схемах, составляющих сдвиговый регистр. При этом в общем случае в бистабильной схеме низкоуровневый потенциал электропитания постоянного тока подается на электроды истока тонкопленочных транзисторов. Вследствие упомянутого выше низкоуровневый потенциал электропитания постоянного тока может быть подан на электроды истока тонкопленочных транзисторов в бистабильной схеме без обеспечения контакта в области сдвигового регистра.

В соответствии с пятым аспектом настоящего изобретения в устройстве отображения, включающем в себя сдвиговый регистр, на который подается низкоуровневый потенциал электропитания постоянного тока и высокоуровневый потенциал электропитания постоянного тока, могут быть получены те же самые полезные эффекты, которые получены в первом аспекте настоящего изобретения, и те же самые полезные эффекты, которые получены во втором аспекте настоящего изобретения.

В соответствии с шестым аспектом настоящего изобретения в устройстве отображения, включающем в себя сдвиговый регистр, на который подается низкоуровневый потенциал электропитания постоянного тока и высокоуровневый потенциал электропитания постоянного тока, поскольку нет необходимости контакта для соединения магистральной соединительной линии с ответвленной соединительной линией для низкоуровневой соединительной линии потенциала электропитания постоянного тока и высокоуровневой соединительной линии потенциала электропитания постоянного тока, подавляется увеличение сопротивления в результате того, что соединительная линия становится узкой на участке контакта.

В соответствии с седьмым аспектом настоящего изобретения управляющие сигналы, такие как тактовые сигналы, могут быть поданы на тонкопленочные транзисторы в бистабильной схеме без обеспечения контакта в области сдвигового регистра.

В соответствии с восьмым аспектом настоящего изобретения в конфигурации, в которой ширина магистральной соединительной линии потенциала электропитания постоянного тока сделана равной ширине магистральных соединительных линий управляющего сигнала, могут быть получены те же самые полезные эффекты, которые получены в первом аспекте настоящего изобретения.

В соответствии с девятым аспектом настоящего изобретения в конфигурации, в которой в области между областью сдвигового регистра и областью отображения сформирована не только магистральная соединительная линия потенциала электропитания постоянного тока, но также магистральная соединительная линия, которая передает редкий сигнал, могут быть получены те же самые полезные эффекты, которые получены в первом аспекте настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - схема расположения компонентов драйвера затвора и области вблизи него в жидкокристаллическом устройстве отображения с активной матрицей в соответствии с первым вариантом осуществления настоящего изобретения.

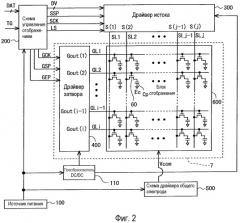

Фиг.2 - блок-схема, показывающая общую конфигурацию жидкокристаллического устройства отображения в первом варианте осуществления.

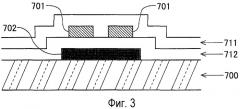

Фиг.3 - частичный поперечный разрез матричной подложки в первом варианте осуществления.

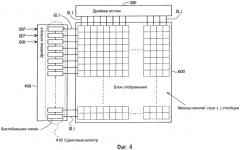

Фиг.4 - блок-схема для описания конфигурации драйвера затвора в первом варианте осуществления.

Фиг.5 - блок-схема, показывающая конфигурацию сдвигового регистра в драйвере затвора в первом варианте осуществления.

Фиг.6 - схема формы сигнала для описания работы драйвера затвора в первом варианте осуществления.

Фиг.7 - схема формы сигнала для описания работы драйвера затвора в первом варианте осуществления.

Фиг.8 - схема, показывающая иллюстративную конфигурацию одного каскада (бистабильной схемы) сдвигового регистра в первом варианте осуществления.

Фиг.9 - схема формы сигнала для описания работы сдвигового регистра в первом варианте осуществления.

Фиг.10 - схема расположения компонентов драйвера затвора и области вблизи него в модификации первого варианта осуществления.

Фиг.11 - блок-схема, показывающая конфигурацию сдвигового регистра в драйвере затвора в модификации первого варианта осуществления.

Фиг.12 - схема, показывающая иллюстративную конфигурацию одного каскада (бистабильной схемы) сдвигового регистра в жидкокристаллическом устройстве отображения с активной матрицей в соответствии со вторым вариантом осуществления настоящего изобретения.

Фиг.13 - схема расположения компонентов драйвера затвора и области вблизи него во втором варианте осуществления.

Фиг.14 - схема расположения компонентов драйвера затвора и области вблизи него в первой модификации второго варианта осуществления.

Фиг.15 - схема расположения компонентов драйвера затвора и области вблизи него во второй модификации второго варианта осуществления.

Фиг.16 - схема расположения компонентов драйвера затвора и области вблизи него в третьей модификации второго варианта осуществления.

Фиг.17 - схема расположения компонентов драйвера затвора и области вблизи него в четвертой модификации второго варианта осуществления.

Фиг.18 - схема расположения компонентов драйвера затвора и области вблизи него в жидкокристаллическом устройстве отображения с активной матрицей в соответствии с третьим вариантом осуществления настоящего изобретения.

Фиг.19 - схема расположения компонентов драйвера затвора и области вблизи него в первой модификации третьего варианта осуществления.

Фиг.20 - схема расположения компонентов драйвера затвора и области вблизи него во второй модификации третьего варианта осуществления.

Фиг.21 - схема, показывающая иллюстративную схему расположения компонентов драйвера затвора в традиционном жидкокристаллическом устройстве отображения, использующем монолитную панель драйвера затвора.

ВАРИАНТЫ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Варианты осуществления настоящего изобретения будут описаны ниже со ссылкой на сопроводительные чертежи.

<1. Первый вариант осуществления>

<1.1 Общая конфигурации и обзор работы>

Фиг.2 является блок-схемой, показывающей общую конфигурацию жидкокристаллического устройства отображения с активной матрицей в соответствии с первым вариантом осуществления настоящего изобретения. Как показано на Фиг.2, жидкокристаллическое устройство отображения включает в себя источник 100 питания, преобразователь 110 DC/DC, схему 200 управления отображением, драйвер 300 истока (схему драйвера линии видеосигнала), драйвер 400 затвора (схему драйвера линии сигнала сканирования), схему 500 драйвера общего электрода и блок 600 отображения. Следует отметить, что в настоящем варианте осуществления драйвер 400 затвора и блок 600 отображения сформированы на одной подложке 7 (матричной подложке, которая является одной из двух подложек, составляющих жидкокристаллическую панель). А именно, драйвер 400 затвора в настоящем варианте осуществления является "монолитным драйвером затвора".

В блоке 600 отображения сформирована схема пикселей, включающая в себя множество (j) линий SL1-SLj шин истока (линий видеосигнала); множество (i) линий GL1-GLi шин затвора (линий сигнала сканирования); и множество (ixj) секций формирования пикселей, обеспеченных на соответствующих пересечениях линий SL1-SLj шин истока и линий GL1-GLi шин затвора.

Множество секций формирования пикселей размещены в матрице и тем самым формируют матрицу пикселей. Каждая секция формирования пикселя составлена из тонкопленочного транзистора (TFT) 60, который представляет собой переключающийся элемент, соединенный своим выводом затвора с линией шины затвора, проходящей через соответствующее пересечение, и соединенный своим выводом истока с линией шины истока, проходящей через пересечение; электрод пикселя, соединенный с выводом стока тонкопленочного транзистора 60; общего электрода Ec, который представляет собой интегрирующий электрод, обеспеченный таким образом, что он совместно используется множеством секций формирования пикселей; и жидкокристаллического слоя, который обеспечен таким образом, что он совместно используется множеством секций формирования пикселей, и который размещен между электродом пикселя и общим электродом Ec. Посредством жидкокристаллической емкости, сформированной электродом пикселя и общим электродом Ec, формируется емкость Cp пикселя. Следует заметить, что, хотя обычно параллельно с жидкокристаллической емкостью обеспечивается вспомогательная емкость, чтобы надежно удерживать напряжение в емкости Cp пикселя, вспомогательная емкость непосредственно не относится к настоящему изобретению, и, таким образом, ее описание и изображение опущены.

Источник 100 питания подает предопределенное напряжение электропитания на преобразователь 110 DC/DC, схему 200 управления отображением и схему 500 драйвера общего электрода. Преобразователь 100 DC/DC из напряжения электропитания формирует предопределенные напряжения постоянного тока, чтобы дать возможность работать драйверу 300 истока и драйверу 400 затвора, и подает предопределенные напряжения постоянного тока на драйвер 300 истока и драйвер 400 затвора. Схема 500 драйвера общего электрода подает предопределенный потенциал Vcom на общий электрод Ec.

Схема 200 управления отображением принимает сигнал изображения DAT и группу сигналов синхронизации TG, такую как сигнал горизонтальной синхронизации и сигнал вертикальной синхронизации, которые отправляются от внешнего источника и выдают цифровой видеосигнал DV и сигнал начального импульса истока SSP, тактовый сигнал истока SCK, запирающий сигнал LS, сигнал начального импульса затвора GSP, сигнал конечного импульса затвора GEP и тактовый сигнал затвора GCK, которые являются сигналами для управления отображением изображения на блоке 600 отображения. Следует заметить, что в настоящем варианте осуществления тактовый сигнал затвора GCK выполнен посредством 4-фазовых тактовых сигналов CK1 (в дальнейшем называется "первым тактовым сигналом затвора"), CK1B (в дальнейшем называется "вторым тактовым сигналом затвора"), CK2 (в дальнейшем называется "третьим тактовым сигналом затвора") и CK2B (в дальнейшем называется "четвертым тактовым сигналом затвора").

Драйвер 300 истока принимает цифровой видеосигнал DV, сигнал начального импульса истока SSP, тактовый сигнал истока SCK и запирающий сигнал LS, которые выдаются из схемы 200 управления изображением, и подает управляющие видеосигналы S(1)-S(j) на линию SL1-SLj шины истока соответственно.

Драйвер 400 затвора повторяет подачу сигналов активного сканирования Gout(1)-Gout(i) на соответствующие линии GL1-GLi шин затвора в циклах одного периода вертикального сканирования на основе сигнала начального импульса затвора GSP, сигнала конечного импульса затвора GEP и тактового сигнала затвора GCK, которые выдаются из схемы 200 управления отображением. Следует заметить, что подробное описание драйвера 400 затвора будет сделано позже.

Описанным выше образом управляющие видеосигналы S(1)-S(j) подаются на линии SL1-SLj шин истока соответственно и сканирующие сигналы Gout(1)-Gout(i) подаются на линии GL1-GLi шин затвора соответственно, посредством чего на блоке 600 отображения отображается изображение, основанное на сигнале изображения DAT, который отправлен из внешнего источника.

<1.2 Структура матричной подложки>

Фиг.3 является частичным поперечным сечением матричной подложки 7. Матричная подложка 7 имеет многослойную структуру, с тем чтобы могли быть сформированы драйвер 400 затвора, схема пикселей и т.д., и многослойная структура включает в себя две металлические пленки (металлических слоя). В частности, как показано на Фиг.3, металлическая пленка 702, защитная пленка 712, металлическая пленка 701 и защитная пленка 711 сложены поверх друг друга на стеклянной подложке 700. Металлическая пленка 701 используется для формирования электродов истока (и электродов стока) тонкопленочных транзисторов, которые обеспечены в драйвере 400 затвора и в схеме пикселей. Таким образом, такая металлическая пленка 701 в дальнейшем называется "металлической пленкой 701 истока". Металлическая пленка 702 используется для формирования электродов затвора тонкопленочных транзисторов. Таким образом, такая металлическая пленка 702 в дальнейшем называется "металлической пленкой 702 затвора". Следует отметить, что металлическая пленка 701 истока и металлическая пленка 702 затвора используются не только в качестве электродов тонкопленочных транзисторов, но также используются в качестве схем соединительных линий, сформированных в драйвере 400 затвора или в схеме пикселей. Кроме того, в настоящем варианте осуществления первая металлическая пленка реализована посредством металлической пленки 701 истока и вторая металлическая пленка реализована посредством металлической пленки 702 затвора.

<1.3 Драйвер затвора>

<1.3.1 Конфигурации и работа драйвера затвора>

Далее будет описана конфигурация драйвера 400 затвора в настоящем варианте осуществления. Как показано на Фиг.4, драйвер 400 затвора составлен из сдвигового регистра 410, сформированного множеством каскадов. Матрица пикселей с i строками и j столбцами сформирована в блоке 600 отображения, и каскады сдвигового регистра 410 обеспечены таким образом, что они имеют взаимно однозначное соответствие со строками матрицы пикселей. Кроме того, каждый каскад сдвигового регистра 410 представляет собой бистабильную схему, которая находится в любом из двух состояний (первое состояние и второе состояние) в каждый момент времени, и выдает сигнал, указывающий состояние (в дальнейшем называется "сигналом состояния"). Таким образом, сдвиговый регистр 410 выполнен посредством i бистабильных схем. Следует отметить, что схема размещения компонентов драйвера 400 затвора будет описана позже.

Фиг.5 является блок-схемой, показывающей конфигурацию сдвигового регистра 410 в драйвере 400 затвора. Как описано выше, сдвиговый регистр 410 выполнен посредством i бистабильных схем. Каждая бистабильная схема снабжена входными выводами для приема 4-фазовых тактовых сигналов CKA (в дальнейшем называется "первым тактовым импульсом "), CKB (в дальнейшем называется "вторым тактовым импульсом "), CKC (в дальнейшем называется "третьим тактовым импульсом") и CKD (в дальнейшем называется "четвертым тактовый импульсом"); входным выводом для приема сигнала установки S; входным выводом для приема сигнала сброса R; входным выводом для приема сигнала очистки CLR; входным выводом для приема низкоуровневого потенциала электропитания постоянного тока VSS; и выходным выводом для вывода сигнала состояния Q.

Сигналы, которые должны быть поданы на входные выводы каждого каскада (каждой бистабильной схемы) сдвигового регистра 410, являются следующими. Для первой стадии первый тактовый сигнал затвора CK1 подается как первый тактовый импульс CKA, второй тактовый сигнал затвора CK1B подается как второй тактовый импульс CKB, четвертый тактовый сигнал затвора CK2B подается как третий тактовый импульс CKC, и третий тактовый сигнал затвора CK2 подается как четвертый тактовый импульс CKD. Для второго каскада второй тактовый сигнал затвора CK1B подается как первый тактовый импульс CKA, первый тактовый сигнал затвора CK1 подается как второй тактовый импульс CKB, третий тактовый сигнал затвора CK2 подается как третий тактовый импульс CKC, и четвертый тактовый сигнал затвора CK2B подается как четвертый тактовый импульс CKD. Для третьего и последующих каскадов та конфигурация, которая имеется для описанных выше первого и второго каскадов, повторяется каждые два каскада. Кроме того, для первой стадии сигнал начального импульса затвора GSP подается как сигнал установки S. Для второго и последующих каскадов сигнал состояния Q, выданный из предыдущего каскада, подается как сигнал установки S. Кроме того, сигнал конечного импульса затвора GEP подается на i-й каскад как сигнал сброса R. Для каскадов с первого по (i-1)-й сигнал состояния Q, выданный из последующего каскада, подается как сигнал сброса R. Следует отметить, что низкоуровневый потенциал электропитания постоянного тока VSS и сигнал очистки CLR подается на все каскады одинаковым образом.

Далее со ссылкой на Фиг.5-7 будет описана работа драйвера 400 затвора в настоящем варианте осуществления. На сдвиговый регистр 410 подаются 4-фазовые тактовые сигналы (первый тактовый сигнал затвора CK1, второй тактовый сигнал затвора CK1B, третий тактовый сигнал затвора CK2 и четвертый тактовый сигнал затвора CK2B), сигнал начального импульса затвора GSP, сигнал конечного импульса затвора GEP, низкоуровневый потенциал электропитания постоянного тока VSS и сигнал очистки CLR.

Как показано на Фиг.6, первый тактовый сигнал затвора CK1 и второй тактовый сигнал затвора CK1B смещены по фазе на 180 градусов (период, соответствующий одному периоду горизонтального сканирования), и третий тактовый сигнал затвора CK2 и четвертый тактовый сигнал затвора CK2B смещены по фазе на 180 градусов. Третий тактовый сигнал затвора CK2 имеет задержку по фазе на 90 градусов от первого тактового сигнала затвора CK1. Все тактовые сигналы затвора CK1, CKB1, CK2 и CK2B помещаются в состояние высокого уровня (уровень H) в интервалах одного периода горизонтального сканирования.

Когда сигнал начального импульса затвора GSP, служащий в качестве сигнала установки S, подается на первый каскад сдвигового регистра 410, импульс, включенный в сигнал начального импульса затвора GSP (этот импульс включен в сигнал состояния Q, выданный из каждого каскада), последовательно передается с первого по i-й каскад на основе тактовых сигналов затвора CK1, CKB1, CK2 и CK2B. Затем согласно передаче импульса сигналы состояния Q, выданные из соответствующих каскадов сдвигового регистра 410, последовательно переходят на высокий уровень. Затем сигналы состояния Q, выданные из соответствующих каскадов, подаются на линии GL1-GLi шин затвора соотв