Комплементарный входной каскад быстродействующего операционного усилителя

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи. Техническим результатом является расширение диапазона активной работы входного каскада ОУ для дифференциального сигнала, а также получение граничных напряжений его проходной характеристики iвых=f(uвх) на уровне Uгр=1÷2 В, что приводит к повышению быстродействия ОУ более чем на порядок. Комплементарный входной каскад быстродействующего операционного усилителя содержит: первый (1) и второй (2) входные транзисторы, первый (3) и второй (4) выходные транзисторы с объединенными базами, первый (5) и второй (6) входы устройства, первый (7) и второй (8) вспомогательные транзисторы, первый (9) токостабилизирующий двухполюсник, первые (10), (11) токовые выходы устройства, вторые (12), (13) токовые выходы устройства, первую (14) шину источника питания, вторую (15) шину источника питания, второй (16) токостабилизирующий двухполюсник, первый (17) дополнительный резистор, второй (18) дополнительный резистор, третий (19) и четвертый (20) дополнительные резисторы. 20 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях, ОУ).

Известны схемы комплементарных входных каскадов ОУ, выполненных в виде дифференциальных усилителей (ДУ) на n-p-п и р-п-р транзисторах с так называемой «архитектурой входного каскада операционного усилителя цА741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом [29-31], стали основным усилительным элементом многих аналоговых интерфейсов. Это связано с тем, что в таких ДУ минимизируется входная емкость из-за отсутствия эффекта Миллера. Предлагаемое изобретение относится к данному подклассу устройств.

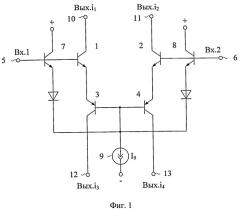

Ближайшим прототипом (фиг.1) заявляемого устройства является комплементарный входной каскад быстродействующего операционного усилителя по патенту US 4.901.031, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов с объединенными базами, а базы подключены к соответствующим первому 5 и второму 6 входам устройства, первый 7 и второй 8 вспомогательные транзисторы, первый 9 токостабилизирующий двухполюсник, первые 10, 11 токовые выходы устройства, связанные с коллекторами первого 1 и второго 2 входных транзисторов, вторые 12, 13 токовые выходы устройства, связанные с коллекторами первого 3 и второго 4 выходных транзисторов, причем коллекторы первого 7 и второго 8 вспомогательных транзисторов связаны с первой 14 шиной источника питания, а первый 9 токостабилизирующий двухполюсник связан со второй 15 шиной источника питания.

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно узкий динамический диапазон (Uгр) линейного усиления дифференциальных сигналов (Uвx.max<Uгр≈100÷150 мВ). Как показано в монографии авторов настоящей заявки [31], это обстоятельство является главной причиной невысокого быстродействия современных операционных усилителей, обусловленной нелинейным режимом работы входного каскада ОУ. При этом для большинства ОУ с высокоимпедансным узлом и одним корректирующим конденсатором (Ск) максимальная скорость нарастания выходного напряжения определяется формулой [31]

υ в ы х = 2 π f с р U г р , ( 1 )

где fcp - частота единичного усиления (частота среза) скорректированного ОУ;

Uгр - напряжение ограничения проходной характеристики iвыx=f(uвх) входного каскада (для классических ДУ Uгр=50÷100 мВ).

Из (1) следует, что повышение υвых можно осуществить двумя качественно разными путями [31]:

1. Увеличением диапазона активной работы входного ДУ (Uгр) без изменения крутизны преобразования входного напряжения в выходные токи ДУ;

2. Повышением fcp за счет улучшения частотных свойств транзисторов, что связано, прежде всего, с использованием более высокочастотных и дорогостоящих техпроцессов (SG25VD, SG25H1, SG25RH и др.).

Заявляемый входной каскад ОУ решает задачу повышения быстродействия за счет увеличения (без изменения крутизны) более чем на порядок диапазона линейной работы входного каскада, измеряемого напряжением ограничения Uгр=1÷2 В.

Таким образом, основная задача предлагаемого изобретения состоит в расширении диапазона активной работы входного каскада ОУ для дифференциального сигнала - получении граничных напряжений его проходной характеристики iвых=f(uвх) на уровне Uгр=1÷2 В.

Поставленная задача достигается тем, что в комплементарном входном каскаде операционного усилителя, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов с объединенными базами, а базы подключены к соответствующим первому 5 и второму 6 входам устройства, первый 7 и второй 8 вспомогательные транзисторы, первый 9 токостабилизирующий двухполюсник, первые 10, 11 токовые выходы устройства, связанные с коллекторами первого 1 и второго 2 входных транзисторов, вторые 12, 13 токовые выходы устройства, связанные с коллекторами первого 3 и второго 4 выходных транзисторов, причем коллекторы первого 7 и второго 8 вспомогательных транзисторов связаны с первой 14 шиной источника питания, а первый 9 токостабилизирующий двухполюсник связан со второй 15 шиной источника питания, предусмотрены новые элементы и связи - между эмиттером второго 8 вспомогательного транзистора и второй 15 шиной источника питания включен первый 9 токостабилизирующий двухполюсник, между эмиттером первого 7 вспомогательного транзистора и второй 15 шиной источника питания включен второй 16 токостабилизирующий двухполюсник, база первого 7 вспомогательного транзистора соединена с эмиттером первого 1 входного транзистора, база второго 8 вспомогательного транзистора соединена с эмиттером второго 2 входного транзистора, эмиттер первого 1 входного транзистора связан с эмиттером первого 3 выходного транзистора через первый 17 дополнительный резистор, эмиттер второго 2 входного транзистора связан с эмиттером второго 4 выходного транзистора через второй 18 дополнительный резистор, а между эмиттерами первого 7 и второго 8 вспомогательных транзисторов включены два последовательно соединенных третий 19 и четвертый 20 дополнительные резисторы, общий узел которых подключен к объединенным базам первого 3 и второго 4 выходных транзисторов.

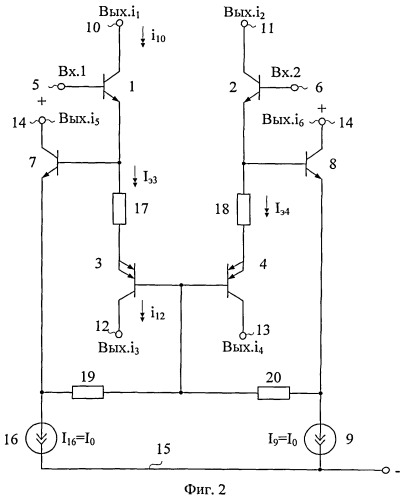

Схема усилителя-прототипа представлена на чертеже фиг.1. На чертеже фиг.2 показано заявляемое устройство в соответствии с формулой изобретения.

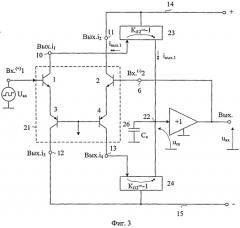

На чертеже фиг.3 приведена возможная архитектура быстродействующего операционного усилителя с предлагаемым входным каскадом.

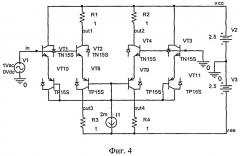

На чертеже фиг.4 показана схема ДУ-прототипа фиг.1 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.5 приведена зависимость разности выходных токов (I(out1)-I(out2)) и (I(out3)-I(out4)) ДУ-прототипа фиг.4 от входного напряжения uвх.

На чертеже фиг.6 представлена зависимость абсолютных значений выходных токов I(out1) и I(out2) ДУ-прототипа фиг.4 от входного напряжения uвх. Аналогичная зависимость выходных токов I(out3) и I(out4) ДУ-прототипа фиг.4 от входного напряжения uвх представлена на чертеже фиг.7. Из данных графиков следует, что максимальное значение выходных токов ДУ-прототипа не превышает величины I1=2 МA, что характерно для каскадов класса «А».

На чертеже фиг.8 показана схема заявляемого ДУ фиг.2 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на чертежах фиг.9-фиг.12 зависимости разностей выходных токов (I(out1)-I(out2)) и (I(out3)-I(out4)) от входного напряжения Uвх ДУ фиг.8 при различных значениях сопротивлений дополнительных резисторов 19, 20 (Rvar).

На чертеже фиг.13 представлена зависимость абсолютных значений выходных токов I(out1) и I(out2) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 19, 20 Rvar=200 Ом, а на чертеже фиг.14 - зависимость выходных токов I(out3) и I(out4) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 19, 20 Rvar=200 Ом.

На чертеже фиг.15 показана зависимость абсолютных значений выходных токов I(out1) и I(out2) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 19, 20 Rvar=1 кОм, а на чертеже фиг.16 аналогичная зависимость выходных токов I(out1) и I(out2) заявляемого ДУ фиг.8 от входного напряжения uвх при сопротивлениях дополнительных резисторов 19, 20 Rvar=1 кОм в увеличенном масштабе.

На чертеже фиг.17 представлена зависимость абсолютных значений выходных токов I(out1) и I(out2) заявляемого ДУ от входного напряжения uвх при Rvar=1 кОм, а на чертеже фиг.18 эта же зависимость выходных токов I(out1) и I(out2) заявляемого ДУ от входного напряжения uвх при Rvar=1 кОм в увеличенном масштабе.

Графики фиг.19 и фиг.20 характеризуют зависимость от uвх абсолютных значений выходных токов I(out3) и I(out4) при Rvar=1 кОм в мелком (фиг.19) и укрупненном (фиг.20) масштабах.

Комплементарный входной каскад (ДУ) быстродействующего операционного усилителя фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов с объединенными базами, а базы подключены к соответствующим первому 5 и второму 6 входам устройства, первый 7 и второй 8 вспомогательные транзисторы, первый 9 токостабилизирующий двухполюсник, первые 10, 11 токовые выходы устройства, связанные с коллекторами первого 1 и второго 2 входных транзисторов, вторые 12, 13 токовые выходы устройства, связанные с коллекторами первого 3 и второго 4 выходных транзисторов, причем коллекторы первого 7 и второго 8 вспомогательных транзисторов связаны с первой 14 шиной источника питания, а первый 9 токостабилизирующий двухполюсник связан со второй 15 шиной источника питания. Между эмиттером второго 8 вспомогательного транзистора и второй 15 шиной источника питания включен первый 9 токостабилизирующий двухполюсник, между эмиттером первого 7 вспомогательного транзистора и второй 15 шиной источника питания включен второй 16 токостабилизирующий двухполюсник, база первого 7 вспомогательного транзистора соединена с эмиттером первого 1 входного транзистора, база второго 8 вспомогательного транзистора соединена с эмиттером второго 2 входного транзистора, эмиттер первого 1 входного транзистора связан с эмиттером первого 3 выходного транзистора через первый 17 дополнительный резистор, эмиттер второго 2 входного транзистора связан с эмиттером второго 4 выходного транзистора через второй 18 дополнительный резистор, а между эмиттерами первого 7 и второго 8 вспомогательных транзисторов включены два последовательно соединенных третий 19 и четвертый 20 дополнительные резисторы, общий узел которых подключен к объединенным базам первого 3 и второго 4 выходных транзисторов.

На чертеже фиг.3 заявляемый входной каскад фиг.2 (21) включен в классическую структуру быстродействующего ОУ с высокоимпедансным узлом 22, которая содержит дополнительные токовые зеркала 23, 24, выходной буфер 25 и корректирующий конденсатор (Ск) 26. При этом ОУ охвачен 100% отрицательной обратной связью.

Рассмотрим работу заявляемого устройства фиг.2.

В связи с тем что падение напряжения на резисторах 19, 20, создаваемое токами базы транзисторов 3 и 4, мало, статические токи всех транзисторов схемы определяются токами токостабилизирущих двухполюсников 16 и 9. При этом для достаточно низкоомных резисторов 17, 18 (R=10-15 Ом) за счет увеличения площадей эмиттерных переходов транзисторов 3, 4 можно при нулевом входном напряжении ДУ обеспечить равенство всех эмиттерных токов схемы:

I э 1 = I э 2 = I э 3 = I э 4 = ≈ I 0 , ( 1 )

где I0=I9=I16 - некоторый опорный ток, например 1 мА.

Если напряжение на первом 5 входе (Вх.1) ДУ становится больше напряжения на втором 6 входе ДУ, то коллекторные токи транзисторов 1 и 3 увеличиваются, а транзисторов 2 и 4 уменьшаются. При этом входное дифференциальное напряжение uвх «выделяется» на резисторах 19 и 20, что приводит к увеличению «открывающего» напряжения между базой транзистора 1 и базой транзистора 3:

u б 1 − 3 ≈ u в х 2 . ( 2 )

Таким образом коллекторные (выходные) токи транзисторов 1 и 3 будут пропорциональны входному напряжению uвх в широком диапазоне его изменения:

i 10 = i 12 ≈ u в х 2 ( r э 1 + r э 3 + R 0 + R 19 2 β 3 ) , ( 3 )

где rэ1, rэ3 - сопротивления эмиттерных переходов транзисторов 1 и 3;

R19=R20 - сопротивления резисторов 19 и 20;

β3 - коэффициент усиления по току базы транзистора 3;

R0≈R17=R18 - эквивалентное сопротивление, состоящее из объемного низкоомного эмиттерного резистора транзистора 3 (4) и дополнительного резистора 17 (R17=10÷15 Ом).

Учитывая, что при увеличении Iэ1 сопротивления rэ1 и rэ3 существенно уменьшаются, из (3) можно найти, что при больших uвх>>25 мВ

i 10 = i 12 ≈ u в х 2 ( R 0 + R 19 2 β 3 ) = u в х S , ( 4 )

где S = 1 2 ( R 0 + R 19 2 β 3 ) - крутизна ДУ.

Уравнение (4) справедливо для входных напряжений не более чем:

U в х . max ≤ U г р = I 0 R 19 = I 0 R 20 = 1 ÷ 2 B . ( 5 )

После этого под действием uвх происходит ограничение выходных токов ДУ.

Таким образом, диапазон активной работы ДУ фиг.2 определяется произведением I0R19 (5) и может выбираться в соответствии с требуемыми значениями к uвых операционного усилителя (1). Данные выводы подтверждаются графиками фиг.9-фиг.20, из которых следует, что диапазон активной работы заявляемого ДУ (Uгр) увеличивается на порядок в сравнении с Uгр ДУ-прототипа.

Таким образом, проходная характеристика iвых=f(uвх) заявляемого ДУ «продлевается» в область больших токов (фиг.9-фиг.20), значительно превышающих статические токи транзисторов ДУ и общий потребляемый ДУ ток в статическом режиме. Это характерно для транзисторных каскадов класса «АВ».

При отрицательном uвх ДУ фиг.2 работает аналогично.

Результаты компьютерного моделирования ДУ фиг.8, представленные на графиках фиг.9-фиг.20, подтверждают полученные выше теоретические выводы.

Таким образом, предлагаемый ДУ имеет более чем на порядок лучшее напряжение ограничения и может использоваться в структуре быстродействующих операционных усилителей различного функционального назначения, а также в аналоговых микросхемах с широким диапазоном линейной работы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.786.362

2. Патент США №4.030.044

3. Патент США №4.059.808, фиг.5

4. Патент США №4.286.227

5. Авт. свид. СССР №375754, H03f 3/38

6. Авт. свид. СССР №843164, H03f 3/30

7. Патент США №3.660.773

8. Патент США №4.560.948

9. Патент РФ №2930041, H03f 1/32

10. Патент Японии №57-5364, H03f 3/343

11. Патент ЧССР №134845, кл. 21а2 18/08

12. Патент ЧССР №134849, кл. 21а2 18/08

13. Патент ЧССР №135326, кл. 21а2 18/08

14. Патент США №4.389.579

15. Патент Англии №1543361, Н3Т

16. Патент США №5.521.552 (фиг.3а)

17. Патент США №4.059.808

18. Патент США №5.789.949

19. Патент США №4.453.134

20. Патент США №4.760.286

21. Авт. свид. СССР №1283946

22. Патент РФ №2019019

23. Патент США №4.389.579

24. Патент США №4.453.092

25. Патент США №3.566.289

26. Патент США №4.059.808 (фиг.2)

27. Патент США №3.649.926

28. Патент США №4.714.894 (фиг.1)

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис. 5.52.

31. Операционные усилители с непосредственной связью каскадов [Текст] / В.И.Анисимов, М.В.Капитонов, Н.Н.Прокопенко, Ю.М.Соколов. - Л., 1979. - 148 с.

Комплементарный входной каскад быстродействующего операционного усилителя, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны с эмиттерами соответствующих первого (3) и второго (4) выходных транзисторов с объединенными базами, а базы подключены к соответствующим первому (5) и второму (6) входам устройства, первый (7) и второй (8) вспомогательные транзисторы, первый (9) токостабилизирующий двухполюсник, первые (10), (11) токовые выходы устройства, связанные с коллекторами первого (1) и второго (2) входных транзисторов, вторые (12), (13) токовые выходы устройства, связанные с коллекторами первого (3) и второго (4) выходных транзисторов, причем коллекторы первого (7) и второго (8) вспомогательных транзисторов связаны с первой (14) шиной источника питания, а первый (9) токостабилизирующий двухполюсник связан со второй (15) шиной источника питания, отличающийся тем, что между эмиттером второго (8) вспомогательного транзистора и второй (15) шиной источника питания включен первый (9) токостабилизирующий двухполюсник, между эмиттером первого (7) вспомогательного транзистора и второй (15) шиной источника питания включен второй (16) токостабилизирующий двухполюсник, база первого (7) вспомогательного транзистора соединена с эмиттером первого (1) входного транзистора, база второго (8) вспомогательного транзистора соединена с эмиттером второго (2) входного транзистора, эмиттер первого (1) входного транзистора связан с эмиттером первого (3) выходного транзистора через первый (17) дополнительный резистор, эмиттер второго (2) входного транзистора связан с эмиттером второго (4) выходного транзистора через второй (18) дополнительный резистор, а между эмиттерами первого (7) и второго (8) вспомогательных транзисторов включены два последовательно соединенных третий (19) и четвертый (20) дополнительные резисторы, общий узел которых подключен к объединенным базам первого (3) и второго (4) выходных транзисторов.