Устройство для защиты интегральных микросхем от тиристорного эффекта

Иллюстрации

Показать всеИзобретение относится к электронике интегральных микросхем (ИС) и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования. Техническим результатом является повышение помехоустойчивости и надежности работы радиоэлектронной аппаратуры. Устройство содержит датчик тока, транзисторы, конденсаторы, резисторы, диоды, компаратор напряжения, RS-триггер, генератор импульсной последовательности. 1 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к электронике интегральных микросхем и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования для защиты от воздействия тяжелых заряженных частиц (ТЗЧ), высокоэнергитичных протонов (ВЭП), импульсного ионизирующего излучения, пучкового оружия.

Известно устройство защиты фирмы «MAXWELL TECHNOLOGIES» (США), реализованное в виде микросхемы HSH-3000, описанное в электронном каталоге фирмы MAXWELL по адресу в сети Интернета

.

Известное устройство содержит детектор излучений и некоторых частиц, усилитель, таймер, логику, выходные каскады.

Недостаткам известного устройства является низкая чувствительность при защите от возникновения тиристорного эффекта.

Наиболее близким по совокупности существенных признаков к изобретению является устройство, описанное в патенте РФ №2305894 под названием «Устройство для защиты интегральных микросхем при попадании в них тяжелых заряженных частиц». Известное устройство содержит датчик тока, включенный между входной клеммой и электронным переключателем, выход которого является выходом устройства. Датчик тока включен между входами усилителя сигналов датчика тока, выходы которого соединены с входами компаратора напряжения, подключенного к R-входу RS-триггера, который имеет приоритет по воздействию на R-вход. S-вход триггера соединен с генератором импульсной последовательности с большой скважностью. Инверсный выход триггера подключен к управляющему входу электронного переключателя, прямой выход - к базе мощного n-p-n транзистора, коллектор которого соединен с выходом устройства, а эмиттер - с общей шиной.

Недостатком известного устройства является пониженная помехоустойчивость по отношению к помехам, распространяющимся по шинам питания, что может привести к ложному срабатыванию защиты и, как следствие, к необоснованному выключению защищаемой аппаратуры. Другим недостатком известного устройства является возможность ложного срабатывания защиты при резких скачках тока потребления. Кроме того, недостатком известного устройства является возможность ложного срабатывания защиты в момент включения за счет емкостной составляющей, протекающей через датчик тока защищаемой микросхемы высокой степени интеграции, поскольку в этой ситуации кратковременно возрастает также и потребляемый ток. Такое возрастание тока потребления характерно именно для структур КМОП, из которых сегодня и строится вся вычислительная техника. Кроме того, также и триггер, выполненный на базе транзисторов n-p-n и p-n-р, имеет недостаточную устойчивость к помехам, распространяющимся по шинам питания.

Задачами настоящего изобретения являются повышение помехоустойчивости по отношению к помехам, распространяющимся по шинам питания, а также повышение надежности в работе защищающей микросхемы в части исключения ложных срабатываний защиты, обусловленных резким кратковременным увеличением тока потребления защищаемой микросхемы. Кроме того, задачей является повышение надежности за счет исключения ложных срабатываний защиты в момент включения в связи с зарядом конденсатора фильтра питания.

Техническим результатом настоящего изобретения является повышение помехоустойчивости и надежности работы радиоэлектронной аппаратуры при рассмотренных выше внешних воздействиях.

В настоящее время наиболее частой причиной отказа аппаратуры космических аппаратов (КА) является возникновение тиристорного эффекта в больших интегральных схемах. Более подробно этот вопрос освещен в книге Л.И.Чумакова «Действие космической радиации на интегральные схемы», Москва, Радио и связь, 2004 г. стр.6, 7, 9, 14, 27, 216, 217, 218, 225, 256, 272, 280, 282.

Защищаемыми микросхемами могут быть:

- микропроцессоры;

- микроконтроллеры:

- микросхемы оперативной памяти;

- микросхемы постоянной памяти;

- микросхемы АЦП, ЦАП и др.

Указанный технический результат достигается тем, что в известное устройство для защиты интегральных микросхем от тиристорного эффекта, содержащее датчик тока, резистивный мост, состоящий из первого и второго резистивных делителей, состоящих соответственно из последовательно включенных первого и второго резисторов и третьего и четвертого резисторов, при этом первый резистивный делитель включен между первым выводом датчика тока и общей шиной, второй резистивный делитель - между вторым выводом датчика тока и общей шиной, компаратор напряжения, генератор импульсной последовательности с большой скважностью, выход которого подключен к S-входу RS-триггера, мощный p-n-р транзистор, база которого подключена к инверсному выходу RS-триггера, n-p-n транзистор, база которого подключена к прямому выходу RS-триггера, а эмиттер - к общей шине, введены пятый, шестой, седьмой, восьмой, девятый и десятый резисторы, второй n-p-n транзистор, первый, второй и третий конденсаторы, первый, второй, третий, четвертый, пятый и шестой диоды, при этом входная клемма устройства соединена с первым выводом пятого резистора, коллектором второго n-p-n транзистора и с эмиттером мощного р-n-р транзистора, неинвертирующий вход компаратора соединен со средней точкой первого резистивного делителя, инвертирующий вход компаратора - со средней точкой второго резистивного делителя, между входами компаратора подключен первый конденсатор, шестой резистор подключен между вторым выводом пятого резистора и общей шиной, база второго n-p-n транзистора подключена к точке соединения пятого и шестого резисторов, первый диод анодом подсоединен к эмиттеру второго n-p-n транзистора, а катодом - к инвертирующему входу компаратора, второй диод подсоединен анодом к инвертирующему входу компаратора, а катодом - к неинвертирующему входу компаратора, первый вывод питания компаратора подключен к входной клемме, а второй вывод питания компаратора соединен с общей шиной, первый вывод датчика тока соединен с коллектором p-n-р транзистора, второй вывод датчика тока соединен с выходом устройства, между первым выводом датчика тока и общей шиной подключен второй конденсатор, седьмой резистор подключен между входной клеммой и выходом компаратора, катод третьего диода соединен с выходом компаратора, а анод этого диода - с анодом четвертого диода, катод последнего соединен с анодом пятого диода, катод которого соединен с R-входом RS-триггера, восьмой резистор подключен между входной клеммой и точкой соединения анодов третьего и четвертого диодов, между упомянутой точкой соединения диодов и общей шиной подключены последовательно соединенные третий конденсатор и девятый резистор, шестой диод катодом соединен с катодом четвертого диода, а анодом - с клеммой «Вх. имп.», между коллектором мощного p-n-р транзистора и коллектором первого n-p-п транзистора подключен десятый резистор.

При этом RS-триггер содержит первый и второй диод, первый и второй p-n-р транзистор, причем между базой и шиной питания каждого из этих транзисторов подключены соответственно первый и второй резисторы тепловой утечки, а эмиттер второго p-n-р транзистора подключен к шине питания, первый, второй и третий n-p-n транзисторы, причем между базой и общей шиной каждого из упомянутых транзисторов включены соответственно третий, четвертый и пятый резисторы тепловой утечки, эмиттеры первого и третьего n-p-n транзисторов подключены к общей шине, база первого n-p-n транзистора через шестой резистор соединена с входом R RS-триггера, коллекторы первого и второго n-р-n транзисторов соединены между собой, при этом через седьмой резистор они подключены к базе первого p-n-р транзистора, а через восьмой резистор - к базе второго p-n-р транзистора, коллектор третьего n-p-n транзистора через девятый резистор соединен с коллектором первого p-n-р транзистора, база третьего n-р-n транзистора через десятый резистор соединена с входом S RS-триггера, коллектор второго p-n-р транзистора соединен с инверсным выходом RS-триггера и через одиннадцатый резистор - с общей шиной, анод первого диода соединен с шиной питания, а катод - с эмиттером первого p-n-р транзистора, катод второго диода соединен с общей шиной, а его анод - с эмиттером второго n-p-n транзистора, между катодом первого диода и анодом второго диода подключен двенадцатый резистор, коллектор первого p-n-р транзистора через тринадцатый резистор соединен с прямым выходом RS-триггера, а между последним и общей шиной подключен четырнадцатый резистор.

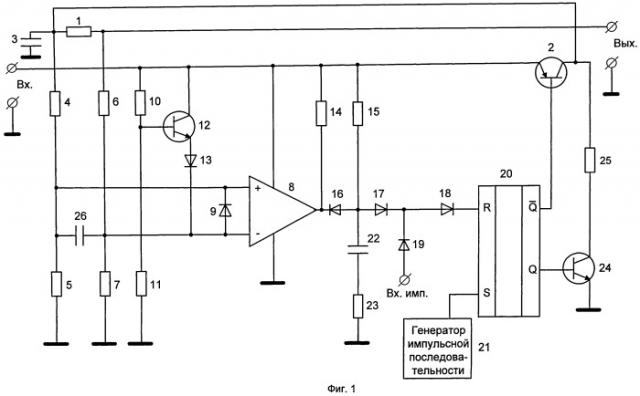

Сущность изобретения поясняется чертежами фиг.1 и фиг.2.

На фиг.1 представлена электрическая схема устройства для защиты интегральных микросхем от тиристорного эффекта. Это устройство содержит датчик 1 тока, первый вывод которого соединен с коллектором мощного р-n-р транзистора 2 и через конденсатор 3-е общей шиной, а также через первый резистивный делитель, состоящий из последовательно включенных резисторов 4 и 5, соединен с общей шиной. Второй вывод датчика тока соединен с выходной клеммой, а также через второй резистивный делитель, состоящий из последовательно включенных резисторов 6 и 7, соединен с общей шиной. Точка соединения резисторов 4 и 5 соединена с неинвертирующим входом компаратора напряжения 8 и с катодом диода 9. Инвертирующий вход компаратора 8 соединен с точкой соединения резисторов 6 и 7, а также с анодом диода 9. Между входной клеммой и общей шиной подключен делитель напряжения, состоящий из последовательно включенных резисторов 10 и 11, точка соединения которых подключена к базе транзистора 12 структуры n-p-n, коллектор которого подключен к входной клемме, а эмиттер соединен с анодом диода 13, катод которого соединен с инвертирующим входом компаратора. Входная клемма соединена с эмиттером транзистора 2, с первым выводом питания компаратора, через резистор 14-е выходом компаратора 8, через резистор 15-е точкой соединения анодов диодов 16 и 17. Катод диода 16 соединен с выходом компаратора 8. Катод диода 17 соединен с анодом диода 18 и с катодом диода 19, анод последнего подключен к клемме «Вх. имп.». Катод диода 18 соединен с входом R триггера 20, вход S последнего подключен к выходу генератора 21. Между общей шиной и точкой соединения анодов диодов 16 и 17 подсоединена цепочка из последовательно включенных конденсатора 22 и резистора 23. Инверсный выход триггера 20 соединен с базой транзистора 2. Прямой выход триггера соединен с базой n-p-n транзистора 24, эмиттер последнего соединен с общей шиной, коллектор через резистор 25 соединен коллектором транзистора 2, между входами компаратора 8 подсоединен конденсатор 26.

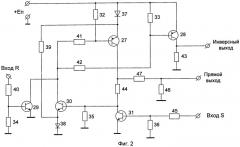

На чертеже фиг.2 представлена электрическая схема RS-триггера, входящего в состав устройства защиты, показанного на чертеже фиг.1. Клемма питания RS-триггера соединена с входной клеммой. RS-триггер содержит транзисторы 27, 28 структуры p-n-р и транзисторы 29, 30, 31 структуры n-p-n. Эмиттеры транзисторов 29 и 31 соединены с общей шиной, эмиттер транзистора 28 - с шиной питания. Между базами транзисторов 27 и 28 и шиной питания включены соответственно резисторы 32 и 33 тепловой утечки. Между базами транзисторов 29, 30, 31 и общей шиной включены соответственно резисторы 34, 35, 36 тепловой утечки. К эмиттеру транзистора 27 присоединен катод диода 37, анод которого соединен с шиной питания. К эмиттеру транзистора 30 присоединен анод диода 38, а катод последнего соединен с общей шиной. Между эмиттером транзистора 27 и эмиттером транзистора 30 подключен резистор 39, между входом R RS-триггера и базой транзистора 29 включен резистор 40. Коллектор транзистора 29 соединен с коллектором транзистора 30. Между коллектором транзистора 30 и базой транзистора 27 подключен резистор 41. Между коллектором транзистора 30 и базой транзистора 28 подключен резистор 42. Коллектор транзистора 28 соединен с инверсным выходом RS-триггера и через резистор 43 соединен с общей шиной. Между коллекторами транзисторов 31 и 27 подключен резистор 44. База транзистора 30 соединена с коллектором транзистора 31. Клемма «Вход S» RS-триггера через резистор 45 подключена к базе транзистора 31. Прямой выход RS-триггера через резистор 46 соединен с общей шиной и через резистор 47 соединен с коллектором транзистора 27.

Рассмотрим состояние устройства защиты в отсутствии воздействий, приводящих к возникновению тиристорного эффекта. При этом к выходу устройства защиты (см. фиг.1) по входу питания подключена защищаемая внешняя микросхема. Конденсатор, фильтрующий питание, подключен между общей шиной и входом датчика тока. При поданном входном напряжении начинает работать импульсный генератор 21, на выходе которого формируются положительные импульсы, поступающие с большим периодом следования. При частоте повторения два герца длительность импульсов составляет пять микросекунд. Эти импульсы поступают на вход S триггера 20 и вызывают открывание транзистора 31 (см. фиг.2). Транзисторы 27, 28, 29, 30 остаются закрытыми. Триггер 20 принимает первое устойчивое состояние, при котором транзистор 2 оказывается открыт и насыщен. Ток, открывающий этот транзистор, проходит по цепи: входной источник питания (клемма «Вход») - участок «эмиттер-база» транзистора 2 - резистор 43 - общая шина. Транзистор 24 закрыт, т.к. напряжение и ток в цепи его базы равны нулю. Напряжение на выходе устройства защиты равно напряжению на его входе за вычетом падения на открытом транзисторе 2. Транзистор 12 закрыт, поскольку напряжение на катоде диода 13 оказывается выше, чем на базе транзистора 12. Номиналы резисторов 4, 5, 6 и 7 выбираются таким образом, чтобы напряжение на втором (инвертирующем) входе компаратора оказывалось бы выше, чем напряжение на первом (неинвертирующем) входе компаратора. Напряжение на выходе компаратора 8 близко к нулевому значению. Диод 16 открыт, и ток протекает по цепи: клемма «Вход» - анод, катод диода 16 - выход компаратора 8 - общая шина. Диоды 17, 18 и 19 закрыты. Использование клеммы «Вх. имп.» делает возможным сокращение расхода энергии и ряда компонентов в том случае, когда необходима защита ряда микросхем высокой степени интеграции в одном и том же приборе. Это реализуется за счет веерного подключения к клемме «Вх. имп.» датчиков, включенных в различные цепи (включая дополнительные компараторы). Вновь введенные диоды 37, 38 и резистор 39 существенно повышают помехоустойчивость RS-триггера. Защищаемая микросхема, подключенная к выходу рассматриваемого устройства, функционирует нормально.

Теперь рассмотрим работу устройства защиты в аварийной ситуации. При возникновении одного из упомянутых выше возможных воздействий (ТЗЧ, ВЭП, ИИИ, пучковое оружие и др.) происходит срабатывание тиристорного эффекта, что приводит к нарастанию тока потребления и к дальнейшему разрушению микросхемы. Нарастание тока регистрируется на датчике 1 и далее приводит к выключению транзистора 2 и включению шунтирующего транзистора 24. Таким образом, предотвращается выход из строя защищаемой микросхемы. Рассмотрим этот процесс более подробно. Увеличение падения напряжения на датчике 1 приводит к тому, что напряжение на первом входе компаратора 8 становится выше, чем на втором входе. В результате напряжение на выходе компаратора 8 принимает высокий уровень, близкий к уровню напряжения питания. Вследствие этого диод 16 закрывается, а диоды 17 и 18 открываются. Ток проходит по цепи: шина питания - резистор 15 - диоды 17 и 18 - резисторы 40 и 34 - участок «база-эмиттер» транзистора 29 - общая шина. Это вызывает открывание транзисторов 29, 27, 30, 28 и переключение триггера 20 во второе устойчивое состояние. Все это приводит к закрыванию транзистора 2 и открыванию транзистора 24, что обеспечивает отключение питания от защищаемой микросхемы и быстрый разряд конденсатора, расположенного на выводах питания этой микросхемы. Ток, открывающий транзистор 24, проходит по цепи: входной источник питания - диод 37 - участок «эмиттер - коллектор» транзистора 27 - резистор 47 - участок «база-эмиттер» транзистора 24 - общая шина. Таким образом, реализуется защита от катастрофического отказа микросхемы, подключаемой к выходу рассматриваемого устройства, при попадании ТЗЧ, ВЭП, ИИИ, воздействии пучкового оружия и др. Именно таким образом защита парирует возможные внешние разрушающие воздействия. В рассматриваемой аварийной ситуации от генератора 21 на вход S триггера 20 продолжают поступать кратковременные импульсы с большим периодом повторения. Эти импульсы стремятся перевести триггер 20 в первое устойчивое состояние. При этом возможны два сценария поведения устройства защиты. Если одновременно на вход R триггера 20 поступает напряжение высокого уровня, которое имеет приоритет перед сигналами, поступающими на вход S, то триггер принимает второе устойчивое состояние, соответствующее состоянию защиты. Если же активные сигналы на входе R отсутствуют, то триггер 20 принимает первое устойчивое состояние за счет импульсов, поступающих на вход S, что соответствует рабочему режиму. После выключения транзистора 2 могла бы возникнуть неопределенная ситуация по уровню напряжения на выходе компаратора 8 из-за неопределенности на входах компаратора. Наличие транзистора 12 позволяет избежать этой неопределенности. После выключения транзистора 2 напряжения на входах компараторов снижаются. Уровень напряжения на базе транзистора 12 становится выше, чем на катоде диода 13 и, следовательно, выше, чем на эмиттере транзистора 12. Напряжение на первом входе компаратора фиксируется на уровне, определяемом делителем на резисторах 10 и 11. Далее открывается диод 9. Ток при этом протекает по цепи: точка соединения резисторов 10 и 11 - участок «база - эмиттер» транзистора 12 - анод, катод диода 13 - анод, катод диода 9 - резистор 5. Напряжение на втором входе компаратора оказывается выше, чем на первом входе, а на выходе компаратора удерживается низкий уровень напряжения, что позволяет триггеру 20 принимать как первое, так и второе устойчивое состояние. В дальнейшем при поступлении импульсов на вход S происходит включение транзистора 2 в том случае, если отсутствуют сигналы на входе R. Клемма «Вх. имп.» может использоваться для подключения к выходам других компараторов, в свою очередь, связанных с другими датчиками тока. Таким образом, в рассматриваемом устройстве по сравнению с известным удается исключить ложное срабатывание защиты в момент включения за счет исключения емкостной составляющей, протекающей через датчик тока, обусловленной наличием конденсатора, подсоединенного к выходным клеммам. Следует отметить, что в самом устройстве защиты принципиально не содержится структур, в которых мог бы возникнуть тиристорный эффект.

В предложенном устройстве удалось существенно повысить надежность за счет исключения возможности ложных срабатываний защиты, обусловленных возникновением помех, распространяющихся по шинам питания. В предложенном устройстве также удалось существенно повысить надежность за счет исключения возможности ложных срабатываний защиты, обусловленных возникновением кратковременного импульса тока потребления защищаемой интегральной схемы, вызываемого увеличением скорости работы упомянутой интегральной схемы. Эти новые свойства устройства защиты обеспечиваются благодаря введению конденсаторов 22, 26, резисторов 10, 11, 14, 15, 23, 39, диодов 9, 13, 16, 17, 18, 19, 37, 38, транзистора 12.

Использование предложенного устройства позволит существенно повысить надежность работы системы, состоящей из защищаемой интегральной схемы и защищающего устройства (микросхемы).

Макет предлагаемого устройства защиты прошел натурные испытания и показал положительные результаты. Защищаемой большой интегральной схемой (БИС) была выбрана БИС оперативного запоминающего устройства (ЗУ). Ранее при воздействии ТЗЧ такая БИС ЗУ всякий раз выходила из строя под воздействием ТЗЧ, когда она включалась без устройства защиты. В то же время, при включении совместно с устройством защиты, защита срабатывала всякий раз, когда появлялся поток ТЗЧ. Последующая проверка показала, что испытуемая БИС ЗУ в этом случае оказывались целой и невредимой. После воздействия ТЗЧ информация записывалась во все ячейки памяти БИС ЗУ, затем считывалась. При этом наблюдалось полное совпадение записанной и считанной информации. При проведении испытаний экспериментально подтверждена функциональная работоспособность макета защищающей микросхемы (отключение тока потребления и отключение электропитания защищаемой БИС) при воздействии на защищаемую БИС заряженных частиц. При возникновении в защищаемой БИС тиристорного эффекта защищающее устройство предотвращает выход защищаемой БИС из строя.

В настоящее время интегральные микросхемы защиты, рассмотренные выше, отсутствуют как на Российском внутреннем рынке, так и на международном рынке. В настоящее время предложенное устройство проектируется в виде интегральной микросхемы защиты.

1. Устройство для защиты интегральных микросхем от тиристорного эффекта, содержащее датчик тока, резистивный мост, состоящий из первого и второго резистивных делителей, состоящих соответственно из последовательно включенных первого и второго резисторов и третьего и четвертого резисторов, при этом первый резистивный делитель включен между первым выводом датчика тока и общей шиной, второй резистивный делитель - между вторым выводом датчика тока и общей шиной, компаратор напряжения, генератор импульсной последовательности с большой скважностью, выход которого подключен к S-входу RS-триггера, мощный p-n-р транзистор, база которого подключена к инверсному выходу RS-триггера, первый n-p-n транзистор, база которого подключена к прямому выходу RS-триггера, а эмиттер - к общей шине, отличающееся тем, что в него введены пятый, шестой, седьмой, восьмой, девятый и десятый резисторы, второй n-p-n транзистор, первый, второй и третий конденсаторы, первый, второй, третий, четвертый, пятый и шестой диоды, при этом входная клемма устройства соединена с первым выводом пятого резистора, коллектором второго n-р-n транзистора и с эмиттером мощного p-n-р транзистора, неинвертирующий вход компаратора соединен со средней точкой первого резистивного делителя, инвертирующий вход компаратора - со средней точкой второго резистивного делителя, между входами компаратора подключен первый конденсатор, шестой резистор подключен между вторым выводом пятого резистора и общей шиной, база второго n-p-n транзистора подключена к точке соединения пятого и шестого резисторов, первый диод анодом подсоединен к эмиттеру второго n-р-n транзистора, а катодом - к инвертирующему входу компаратора, второй диод подсоединен анодом к инвертирующему входу компаратора, а катодом - к неинвертирующему входу компаратора, первый вывод питания компаратора подключен к входной клемме, а второй вывод питания компаратора соединен с общей шиной, первый вывод датчика тока соединен с коллектором р-n-р транзистора, второй вывод датчика тока соединен с выходом устройства, между первым выводом датчика тока и общей шиной подключен второй конденсатор, седьмой резистор подключен между входной клеммой и выходом компаратора, катод третьего диода соединен с выходом компаратора, а анод этого диода - с анодом четвертого диода, катод последнего соединен с анодом пятого диода, катод которого соединен с R - входом RS-триггера, восьмой резистор подключен между входной клеммой и точкой соединения анодов третьего и четвертого диодов, между упомянутой точкой соединения диодов и общей шиной подключены последовательно соединенные третий конденсатор и девятый резистор, катод шестого диода соединен с катодом четвертого диода, а анод - с клеммой "Вх. имп.», между коллектором мощного p-n-р транзистора и коллектором первого n-p-n транзистора подключен десятый резистор.

2. Устройство по п.1, отличающееся тем, что RS-триггер содержит первый и второй диоды, первый и второй p-n-р транзисторы, причем между базой и шиной питания каждого из этих транзисторов подключены соответственно первый и второй резисторы тепловой утечки, а эмиттер второго p-n-р транзистора подключен к шине питания, первый, второй и третий n-p-n транзисторы, причем между базой и общей шиной каждого из упомянутых транзисторов включены соответственно третий, четвертый и пятый резисторы тепловой утечки, эмиттеры первого и третьего n-p-n транзисторов подключены к общей шине, база первого n-р-n транзистора через шестой резистор соединена с входом R RS-триггера, коллекторы первого и второго n-p-n транзисторов соединены между собой, при этом через седьмой резистор они подключены к базе первого p-n-р транзистора, а через восьмой резистор - к базе второго p-n-р транзистора, коллектор третьего n-р-n транзистора через девятый резистор соединен с коллектором первого р-n-р транзистора, база третьего n-p-n транзистора через десятый резистор соединена с входом S RS-триггера, коллектор второго p-n-р транзистора соединен с инверсным выходом RS-триггера и через одиннадцатый резистор - с общей шиной, анод первого диода соединен с шиной питания, а катод - с эмиттером первого р-n-р транзистора, катод второго диода соединен с общей шиной, а его анод - с эмиттером второго n-р-n транзистора, между катодом первого диода и анодом второго диода подключен двенадцатый резистор, коллектор первого р-n-р транзистора через тринадцатый резистор соединен с прямым выходом RS-триггера, а между последним и общей шиной подключен четырнадцатый резистор.