Сдвиговый регистр, схема управления дисплеем, панель отображения и устройство отображения

Иллюстрации

Показать всеИзобретение относится к сдвиговому регистру и различным видам схем управления дисплеем. Техническим результатом является обеспечение быстрого выполнения (i) одновременного выбора множества линий сигнала и (ii) инициализации сдвигового регистра. Сдвиговый регистр схемы управления дисплеем осуществляет одновременный выбор множества линий сигнала, используя сигнал одновременного выбора (сигнал AONB). Каскад сдвигового регистра включает в себя (i) RS-триггер и (ii) схему генерирования сигнала, которая генерирует выходной сигнал каскада путем избирательного вывода сигнала в ответ на выход триггера. Выходной сигнал (например, сигнал OUTn) каскада (i) становится активным в результате активации сигнала одновременного выбора и затем (ii) остается активным во время выполнения одновременного выбора, а выход (сигнал Qn) из триггера является неактивным (Низким) в течение периода, в который сигнал (SBn) установки и сигнал (Rn) сброса оба являются активными. Это позволяет быстро осуществлять одновременный выбор всех линий сигнала и инициализацию сдвигового регистра. 6 н. и 23 з.п. ф-лы, 35 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к сдвиговому регистру и различным видам схем управления дисплеем.

Уровень техники

В Патентной литературе 1 (см. фиг.34) раскрыта конфигурация, в которой выход каждого каскада сдвигового регистра, включенный в схему управления затвором, подают в схему И-НЕ, и сигнал DCG также подают в схему И-НЕ. Кроме того, выход схемы И-НЕ подают в соответствующую линию сигнала развертки. При такой конфигурации, делая сигнал DCG активным, когда источник питания устройства жидкокристаллического дисплея включают или выключают, можно одновременно выбирать все линии сигнала развертки так, что Vcom (электрический потенциал общего электрода) будет записан во все пиксели.

В Патентной литературе 2 (см. фиг.35) раскрыта схема управления затвором, которая включает в себя сдвиговый регистр, имеющий множество каскадов. Каждый из множества каскадов имеет (i) RS-триггер и (ii) схему затвора, включающую в себя аналоговый переключатель 43 и транзистор 45 с n-каналом. Кроме того, сигнал СК тактовой частоты подают в аналоговый переключатель 43, исток транзистора 44 с n-каналом соединен с VSS, и выход каждого из каскадов подают в соответствующие линии сигнала развертки. В этой конфигурации, когда источник питания устройства жидкокристаллического дисплея включают или выключают, выходные сигналы всех каскадов становятся активными, путем обеспечения активного сигнала установки в первом каскаде сдвигового регистра, в то время как сигнал СК тактовой частоты является постоянно активным. Это позволяет одновременно выбирать все линии сигнала развертки так, что Vcom (электрический потенциал общего электрода) записывается во все пиксели.

Список литературы

Патентная литература

Патентная литература 1

Публикация Tokukai №2000-347627 заявки на японский патент (Дата публикации: 15 декабря 2000 г.)

Патентная Литература 2

Международная Публикация № WO 2007/108177 (Дата публикации: 27 сентября 2007 г.)

Раскрытие изобретения

Техническая задача

В обычной схеме управления затвором возникает проблема, состоящая в том, что время установки для включения или выключения источника питания является продолжительным, поскольку необходимо инициализировать триггер (то есть сделать выход неактивным) каждого из каскадов сдвигового регистра после того, как все линии сигнала развертки будут одновременно выбраны.

Цель настоящего изобретения состоит в том, чтобы обеспечить сдвиговый регистр и различные виды схем управления, каждая из которых быстро выполняет (i) одновременный выбор множества линий сигнала и (ii) инициализацию сдвигового регистра.

Решение задачи

Сдвиговый регистр в соответствии с настоящим изобретением представляет собой, например, сдвиговый регистр, предназначенный для использования в схеме управления дисплеем, которая выполняет одновременный выбор множества линий сигнала в заданные моменты времени, при этом каскад сдвигового регистра включает в себя (i) RS-триггер и (ii) схему генерирования сигнала, принимающую сигнал одновременного выбора, причем схема генерирования сигнала генерирует выходной сигнал каскада путем использования выхода триггера; выходной сигнал каскада (i) становится активным в результате активации сигналом одновременного выбора и затем (ii) остается активным во время одновременного выбора; и выход триггера является неактивным в течение периода, в котором сигнал установки и сигнал сброса оба являются активными.

В течение периода, в который выполняют одновременный выбор, выходной сигнал каждого из каскадов является активным. Это делает активными как сигнал установки, так и сигнал сброса, которые подают в триггер каждого из каскадов. В одной конфигурации используется триггер, который остается неактивным в течение периода, в течение которого как сигнал установки, так и сигнал сброса одновременно являются активными. Соответственно, триггер каждого из каскадов инициализируется (то есть становится неактивным) во время выполнения одновременного выбора. Это позволяет быстро закончить одновременный выбор и инициализацию сдвигового регистра, поскольку сдвиговый регистр инициализируется при осуществлении одновременного выбора. Кроме того, становится возможным уменьшить размер каждой из различных схем управления, работающих со сдвиговым регистром, поскольку нет необходимости обеспечивать конфигурацию для генерирования и передачи сигнала для инициализации сдвигового регистра.

Полезные результаты изобретения

Как описано выше, настоящее изобретение позволяет быстро выполнить (i) одновременный выбор множества линий сигнала и (ii) инициализировать сдвиговый регистр.

Краткое описание чертежей

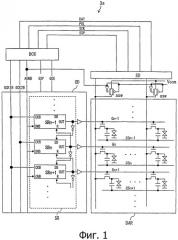

На фиг.1 схематично представлен вид, иллюстрирующий конфигурацию устройства жидкокристаллического дисплея варианта 1 осуществления настоящего изобретения.

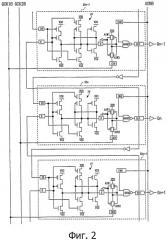

На фиг.2 представлена принципиальная схема, частично иллюстрирующая сдвиговый регистр устройства жидкокристаллического дисплея, показанного на фиг.1.

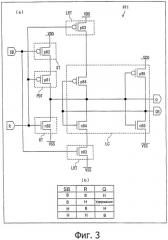

На фиг.3 (а) представлена принципиальная схема триггера сдвигового регистра, показанного на фиг.2, и (b) таблица истинности триггера.

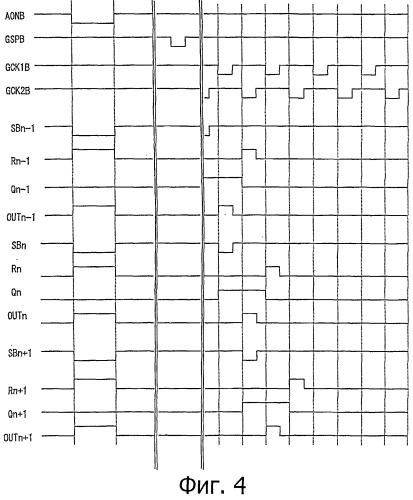

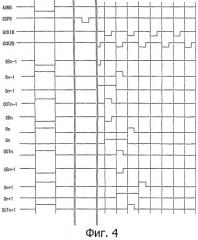

На фиг.4 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.1.

На фиг.5 схематично представлен вид, иллюстрирующий другую конфигурацию устройства жидкокристаллического дисплея варианта 1 осуществления настоящего изобретения.

На фиг.6 схематично представлен вид, иллюстрирующий еще одну конфигурацию устройства жидкокристаллического дисплея варианта 1 осуществления настоящего изобретения.

На фиг.7 показана принципиальная схема, иллюстрирующая каждый каскад сдвигового регистра устройства жидкокристаллического дисплея, показанного на фиг.6.

На фиг.8 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.6.

На фиг.9 показана принципиальная схема, иллюстрирующая каждый каскад сдвигового регистра устройства жидкокристаллического дисплея, показанного на фиг.6.

На фиг.10 схематично представлен вид, иллюстрирующий конфигурацию устройства жидкокристаллического дисплея варианта 2 осуществления настоящего изобретения.

На фиг.11 представлена принципиальная схема, частично иллюстрирующая сдвиговый регистр устройства жидкокристаллического дисплея, показанного на фиг.10.

На фиг. 12(а) представлена принципиальная схема триггера сдвигового регистра, показанного на фиг.11, и (b) - таблица истинности триггера.

На фиг.13 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.10.

На фиг.14 схематично представлен вид, иллюстрирующий другую конфигурацию устройства жидкокристаллического дисплея варианта 2 осуществления настоящего изобретения.

На фиг.15 представлена принципиальная схема, частично иллюстрирующая сдвиговый регистр устройства жидкокристаллического дисплея, показанного на фиг.14.

На фиг.16 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.14.

На фиг.17 показана принципиальная схема, иллюстрирующая конкретную конфигурацию схемы И-НЕ, показанной на фиг.15.

На фиг.18(а) показана другая принципиальная схема триггера сдвигового регистра, показанного на фиг.10 или 14, и (b )- таблица истинности триггера.

На фиг.19(а) показана другая принципиальная схема триггера сдвигового регистра, показанного на фиг.10 или 14, и (b) - таблица истинности триггера.

На фиг.20(а) показана другая принципиальная схема триггера сдвигового регистра, показанного на фиг.10 или 14, и (b) - таблица истинности триггера.

На фиг.21 схематично представлен вид, иллюстрирующий еще одну конфигурацию устройства жидкокристаллического дисплея варианта 2 осуществления настоящего изобретения.

На фиг.22 представлена принципиальная схема, частично иллюстрирующая сдвиговый регистр устройства жидкокристаллического дисплея, показанного на фиг.21.

На фиг.23 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.21.

На фиг.24 показана принципиальная схема, иллюстрирующая конкретную конфигурацию схемы NOR, показанной на фиг.22.

На фиг.25 схематично представлен вид, иллюстрирующий конфигурацию устройства жидкокристаллического дисплея варианта 3 осуществления настоящего изобретения,

На фиг.26 показана принципиальная схема, иллюстрирующая каждый каскад сдвигового регистра устройства жидкокристаллического дисплея, показанного на фиг.25.

На фиг.27 показана принципиальная схема, иллюстрирующая схему D-защелки схемы CS управления затвора устройства жидкокристаллического дисплея, показанного на фиг.25.

На фиг.28 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.25.

На фиг.29 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг, 25.

На фиг.30 схематично представлен вид, иллюстрирующий конфигурацию устройства жидкокристаллического дисплея варианта 4 осуществления настоящего изобретения.

На фиг.31 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на фиг.30.

На фиг.32 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея, показанным на Фиг.30, управляют.

На фиг.33 показана принципиальная схема, иллюстрирующая каждый каскад сдвигового регистра устройства жидкокристаллического дисплея, показанного на фиг.15.

Фиг.34 показана принципиальная схема, иллюстрирующая конфигурацию обычного сдвигового регистра.

На фиг.35 показана принципиальная схема, иллюстрирующая конфигурацию обычного сдвигового регистра.

Осуществление изобретения

Ниже описаны варианты осуществления настоящего изобретения со ссылкой на фиг.1-33.

Следует отметить, что в следующем описании предполагается, что RS-триггер (ниже иногда называется "FF") имеет (i) вывод установки (вывод S или вывод SB), на который подают сигнал установки (сигнал S или сигнал SB), (ii) вывод сброса (вывод R или вывод RB), на который подают сигнал сброса (сигнал R или сигнал RB), (iii) выходной вывод (вывод Q), из которого выводят сигнал Q, и (iv) инвертированный выходной вывод (вывод QB), из которого выводят сигнал QB. Следует отметить, что электрический потенциал стороны высокого потенциала источника питания (VDD) обозначается "Vdd" (ниже также иногда называется как "Высокий"), и электрический потенциал на стороне низкого потенциала источника питания (VSS) обозначается "Vss" (ниже иногда также называется "Низкий"). Сигнал S (сигнал установки), сигнал R (сигнал сброса) и сигнал Q (выходной сигнал) становятся высокими, когда каждый из этих сигналов находится в активном состоянии. Сигнал SB (сигнал шины установки), сигнал RB (сигнал шины сброса) и сигнал QB (инвертированный выходной сигнал) становятся низкими, когда каждый из этих сигналов находится в активном состоянии.

Вариант 1 осуществления

На фиг.1 показана схема цепей, иллюстрирующая конфигурацию устройства 3а жидкокристаллического дисплея в соответствии с настоящим изобретением. Устройство 3а жидкокристаллического дисплея включает в себя блок DAR дисплея, схему GD управления затвором, схему SD управления истоком и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором сигнал AONB (сигнал все включены), импульс GSP запуска затвора, сигнал GOE разрешения работы затвора и сигналы GCK1B и GCK2B тактовой частоты затвора. Кроме того, схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвором включает в себя сдвиговый регистр SR, имеющий множество каскадов. Ниже i-ый каскад (i=1,… n-1, n, n+1,…) сдвигового регистра кратко называется "i-ым каскадом SRi", соответственно.

Выходной сигнал (сигнал OUT) i-ого каскада SRi сдвигового регистра подают в линию Gi сигнала развертки блока DAR дисплея через буфер. Например, выходной сигнал n-ого каскада SRn подают в линию Gn сигнала развертки через буфер. В блоке DAR дисплея линия Gn сигнала развертки соединена с затвором транзистора, который соединен через электрод пикселя с пикселем PIXn. Конденсатор удержания (вспомогательный конденсатор) сформирован электродом пикселя в пикселе PIXn и линии CSn конденсатора удержания.

Кроме того, один (1) аналоговый переключатель asw и один (1) инвертор предусмотрены для каждой линии сигнала данных. Инвертор имеет входной вывод, соединенный с линией сигнала AONB. Один электропроводный вывод аналогового переключателя asw соединен с концом линии сигнала данных, и другой электропроводный вывод аналогового переключателя asw соединен с Vcom (электрический потенциал общего электрода) источника питания. Затвор на стороне n-канала аналогового переключателя asw соединен с выходным выводом инвертора, и затвор на стороне р-канала аналогового переключателя asw соединен с линией сигнала AONB.

На фиг.2 показана принципиальная схема, частично иллюстрирующая конкретную конфигурацию сдвигового регистра SR. Как показано на фиг.2, каждый из каскадов сдвигового регистра включает в себя (i) RS-триггер FF, вывод SB и вывод R, (ii) два аналоговых переключателя ASW1 и ASW2, (iii) схему И-НЕ, (iv) два инвертора, (v) вывод СКВ, (vi) вывод ONB и (vii) вывод OUT. Вывод Q триггера FF соединен с затвором на стороне р-канала аналогового переключателя ASW1, затвором на стороне n-канала аналогового переключателя ASW2 и входным выводом одного из двух инверторов. Выходной вывод одного из этих двух инверторов соединен с затвором на стороне n-канала аналогового переключателя ASW1 и затвором на стороне р-канала аналогового переключателя ASW2. Один электропроводный электрод аналогового переключателя ASW1 соединен с VDD, и один электропроводный электрод аналогового переключателя ASW2 соединен с выводом СКВ. Другой электропроводный электрод аналогового переключателя ASW1, другой электропроводный электрод аналогового переключателя ASW2 и один входной вывод схемы И-НЕ соединены друг с другом. Другой входной вывод схемы И-НЕ соединен с выводом ONB. Выходной вывод схемы И-НЕ соединен с выводом OUT, который используется как выходной вывод первого каскада.

В сдвиговом регистре SR каждый из каскадов имеет (i) вывод OUT, который соединен с выводом SB следующего каскада для каскада через другой из двух инверторов и (ii) вывод R, который соединен с выводом OUT следующего каскада для каскада. Например, вывод OUT п-ого каскада SRn соединен с выводом SB (n+1) каскада SRn+1 через инвертор, и вывод OUT (n+1)-ого каскада SRn+1 соединен с выводом R п-ого каскада SRn. Следует отметить, что первый каскад SR1 сдвигового регистра SR имеет вывод SB, на который подают сигнал GSPB. В схеме GD управления затвором вывод СКВ каскада с нечетным номером соединен с линией GCK (через которую подают сигнал GCK тактовой частоты затвора), которая отличается от линии GCK, с которой соединен вывод СКВ каскада с четными номерами. Например, вывод СКВ n-ого каскада SRn соединен с линией сигнала GCK2B, и вывод СКВ (n+1)-ого каскада SRn+1 соединен с линией сигнала GCK1B.

В качестве триггера FF, показанного на фиг.2, используется триггер FF1, показанный на фиг.3. Как показано на фиг.3, триггер FF1 включает в себя (i) транзистор р84 с р-каналом и транзистор n84 с n-каналом, которые составляют схему КМОП, (ii) транзистор р85 с р-каналом и транзистор n85 с n-каналом, которые составляют схему КМОП, (iii) транзисторы р81, р82, и р83 с р-каналом, (iv) транзисторы n82 и n83 с n-каналом и (v) вывод SB, вывод R, вывод Q и вывод QB. Затвор транзистора р84, затвор транзистора n84, сток транзистора р85, сток транзистора n85 и вывод QB соединены друг с другом. Сток транзистора р84, сток транзистора n84, сток транзистора р81, сток транзистора n82, затвор транзистора р85, затвор транзистора n85 и вывод Q соединены друг с другом. Исток транзистора n84 соединен со стоком транзистора n83. Исток 8 транзистора р84 соединен со стоком транзистора р83. Исток транзистора р81 соединен со стоком транзистора р82. Вывод SB соединен с затвором транзистора р82 и затвором транзистора n83. Вывод R соединен с затвором транзистора n82, затвором транзистора р81 и затвором транзистора р83. Исток транзистора n85 соединен с VSS. Истоки транзисторов р82, р83 и р85 соединены с VDD. Истоки транзисторов n82 и n83 соединены с VSS. Здесь транзисторы р84, n84, р85 и n85 составляют схему LC защелки, транзистор р82 используется как транзистор ST установки, транзистор n82 используется как транзистор RT сброса, каждый из транзисторов р83 и n83 используется как транзистор LRT высвобождения защелки и транзистор р81 используется как транзистор PDT определения приоритета.

В позиции (b) на фиг.3 показана таблица истинности триггера FF1. Сигнал Q триггера FF1 должен иметь следующие состояния (см. позицию (b) на фиг.3): в течение периода, в который сигнал SB является высоким (неактивным) и сигнал R является высоким (активным), сигнал Q является низким (неактивным); в течение периода, в который сигнал SB является высоким (неактивным) и сигнал R является низким (неактивным), сигнал Q находится в состоянии удержания; в течение периода, в который SB является низким (активным) и сигнал R является высоким (активным), сигнал Q является низким (неактивным); и в течение периода, в который сигнал SB является низким (активным) и сигнал R является низким (неактивным), сигнал Q является высоким (активным). В триггере FF1 транзистор п82 включается, когда сигнал SB и сигнал R оба становятся активными, и, соответственно, сигнал Q переключают так, чтобы он имел состояние Vss (Низкое). Это приводит к тому, что сигнал R (сброс) получает приоритет.

На фиг.4 показана временная диаграмма, иллюстрирующая, как осуществляют управление устройством 3а жидкокристаллического дисплея. Следует отметить, что на фиг.4, "AONB" обозначает сигнал AONB (сигнал все включены), "GSPB" обозначает сигнал шины импульса запуска затвора, "GCK1B" обозначает сигнал GCK1B, "GCK2B" обозначает сигнал GCK2B. Кроме того, "SBi", "Ri", "Qi" и "OUTi" (i=n-1, n, n+1) обозначают сигнал SB (то есть электрический потенциал на выводе SB), сигнал R (то есть электрический потенциал на выводе R), сигнал Q (то есть электрический потенциал на выводе Q) и сигнал OUT (то есть электрический потенциал на выводе OUT) в i-ом каскаде SRi, соответственно.

В устройстве 3а жидкокристаллического дисплея следующая операция подготовки дисплея осуществляется перед первым кадром (период вертикальной развертки) отображаемого видеоизображения. В частности, сигнал AONB переводят в состояние активный (Низкий) в течение заданного периода времени. В каждом из каскадов сдвигового регистра SR один из входов в схему И-НЕ становится низким и, соответственно выход схемы И-НЕ становится высоким. Это обеспечивает то, что сигналы OUT всех каскадов становятся активными (Высокими) и соответственно все линии сигнала развертки будут выбраны. В это время, аналоговые переключатели asw, предусмотренные для соответствующих линий сигнала данных, включают и соответственно Vcom прикладывают ко всем линиям сигнала данных. Кроме того, сигнал SB, подаваемый в триггер FF каждого из каскадов, становится активным (Низким), и сигнал R, подаваемый в триггер FF, также становится активным (Высоким) и соответственно сигнал Q триггера FF становится неактивным (Низким). Это связано с тем, что в триггере FF сигнал R (сброс) имеет приоритет в случае, когда сигнал SB и сигнал R одновременно становятся активными. После того, как операция подготовки отображения будет закончена (то есть после того, как сигнал AONB станет неактивным), Vcom записывают во все пиксели PIX в блоке DAR дисплея, и сигналы Q соответствующих триггеров FF сдвигового регистра SR становятся неактивными (Низкими).

Кроме того, в сдвиговом регистре SR устройства 3а жидкокристаллического дисплея выполняется следующая операция в каждый период вертикальной развертки (при котором отображается кадр). В частности, каждый каскад сдвигового регистра SR выполнен следующим образом. Когда сигнал SB, подаваемый в каскад сдвигового регистра SR, становится активным (= Низким), триггер FF каскада устанавливают и соответственно сигнал Q становится высоким (активным). Это приводит к приему сигнала GCKB каскадом через аналоговый переключатель ASW2. Когда сигнал GCKB в каскаде становится активным (= Низким), сигнал OUT каскада становится активным (Высоким), и сигнал SB в следующем каскаде для каскада становится активным. Это приводит к тому, что сигнал OUT триггера FF в следующем каскаде для данного каскада становится активным и соответственно сигнал GCKB принимают в следующем каскаде для каскада. Когда сигнал GCKB в следующем каскаде для каскада становится активным (= Низким), триггер FF каскада сбрасывают и соответственно сигнал Q становится низким (неактивным). Это приводит к тому, что аналоговый переключатель ASW1 каскада включают. В это время сигнал АОВ является высоким, и соответственно, оба входа в схему И-НЕ каскада становятся высокими, и выход схемы И-НЕ становится низким. Это приводит к тому, что сигнал OUT каскада становится низким (неактивным, то есть происходит инициализация триггера FF).

В устройстве 3а жидкокристаллического дисплея, например, становится возможным применять идентичный электрический потенциал (например, Vcom) ко всем пикселям путем одновременного выбора всех линий сигнала развертки перед началом отображения. Это позволяет предотвратить представление неупорядоченного экрана, перед началом отображения или после окончания отображения. Кроме того, сдвиговый регистр инициализируется (триггеры соответствующих каскадов инициализируются), когда выполняют одновременный выбор всех линий сигнала развертки. Это обеспечивает возможность выполнять операцию подготовки перед началом отображения более быстро, по сравнению с обычным устройством жидкокристаллического дисплея, которое отдельно выполняет одновременный выбор всех линий сигнала развертки и инициализацию сдвигового регистра. Кроме того, нет необходимости подготавливать конфигурацию для генерирования и передачи сигнала инициализации для сдвигового регистра и поэтому становится возможным уменьшить размер схемы управления затвором.

На фиг.5 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3b жидкокристаллического дисплея, в котором сдвиговый регистр SR, показанный на фиг.1, предусмотрен на стороне схемы управления истоком. В этой конфигурации импульс SSP запуска истока подают в первый каскад сдвигового регистра SR, и сигнал SCK1B или SCK2B панели тактовой частоты истока подают в вывод СКВ каждого каскада. Кроме того, сигнал OUT, выводимый из i-ого каскада Sri, подают в схему SAC выборки, и данные, отобранные на основе сигнала OUT, подают в линию SLi сигнала данных блока DAR дисплея через DAC. Например, сигнал OUT n-ого каскада SRn подают в схему SAC выборки, и затем данные, отобранные на основе сигнала OUT, подают в линию SLn сигнала данных блока DAR дисплея через DAC. В блоке DAR дисплея линию SLn сигнала данных соединяют с истоком транзистора, соединенным с электродом пикселя в пикселе PIXn.

На фиг.6 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3с жидкокристаллического дисплея, которое выполнено путем модификации устройства 3а жидкокристаллического дисплея. В устройстве 3с жидкокристаллического дисплея выходной сигнал (OUTB-сигнал) i-ого каскада SRi сдвигового регистра подают в линию Gi сигнала развертки блока DAR дисплея через инвертор. Например, сигнал OUTB n-ого каскада SRn подают в линию Gn сигнала развертки через инвертор. В блоке DAR дисплея линия Gn сигнала развертки соединена с затвором транзистора, который подключен к электроду пикселя в пикселе PIXn. Конденсатор удержания (вспомогательный конденсатор) формируется с помощью электрода пикселя в пикселе PIXn и линии CSn конденсатора удержания.

На фиг.7 показана принципиальная схема, иллюстрирующая конфигурацию i-ого каскада SRi сдвигового регистра SR. Как показано на фиг.7, i-ый каскад SRi включает в себя (i) SR-триггер FF, имеющий вывод SB и вывод R, (ii) два аналоговых переключателя ASW3 и ASW4, (iii) логическую схему AND, (iv) инвертор и (v) вывод СКВ, вывод ONB и вывод OUTB. Вывод Q триггера FF соединен с затвором стороны р-канала аналогового прееключателя ASW3, с затвором стороны n-канала аналогового переключателя ASW4 и входным выводом инвертора. Выходной вывод инвертора соединен с затвором стороны n-канала аналогового переключателя ASW3 и затвором стороны р-канала аналогового переключателя ASW4. Один электропроводный электрод аналогового переключателя ASW3 соединен с VDD, и один электропроводный электрод аналогового переключателя ASW4 соединен с выводом СКВ. Другой электропроводный электрод аналогового переключателя ASW3, другой электропроводный электрод аналогового переключателя ASW4 и один входной вывод схемы AND соединены друг с другом. Другой входной вывод схемы AND соединен с выводом ONB. Выходной вывод схемы AND соединен с выводом OUTB, который используется как выходной вывод для этого каскада.

В сдвиговом регистре SR каждый из каскадов имеет (i) вывод OUTB, который соединен с выводом SB следующего каскада, и (ii) вывод R, который соединен с выводом OUTB следующего каскада через инвертор. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, и вывод OUTB (n+1)-ого каскада SRn+1 соединен с выводом R n-ого каскада SRn через инвертор. Следует отметить, что первый каскад SR1 сдвигового регистра SR имеет вывод SB, на который подают сигнал GSPB. В схеме GD управления затвором вывод СКВ каскада с нечетным номером соединен с линией GCK (через которую подают сигнал GCK тактовой частоты затвора), который отличается от линии GCK, с которой соединен вывод СКВ каскада с четным номером. Например, вывод СКВ n-ого каскада SRn соединен с линией сигнала GCK2B, и вывод СКВ (n+1)-ого каскада SRn+1 соединен с линией сигнала GCK1B.

На фиг.8 показана временная диаграмма, иллюстрирующая, как осуществляется управление устройством 3c жидкокристаллического дисплея. В устройстве 3c жидкокристаллического дисплея следующую операцию подготовки дисплея выполняют перед первым кадром (период вертикальной развертки) при отображении видеоизображения. В частности, сигнал AONB делают активным (Низким) в течение заданного периода времени, и в каждом из каскадов сдвигового регистра SR один из входов схемы AND становится низким, и соответственно выход схемы AND становится Низким. Это приводит к тому, что сигналы OUTB на всех каскадах становятся активными (Низкими), и соответственно все линии сигнала развертки будут выбраны. В это время аналоговые переключатели asw, предоставляемые для соответствующих линий сигнала данных, включают и соответственно Vcom подают во все линии сигнала данных. Кроме того, сигнал SB, подаваемый в каждый из каскадов, становится активным (Низким), и сигнал R, подаваемый в каждый из каскадов, также становится активным (Высоким), и соответственно сигнал Q триггера FF становится неактивным (Низким). Это связано с тем, что в триггере FF сигнал R (сброса) имеет приоритет и поэтому сигнал Q становится неактивным в случае, когда сигнал SB и сигнал R одновременно становятся активными. После окончания операции подготовки к отображению (то есть после того, как сигнал AONB становится неактивным), Vcom записывают во все пиксели FIX блока DAR дисплея, и сигнал Q, выводимый из триггера FF в каждом из каскадов сдвигового регистра, становится неактивным (Низким).

Кроме того, в сдвиговом регистре SR устройства 3c жидкокристаллического дисплея выполняют следующую операцию в каждый период вертикальной развертки (в котором отображают кадр). В частности, каждый каскад сдвигового регистра SR выполнен следующим образом. Когда сигнал SB, подаваемый в каскад сдвигового регистра SR, становится активным (= Низким), триггер FF каскада устанавливают и, соответственно сигнал Q становится высоким (активным). Это приводит к приему сигнала GCKB каскадом через аналоговый переключатель ASW4. Когда сигнал GCKB в каскаде становится активным (= Низким), сигнал OUTB каскада становится активным (Низким), и сигнал SB следующего каскада для данного каскада становится активным. Это приводит к тому, что в сигнал OUTB триггера FF следующего каскада для данного каскада становится активным и соответственно сигнал GCKB принимают в следующем каскаде для данного каскада. Когда сигнал GCKB в следующем каскаде для данного каскада становится активным (= Низким), триггер FF каскада сбрасывают, и соответственно сигнал Q становится низким (неактивным). Это приводит к тому, что аналоговый переключатель ASW3 включается. В это время сигнал AON является высоким, и соответственно оба входа в схеме AND каскада становятся высокими, и выход схемы AND становится высоким. Это приводит к высокому (неактивному) сигналу OUTB каскада.

Устройство 3c жидкокристаллического дисплея приводит к получению следующего эффекта, в дополнение к эффекту, аналогичному выполняемому устройством 3а жидкокристаллического дисплея. В частности, когда сигнал АОВ возвращается в неактивное состояние (то есть когда сдвиговый регистр возвращается из одновременного выбора всех линий сигнала развертки), сигнал SB и сигнал R, которые подают в триггер FF, оба возвращаются в неактивное состояние. В это время сигнал R возвращается в неактивное состояние после того, как сигнал SB возвращается в неактивное состояние, поскольку инвертор предусмотрен между выводом OUTB и выводом R. Это позволяет предотвратить нежелательную установку триггера FFa в активное состояние (поскольку сигнал SB возвращается в неактивное состояние после возврата сигнала R в неактивное состояние), когда сигнал АОВ возвращается в неактивное состояние.

i-ый каскад SRi сдвигового регистра SR устройства 3c жидкокристаллического дисплея также может быть выполнен, как показано на фиг.9. В конфигурации, показанной на фиг.9, i-ый каскад SRi сдвигового регистра включает в себя (i) триггер FF, имеющий вывод SB и вывод R, (ii) аналоговые переключатели ASW5 и ASW6, и (iii) вывод ONB, вывод СКВ и вывод OUTB. Вывод QB триггера FF соединен со стороной затвора n-канала аналогового переключателя ASW5 и стороной р-канала затвора аналогового переключателя ASW6. Вывод Q триггера FF соединен со стороной затвора р-канала аналогового переключателя ASW5 и стороной затвора n-канала аналогового переключателя ASW6. Вывод OUTB, который используется как выходной вывод для этого каскада, соединен с одним электропроводным электродом аналогового переключателя ASW5 и одним электропроводным электродом аналогового переключателя ASW6. Другой электропроводный электрод аналогового переключателя ASW5 соединен с выводом ONB. Другой электропроводный электрод аналогового переключателя ASW6 соединен с выводом СКВ, в который подают сигнал тактовой частоты.

В случае, когда i-ый каскад SRi сдвигового регистра выполнен так, как показано на фиг.9, в то время как сигнал AONB является активным (Низким) в течение заданного периода времени, сигнал AON выводят из вывода OUTB каждого из каскадов сдвигового регистра SR через аналоговый переключатель ASW5, и сигнал OUTB становится низким (активным). Это приводит к тому, что все линии сигнала развертки становятся выбранными. В это время аналоговые переключатели asw, предусмотренные для соответствующих линий сигнала данных, включают и соответственно Vcom прикладывают ко всем линиям сигнала данных. "Кроме того, сигнал SB, подаваемый в каждый из каскадов, становится активным (Низким), и сигнал R, подаваемый в каскад, также становится активным (Высоким) и соответственно сигнал Q триггера FF становится неактивным (Низким) (поэтому аналоговый переключатель ASW5 остается включенным). После окончания операции подготовки к отображению (то есть после того, как сигнал AONB становится неактивным), Vcom записывают во все пиксели PIX в блоке DAR дисплея, и сигналы Q, которые выводят из соответствующих триггеров FF, подаваемые в соответствующие каскады сдвигового регистра, становятся неактивными (Низкими).

Кроме того, в i-ом каскаде SRi, показанном на фиг.9, когда сигнал SB, подаваемый в каждый из каскадов, становится активным (= Низким) в каждый период вертикальной развертки, триггер FF каскада устанавливают, и, соответственно, сигнал Q становится высоким (активным). Это приводит к приему сигнала GCKB с помощью каскада через аналоговый переключатель ASW6. Когда сигнал GCKB в каскаде становится активным (= Низким), сигнал OUTB в каскаде становится активным (Низким) и сигнал SB в следующем каскаде этого каскада становится активным. Это приводит к тому, что сигнал OUTB триггера FF следующего каскада для данного каскада становится активным, и соответственно сигнал GCKB принимают с помощью следующего каскада для данного каскада. Когда сигнал GCKB в следующем каскаде данного каскада становится активным (= Низким), триггер FF для каскада сбрасывают и соответственно сигнал Q становится низким (неактивным). Это приводит к тому, что аналоговый переключатель ASW5 каскада включается. В это время сигнал AON является высоким и соответственно сигнал OUTB для данного каскада становится высоким (неактивным).

Каждый из каскадов сдвигового регистра, который выполнен, как показано на фиг.9, позволяет уменьшить размер сдвигового регистра, вызывая эффект, аналогичный сдвиговому регистру, показанному на фиг.2.

Вариант осуществления 2

На фиг.10 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3d жидкокристаллического дисплея, в соответствии с настоящим изобретением. Устройство 3d жидкокристаллического дисплея включает в себя блок DAR дисплея, схему GD управления затвором, схему SD управления истоком и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвора сигнал AONB (сигнал все включены), импульс GSP запуска затвора, сигнал GOE разрешения работы затвора и сигналы GCK1B и GCK2B тактовой частоты затвора. Кроме того, схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвором включает в себя сдвиговый регистр SR, имеющий множество каскадов. Ниже i-ый каскад (i=1,… n-1, n, n+1,…) сдвигового регистра кратко обозначается как "i-ый каскад SRi" в соответствующих случаях.

Выходной сигнал (OUT-сигнал) i-ого каскада SRi сдвигового регистра подают в линию Gi сигнала развертки блока DAR дисплея через буфер. Например, сигнал OUTB n-ого каскада SRn подают в линию Gn сигнала развертки через буфер. В блоке DAR дисплея линия Gn сигнала развертки соединена с затвором транзистора, который соединен с электродом пикселя в пикселе PDCn. Конденсатор удержания (вспомогательный конденсатор) сформирован с помощью электрода пикселя в пикселе PIXn и линии конденсатора CSn удержания.

Кроме того, один (1) аналоговый переключатель asw и один (1) инвертор предусмотрены для каждой линии сигнала данных. Инвертор имеет входной вывод, соединенный с линией AONB сигнала. Один электропроводный вывод аналогового переключателя asw соединен с концом линии сигнала данных, и другой электропроводный вывод аналогового переключателя asw соединен с Vcom (электрический потенциал общего электрода) источника питания. Затвор на стороне n-канала аналогового ключа asw соединен с выходным выводом инвертора, и затвор на стороне р-канала аналогового переключателя asw соединен с линией сигнала AONB.

На фиг.11 показана принципиальная схема, частично иллюстрирующая конкретную конфигурацию сдвигового регистра SR. Как показано на фиг.11, каждый каскад сдвигового регистра включает в себя (i) триггер FF, имеющий вывод SB и вывод RB, (и) два аналоговых переключателя ASW7 и ASW8 (схема затвора), (iii) схему 1 И-НЕ (логическую схему) и схему 2 И-НЕ (выходная схема), (iv) первый инвертор и второй инвертор, (v) вывод СКВ, (vi) вывод ONB и (vii) вывод OUT. Вывод QB триггера FF соединен с одним входным выводом схемы 1 И-НЕ, и выходной вывод схемы 1 И-НЕ соединен с входным выводом первого инвертора, с затвором на стороне р-канала аналогового переключателя ASW7 и затвором на стороне n-канала аналогового переключателя ASW8. Выходной вывод первого инвертора соединен с затвором на стороне n-канала аналогового переключателя ASW7 и затвором на стороне р-канала аналогового переключателя ASW8. Один электропроводный электрод аналогового переключателя ASW7 соединен с VDD, и один электропроводный электрод аналогового переключателя ASW8 соединен с выводом СКВ. Другой электропроводный электрод аналогового переключателя ASW7, другой электропроводный электрод аналогового переключателя ASW8 и один вх