Дифференциальный операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения. Техническим результатом является повышение стабильности выходного статического синфазного напряжения дифференциального операционного усилителя при нулевом входном синфазном сигнале. В усилитель введены третий и четвертый входные транзисторы, эмиттеры которых связаны с эмиттерами первого и второго входных транзисторов, причем база третьего входного транзистора соединена с базой первого входного транзистора, база четвертого входного транзистора соединена с базой второго входного транзистора, коллекторы третьего и четвертого входных транзисторов связаны с шиной второго источника питания, эмиттеры первого и второго входных транзисторов подключены к эмиттерам первого и второго дополнительных транзисторов, коллектор первого дополнительного транзистора соединен с коллектором первого входного транзистора, коллектор второго дополнительного транзистора соединен с коллектором второго входного транзистора, при этом первый вспомогательный выход устройства связан с базами первого и второго дополнительных транзисторов через первый резистор обратной связи, а второй вспомогательный выход устройства связан с базами первого и второго дополнительных транзисторов через второй резистор обратной связи. 1 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, фильтрах, компараторах т.п.).

Известны схемы классических двухкаскадных дифференциальных операционных усилителей (ДУ) [1-16] с парафазным выходом, которые стали основой многих серийных аналоговых микросхем.

ДУ данного класса активно применяются в структуре СВЧ-устройств, реализованных на базе SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи, драйверов дифференциальных линий связи между СФ-блоками и т.п. В значительной степени этому способствует простота установления статического режима ДУ при низковольтном питании (1,2÷2,1) В, которое характерно для SiGe транзисторов с предельными частотами 120÷500 ГГц.

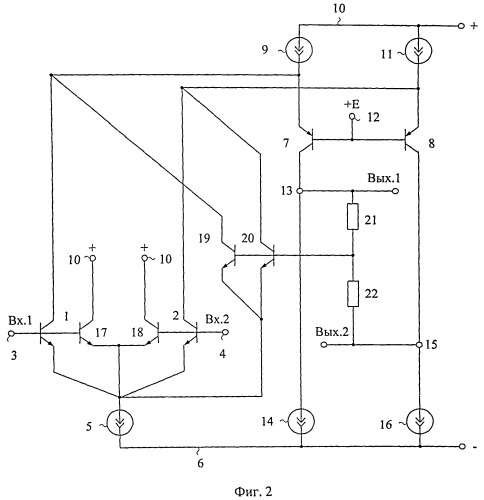

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель по патенту US 4.600.893, fig.4, содержащий первый 1 и второй 2 входные транзисторы, базы которых соединены с соответствующими входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттерами первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, эмиттер первого 7 выходного транзистора соединен с коллектором первого 1 входного транзистора и через второй 9 токостабилизирующий двухполюсник соединен с шиной второй 10 источника питания, эмиттер второго 8 выходного транзистора соединен с коллектором второго 2 входного транзистора и через третий 11 токостабилизирующий двухполюсник соединен с шиной второго 10 источника питания, базы первого 7 и второго 8 выходных транзисторов объединены и подключены к источнику напряжения смещения потенциалов 12, коллектор первого 7 выходного транзистора соединен с первым 13 вспомогательным выходом устройства и через первый 14 двухполюсник коллекторной нагрузки подключен к шине первого 6 источника питания, коллектор второго 8 выходного транзистора соединен со вторым 15 вспомогательным выходом устройства и через второй 16 двухполюсник нагрузки подключен к шине первого 6 источника питания.

Существенный недостаток известного ДУ состоит в том, что он имеет нестабильный уровень выходного синфазного напряжения, зависящий от параметров двухполюсников коллекторной нагрузки 14 и 15. Это значительно затрудняет его согласование с последующими функциональными узлами многокаскадных интерфейсных СФ-блоков и IP-модулей.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ДУ при нулевом входном синфазном сигнале будет иметь высокую стабильность и нулевое значение.

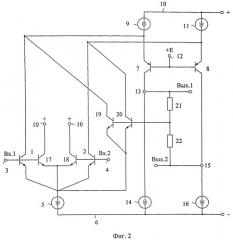

Поставленная задача решается тем, что в дифференциальном операционном усилителе с парафазным выходом, фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых соединены с соответствующими входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, эмиттер первого 7 выходного транзистора соединен с коллектором первого 1 входного транзистора и через второй 9 токостабилизирующий двухполюсник соединен с шиной второй 10 источника питания, эмиттер второго 8 выходного транзистора соединен с коллектором второго 2 входного транзистора и через третий 11 токостабилизирующий двухполюсник соединен с шиной второго 10 источника питания, базы первого 7 и второго 8 выходных транзисторов объединены и подключены к источнику напряжения смещения потенциалов 12, коллектор первого 7 выходного транзистора соединен с первым 13 вспомогательным выходом устройства и через первый 14 двухполюсник коллекторной нагрузки подключен к шине первого 6 источника питания, коллектор второго 8 выходного транзистора соединен со вторым 15 вспомогательным выходом устройства и через второй 16 двухполюсник нагрузки подключен к шине первого 6 источника питания, предусмотрены новые элементы и связи - в схему введены третий 17 и четвертый 18 входные транзисторы, эмиттеры которых связаны с эмиттерами первого 1 и второго 2 входных транзисторов, база третьего 17 входного транзистора соединена с базой первого 1 входного транзистора, база четвертого 18 входного транзистора соединена с базой второго 2 входного транзистора, коллекторы третьего 17 и четвертого 18 входных транзисторов связаны с шиной второго 10 источника питания, эмиттеры первого 1 и второго 2 входных транзисторов подключены к эмиттерам первого 19 и второго 20 дополнительных транзисторов, коллектор первого 19 дополнительного транзистора соединен с коллектором первого 1 входного транзистора, коллектор второго 20 дополнительного транзистора соединен с коллектором второго 2 входного транзистора, причем первый 13 вспомогательный выход устройства связан с базами первого 19 и второго 20 дополнительных транзисторов через первый 21 резистор обратной связи, а второй 15 вспомогательный выход устройства связан с базами первого 19 и второго 20 дополнительных транзисторов через второй 22 резистор обратной связи.

На фиг.1 показана схема ДУ-прототипа.

На фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения.

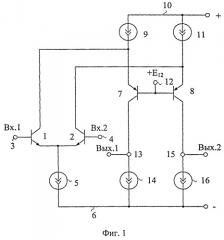

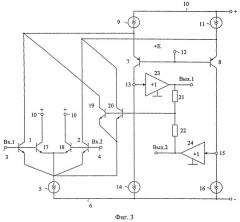

Схема ДУ по п.2 формулы изобретения приведена на фиг.3.

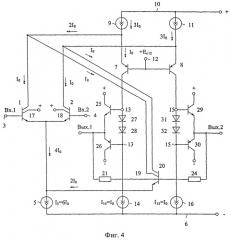

На фиг.4 приведена схема ДУ фиг.3 с конкретным выполнением буферных усилителей.

На фиг.5 показана схема заявляемого ДУ фиг.4 в среде компьютерного моделирования Pspice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.6 - зависимость его коэффициента усиления по напряжению от частоты.

На фиг.7 представлена зависимость выходных напряжений ДУ фиг.5 от входного синусоидального напряжения (uвх = 30 мВ). Графики фиг.7 показывают, что заявляемый ДУ имеет два противофазных выходных напряжения и нулевой уровень выходного синфазного статического напряжения.

Дифференциальный операционный усилитель с парафазным выходом, фиг.2, содержит первый 1 и второй 2 входные транзисторы, базы которых соединены с соответствующими входами 3 и 4 устройства, первый 5 токостабилизирующий двухполюсник, включенный между объединенным эмиттерами первого 1 и второго 2 входных транзисторов и шиной первого 6 источника питания, первый 7 и второй 8 выходные транзисторы, эмиттер первого 7 выходного транзистора соединен с коллектором первого 1 входного транзистора и через второй 9 токостабилизирующий двухполюсник соединен с шиной второй 10 источника питания, эмиттер второго 8 выходного транзистора соединен с коллектором второго 2 входного транзистора и через третий 11 токостабилизирующий двухполюсник соединен с шиной второго 10 источника питания, базы первого 7 и второго 8 выходных транзисторов объединены и подключены к источнику напряжения смещения потенциалов 12, коллектор первого 7 выходного транзистора соединен с первым 13 вспомогательным выходом устройства и через первый 14 двухполюсник коллекторной нагрузки подключен к шине первого 6 источника питания, коллектор второго 8 выходного транзистора соединен со вторым 15 вспомогательным выходом устройства и через второй 16 двухполюсник нагрузки подключен к шине первого 6 источника питания. В схему введены третий 17 и четвертый 18 входные транзисторы, эмиттеры которых связаны с эмиттерами первого 1 и второго 2 входных транзисторов, база третьего 17 входного транзистора соединена с базой первого 1 входного транзистора, база четвертого 18 входного транзистора соединена с базой второго 2 входного транзистора, коллекторы третьего 17 и четвертого 18 входных транзисторов связаны с шиной второго 10 источника питания, эмиттеры первого 1 и второго 2 входных транзисторов подключены к эмиттерам первого 19 и второго 20 дополнительных транзисторов, коллектор первого 19 дополнительного транзистора соединен с коллектором первого 1 входного транзистора, коллектор второго 20 дополнительного транзистора соединен с коллектором второго 2 входного транзистора, причем первый 13 вспомогательный выход устройства связан с базами первого 19 и второго 20 дополнительных транзисторов через первый 21 резистор обратной связи, а второй 15 вспомогательный выход устройства связан с базами первого 19 и второго 20 дополнительных транзисторов через второй 22 резистор обратной связи.

На фиг.3 в соответствии с п.2 формулы изобретения первый 13 вспомогательный выход устройства связан с базами первого 19 и второго 20 дополнительных транзисторов через последовательно соединенные первый 23 дополнительный буферный усилитель и первый 21 резистор обратной связи, а второй 15 вспомогательный выход устройства связан с базой первого 19 и второго 20 дополнительных транзисторов через последовательно соединенные второй 24 дополнительный буферный усилитель и второй 22 резистор обратной связи.

На фиг.4 буферные усилители 23 и 24 реализованы соответственно на транзисторах 25, 26, р-n переходах 27, 28, а также транзисторах 29, 30 и р-n переходах 31, 32.

Рассмотрим работу ДУ фиг.2.

Статический режим по току транзисторов предлагаемого ДУ устанавливается двухполюсниками 5, 9, 11, 14, 16.

Статические напряжения U13=U15 на выходах Вых.1 и Вых.2 ДУ при нулевом входном сигнале (uвх=0) можно найти из уравнения:

U 13 = I б R 21 − U э б .19 + U э б .1 ≈ I б R 21 ≈ 0 U 15 = I б R 22 − U э б .20 + U э б .2 ≈ I б R 22 ≈ 0

где Uэб.1 = Uэб.19, Uэб.2 = Uэб.20 - напряжение «эмиттер-база» транзисторов 1, 2, 19 и 20;

I б I б . Σ 2 - составляющая суммарного тока баз транзисторов 19 и

20 в резисторе обратной связи 21 (22).

Таким образом, при типовых значениях токов базы транзисторов 19, 20, а также при R21=R22=500÷1000 Ом выходное синфазное напряжение ДУ фиг.2 практически равно нулю в широком диапазоне температурных и радиационных воздействий, а также изменений напряжений питания. Это весьма существенно для согласования заявляемого ДУ с последующими функциональными узлами радиоэлектронной аппаратуры, а также его использования в мостовых усилителях мощности.

Таким образом, предлагаемый ДУ имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4.406.990, fig.3.

2. Патент US 4.600.893, fig.4.

3. Патент US 5.684.419.

4. Патент US 3.979.689.

5. Патент US Re 30.587.

6. Патент US 5.684.419.

7. Патент US 4.151.483, fig.4.

8. Патент US 4.151.484, fig.4.

9. Патент US 4.406.990.

10. Патент US 5.557.238, fig.5.

11. Патент US 6.580.325, fig.26.

12. Патент US 3.733.559.

13. Патент US 5.376.897.

14. Патент 3.079.689 15.

15. Патент ЕР 0144647.

16. Патент JP 60090407.

1. Дифференциальный операционный усилитель с парафазным выходом, содержащий первый (1) и второй (2) входные транзисторы, базы которых соединены с соответствующими входами (3) и (4) устройства, первый (5) токостабилизирующий двухполюсник, включенный между объединенным эмиттерами первого (1) и второго (2) входных транзисторов и шиной первого (6) источника питания, первый (7) и второй (8) выходные транзисторы, эмиттер первого (7) выходного транзистора соединен с коллектором первого (1) входного транзистора и через второй (9) токостабилизирующий двухполюсник соединен с шиной второй (10) источника питания, эмиттер второго (8) выходного транзистора соединен с коллектором второго (2) входного транзистора и через третий (11) токостабилизирующий двухполюсник соединен с шиной второго (10) источника питания, базы первого (7) и второго (8) выходных транзисторов объединены и подключены к источнику напряжения смещения потенциалов (12), коллектор первого (7) выходного транзистора соединен с первым (13) вспомогательным выходом устройства и через первый (14) двухполюсник коллекторной нагрузки подключен к шине первого (6) источника питания, коллектор второго (8) выходного транзистора соединен со вторым (15) вспомогательным выходом устройства и через второй (16) двухполюсник нагрузки подключен к шине первого (6) источника питания, отличающийся тем, что в схему введены третий (17) и четвертый (18) входные транзисторы, эмиттеры которых связаны с эмиттерами первого (1) и второго (2) входных транзисторов, база третьего (17) входного транзистора соединена с базой первого (1) входного транзистора, база четвертого (18) входного транзистора соединена с базой второго (2) входного транзистора, коллекторы третьего (17) и четвертого (18) входных транзисторов связаны с шиной второго (10) источника питания, эмиттеры первого (1) и второго (2) входных транзисторов подключены к эмиттерам первого (19) и второго (20) дополнительных транзисторов, коллектор первого (19) дополнительного транзистора соединен с коллектором первого (1) входного транзистора, коллектор второго (20) дополнительного транзистора соединен с коллектором второго (2) входного транзистора, причем первый (13) вспомогательный выход устройства связан с базами первого (19) и второго (20) дополнительных транзисторов через первый (21) резистор обратной связи, а второй (15) вспомогательный выход устройства связан с базами первого (19) и второго (20) дополнительных транзисторов через второй (22) резистор обратной связи.

2. Дифференциальный операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (13) вспомогательный выход устройства связан с базами первого (19) и второго (20) дополнительных транзисторов через последовательно соединенные первый (23) дополнительный буферный усилитель и первый (21) резистор обратной связи, а второй (15) вспомогательный выход устройства связан с базой первого (19) и второго (20) дополнительных транзисторов через последовательно соединенные второй (24) дополнительный буферный усилитель и второй (22) резистор обратной связи.