Мутильдифференциальный операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых интерфейсов, аналого-цифровых преобразователях, RC-фильтрах, инструментальных усилителях и т.п. Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов МОУ, а также расширении диапазона рабочих частот, снижении температурного дрейфа ЭДС смещения нуля, увеличении входных граничных напряжений. Мультидифференциальный операционный усилитель содержит входной дифференциальный преобразователь «напряжение-ток», противофазные токовые выходы, двухполюсники нагрузки, шины источников питания, токовые выходы устройства, входные транзисторы, эмиттер входного транзистора, источники питания, источники опорного тока, масштабирующие резисторы, источники опорного тока выполнены в виде управляемых источников опорного тока с соответствующими управляющими входами, которые подключены к выходу каскада выделения выходного синфазного напряжения входного дифференциального преобразователя «напряжение-ток», причем входы каскада выделения выходного синфазного напряжения входного дифференциального преобразователя «напряжение-ток» соединены с соответствующими противофазными токовыми выходами входного дифференциального преобразователя «напряжение-ток». 3 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых интерфейсов, аналого-цифровых преобразователях, RC-фильтрах, инструментальных усилителях и т.п.

Известны схемы так называемых мультидифференциальных операционных усилителей (МОУ), имеющих несколько входов и общую выходную подсхему - буферный каскад [1-8]. В связи с малым энергопореблением МОУ стали основой многих микроэлектронных устройств нового поколения [1-8].

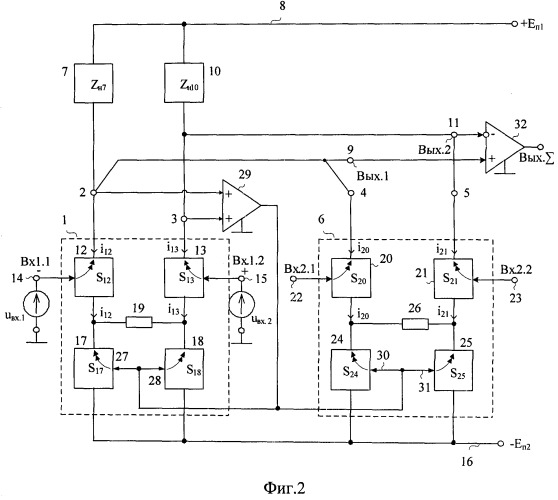

Ближайшим прототипом заявляемого устройства (фиг.1) является мультидифференциальный операционный усилитель, описанный в патенте US №4835488, fig.3. Он содержит первый 1 входной дифференциальный преобразователь «напряжение-ток», первый 2 и второй 3 противофазные токовые выходы которого соединены с соответствующими первым 4 и вторым 5 противофазными токовыми выходами второго 6 входного дифференциального преобразователя «напряжение-ток», первый 7 двухполюсник нагрузки, включенный между первой 8 шиной источника питания и первым 2 токовым выходом первого 1 входного дифференциального преобразователя «напряжение-ток», соединенным с первым 9 выходом устройства, второй 10 двухполюсник нагрузки, второй 11 выход устройства, причем первый 1 входной дифференциальный преобразователь «напряжение-ток» включает первый 12 и второй 13 входные транзисторы, базы которых соединены с первой группой 14, 15 соответствующих противофазных входов 14, 15 устройства, эмиттер первого 12 входного транзистора связан со второй 16 шиной источника питания через первый 17 источник опорного тока, эмиттер второго 13 входного транзистора связан со второй 16 шиной источника питания через второй 18 источник опорного тока, между эмиттерами первого 12 и второго 13 входных транзисторов включен первый 19 масштабирующий резистор, причем второй 6 входной дифференциальный преобразователь «напряжение-ток» включает второй 10 двухполюсник нагрузки, включенный между первой 8 шиной источника питания и вторым 3 токовым выходом первого 1 входного дифференциального преобразователя «напряжение-ток», соединенным со вторым 5 токовым выходом второго 6 входного дифференциального преобразователя «напряжение-ток» и вторым 11 выходом устройства, причем второй 6 входной дифференциальный преобразователь «напряжение-ток» включает третий 20 и четвертый 21 входные транзисторы, базы которых соединены со второй группой (22, 23) противофазных входов 22, 23 устройства, эмиттер третьего 20 входного транзистора связан со второй 16 шиной источника питания через третий 24 источник опорного тока, эмиттер четвертого 21 входного транзистора связан со второй 16 шиной источника питания через четвертый 25 источник опорного тока, между эмиттерами третьего 20 и четвертого 21 входных транзисторов включен второй 26 масштабирующий резистор.

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет сравнительно невысокое ослабление входных синфазных сигналов, что отрицательно сказывается на точностных параметрах аналоговых интерфейсов на его основе.

Основная задача предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов МОУ, а также расширении диапазона рабочих частот, снижении температурного дрейфа ЭДС смещения нуля, увеличении входных граничных напряжений.

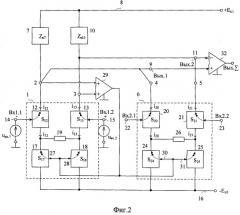

Поставленная задача достигается тем, что в мультидифференциальном операционном усилителе фиг.1, содержащем первый 1 входной дифференциальный преобразователь «напряжение-ток», первый 2 и второй 3 противофазные токовые выходы которого соединены с соответствующими первым 4 и вторым 5 противофазными токовыми выходами второго 6 входного дифференциального преобразователя «напряжение-ток», первый 7 двухполюсник нагрузки, включенный между первой 8 шиной источника питания и первым 2 токовым выходом первого 1 входного дифференциального преобразователя «напряжение-ток», соединенным с первым 9 выходом устройства, второй 10 двухполюсник нагрузки, второй 11 выход устройства, причем первый 1 входной дифференциальный преобразователь «напряжение-ток» включает первый 12 и второй 13 входные транзисторы, базы которых соединены с первой группой 14, 15 соответствующих противофазных входов 14, 15 устройства, эмиттер первого 12 входного транзистора связан со второй 16 шиной источника питания через первый 17 источник опорного тока, эмиттер второго 13 входного транзистора связан со второй 16 шиной источника питания через второй 18 источник опорного тока, между эмиттерами первого 12 и второго 13 входных транзисторов включен первый 19 масштабирующий резистор, причем второй 6 входной дифференциальный преобразователь «напряжение-ток» включает второй 10 двухполюсник нагрузки, включенный между первой 8 шиной источника питания и вторым 3 токовым выходом первого 1 входного дифференциального преобразователя «напряжение-ток», соединенным со вторым 5 токовым выходом второго 6 входного дифференциального преобразователя «напряжение-ток» и вторым 11 выходом устройства, причем второй 6 входной дифференциальный преобразователь «напряжение-ток» включает третий 20 и четвертый 21 входные транзисторы, базы которых соединены со второй группой (22, 23) противофазных входов 22, 23 устройства, эмиттер третьего 20 входного транзистора связан со второй 16 шиной источника питания через третий 24 источник опорного тока, эмиттер четвертого 21 входного транзистора связан со второй 16 шиной источника питания через четвертый 25 источник опорного тока, между эмиттерами третьего 20 и четвертого 21 входных транзисторов включен второй 26 масштабирующий резистор, предусмотрены новые элементы и связи первый 17 и второй 18 источники опорного тока выполнены в виде управляемых источников опорного тока с соответствующими управляющими входами 27 и 28, которые подключены к выходу каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток», причем входы каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток» соединены с соответствующими первым 2 и вторым 3 противофазными токовыми выходами первого 1 входного дифференциального преобразователя «напряжение-ток».

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показан заявляемый МОУ в соответствии с пп.1-4 формулы изобретения.

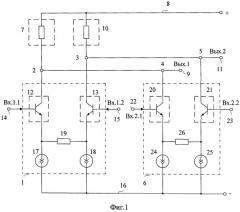

На фиг.3 представлена принципиальная схема заявляемого устройства на КМОП транзисторах.

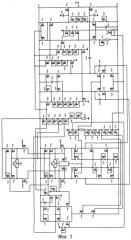

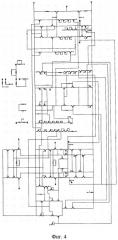

Схема исследованного авторами МОУ (фиг.2) в среде компьютерного моделирования Cadance Virtuoso на моделях SiGe транзисторов представлена на фиг.4.

На фиг.5 приведена частотная зависимость коэффициента передачи синфазного напряжения МОУ фиг.4 при единичном дифференциальном коэффициенте усиления.

На фиг.6 показаны графики для определения граничных напряжений входного синфазного сигнала МОУ фиг.4, в пределах которых обеспечивается высокий уровень ослабления входных синфазных напряжений.

На фиг.7 представлена амплитудно-частотная характеристика МОУ (фиг.4), а на фиг.8 - его фазо-частотная характеристика.

На фиг.9 приведена амплитудно-частотная характеристика МОУ фиг.4 в режиме неинвертирующего повторителя напряжения.

На фиг.10 показаны графики для определения максимальной скорости нарастания выходного напряжения МОУ фиг.4, а на фиг.11 - его амплитудная характеристика.

На фиг.12 приведена температурная зависимость ЭДС смещения МОУ (фиг.4).

Мультидифференциальный операционный усилитель фиг.2 содержит первый 1 входной дифференциальный преобразователь «напряжение-ток», первый 2 и второй 3 противофазные токовые выходы которого соединены с соответствующими первым 4 и вторым 5 противофазными токовыми выходами второго 6 входного дифференциального преобразователя «напряжение-ток», первый 7 двухполюсник нагрузки, включенный между первой 8 шиной источника питания и первым 2 токовым выходом первого 1 входного дифференциального преобразователя «напряжение-ток», соединенным с первым 9 выходом устройства, второй 10 двухполюсник нагрузки, второй 11 выход устройства, причем первый 1 входной дифференциальный преобразователь «напряжение-ток» включает первый 12 и второй 13 входные транзисторы, базы которых соединены с первой группой 14, 15 соответствующих противофазных входов 14, 15 устройства, эмиттер первого 12 входного транзистора связан со второй 16 шиной источника питания через первый 17 источник опорного тока, эмиттер второго 13 входного транзистора связан со второй 16 шиной источника питания через второй 18 источник опорного тока, между эмиттерами первого 12 и второго 13 входных транзисторов включен первый 19 масштабирующий резистор, причем второй 6 входной дифференциальный преобразователь «напряжение-ток» включает второй 10 двухполюсник нагрузки, включенный между первой 8 шиной источника питания и вторым 3 токовым выходом первого 1 входного дифференциального преобразователя «напряжение-ток», соединенным со вторым 5 токовым выходом второго 6 входного дифференциального преобразователя «напряжение-ток» и вторым 11 выходом устройства, причем второй 6 входной дифференциальный преобразователь «напряжение-ток» включает третий 20 и четвертый 21 входные транзисторы, базы которых соединены со второй группой (22, 23) противофазных входов 22, 23 устройства, эмиттер третьего 20 входного транзистора связан со второй 16 шиной источника питания через третий 24 источник опорного тока, эмиттер четвертого 21 входного транзистора связан со второй 16 шиной источника питания через четвертый 25 источник опорного тока, между эмиттерами третьего 20 и четвертого 21 входных транзисторов включен второй 26 масштабирующий резистор. Для достижения поставленной цели первый 17 и второй 18 источники опорного тока выполнены в виде управляемых источников опорного тока с соответствующими управляющими входами 27 и 28, которые подключены к выходу каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток», причем входы каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток» соединены с соответствующими первым 2 и вторым 3 противофазными токовыми выходами первого 1 входного дифференциального преобразователя «напряжение-ток».

На фиг.2 в соответствии с п.2 формулы изобретения третий 24 и четвертый 25 источники опорного тока второго 6 входного дифференциального преобразователя «напряжение-ток» выполнены в виде управляемых источников опорного тока с соответствующими управляющими входами 30 и 31, которые подключены к выходу каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток».

Кроме того, на фиг.2 в соответствии с п.3 формулы изобретения в качестве первого 12, второго 13, третьего 20 и четвертого 21 входных транзисторов используются составные транзисторы в виде полевых транзисторов, истоки которых соответствуют эмиттерам, стоки - коллекторам, а затворы - базам биполярных транзисторов.

На фиг.2 в соответствии с п.4 формулы изобретения выходы 11 и 9 устройства также связаны со входами дополнительного дифференциального буферного каскада 32.

Рассмотрим работу мультидифференциального операционного усилителя (МОУ) фиг.2.

Входные сигналы, содержащие синфазную и дифференциальную составляющие, подаются на базу первого 12 входного транзистора и базу второго 13 входного транзистора. При этом возникают приращения токов i12, i13, причем за счет использования первого 19 масштабирующего резистора, подключенного между выходами первого 17 и второго 18 источников опорного тока, происходит частичное вычитание синфазных и суммирование дифференциальных составляющих приращений токов i12, i13, вследствие чего на первом 7 и втором 10 двухполюсниках нагрузки возникают падения напряжений суммированных дифференциальных и оставшихся после частичного вычитания синфазных составляющих приращений токов i12, i13.

Наличие каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток» позволяет создать два контура отрицательной обратной связи:

1. Первый контур. «Первый 2 выход первого 1 входного дифференциального преобразователя «напряжение-ток» - выход каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток» - управляющий вход 27 первого 17 опорного источника тока - выход первого 17 опорного источника тока - эмиттер первого 12 входного транзистора - коллектор первого 12 входного транзистора»;

2. Второй контур. «Второй 3 выход первого 1 входного дифференциального преобразователя «напряжение-ток» - выход каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток» - управляющий вход 28 второго 18 опорного источника тока - выход второго 18 опорного источника тока - эмиттер второго 13 входного транзистора - коллектор второго 13 входного транзистора».

Эти контуры отрицательной обратной связи обеспечивают дополнительное подавление синфазных составляющих вследствие их суммирования на каскаде 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток».

При этом указанные контуры не влияют на дифференциальные (противофазные) составляющие падений напряжений на первом 7 и втором 10 двухполюсниках нагрузок вследствие нулевого результата при их суммировании каскадом 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток».

Аналогично описанному принципу функционирования первого 1 входного дифференциального преобразователя «напряжение-ток» с первым 7 и вторым 10 двухполюсниками нагрузок и каскадом 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток» функционирует второй 6 входной дифференциальный преобразователь «напряжение-ток».

После этого происходит дополнительное усиление дифференциальных и ослабление синфазных составляющих напряжений на первом 7 и втором 10 двухполюсниках нагрузок с помощью дополнительного дифференциального буферного каскада 32, выход которого является выходом МОУ.

Анализ схемы позволяет определить коэффициенты передачи по каждому из каналов МОУ

K 1 + ( j ω ) = u В ы х . ∑ ( j ω ) u 15 ( j ω ) = − K 1 − = − u В ы х . ∑ ( j ω ) u 14 ( j ω ) = ( S э 12 ( j ω ) Z н 7 + S э 13 ( j ω ) Z н 10 ) K ( j ω ) , ( 1 )

K 2 + ( j ω ) = u В ы х . ∑ ( j ω ) u 23 ( j ω ) = − K 2 − = − u В ы х . ∑ ( j ω ) u 22 ( j ω ) = ( S э 20 ( j ω ) Z н 7 + S э 21 ( j ω ) Z н 10 ) K ( j ω ) . ( 2 )

Здесь Sэi(jω) - эквивалентная крутизна i-го транзистора

S э 12 ( j ω ) = S 12 ( j ω ) 1 + S 12 ( j ω ) / S 13 ( j ω ) + S 12 ( j ω ) R 19 ≈ 1 R 19 , ( 3 )

S э 13 ( j ω ) = S 13 ( j ω ) 1 + S 13 ( j ω ) / S 12 ( j ω ) + S 13 ( j ω ) R 19 ≈ 1 R 19 , ( 4 )

S э 20 ( j ω ) = S 20 ( j ω ) 1 + S 20 ( j ω ) / S 21 ( j ω ) + S 20 ( j ω ) R 26 ≈ 1 R 26 , ( 5 )

S э 21 ( j ω ) = S 21 ( j ω ) 1 + S 21 ( j ω ) / S 20 ( j ω ) + S 21 ( j ω ) R 26 ≈ 1 R 26 . ( 6 )

где Si - крутизна i-го транзистора, Rj - сопротивление j-гo масштабирующего резистора схемы, К - дифференциальный коэффициент усиления дополнительного дифференциального буферного каскада 32.

При этом коэффициенты ослабления входного синфазного напряжения первого 1 и второго 6 входных дифференциальных преобразователей «напряжение-ток» соответственно определяются выражениями

K о с с н 1 = ( 1 1 + S 13 R i 17 1 + R i 17 ( S 17 + S 24 ) K c − 1 1 + S 12 R i 18 1 + R i 18 ( S 18 + S 25 ) K с ) − 1 , ( 7 )

K о с с н 2 = ( 1 1 + S 21 R i 24 1 + R i 24 ( S 24 + S 17 ) K с − 1 1 + S 20 R i 25 1 + R i 25 ( S 25 + S 18 ) K с ) − 1 , ( 8 )

где Rij - выходное дифференциальное сопротивление j-гo транзистора или опорного источника тока (17, 18, 24, 25), Kc - коэффициент усиления по напряжению каскада 29 выделения выходного синфазного напряжения первого 1 входного дифференциального преобразователя «напряжение-ток».

Если Ri17(S17+S24)KC>>1, Ri18(S18+S25)Kc>>1 и Ri24(S24+S17)KC>>1, Ri25(S25+S18)KC>>1,то можно найти, что:

K о с с н 1 = ( 1 1 + S 13 ( S 17 + S 24 ) K C − 1 1 + S 12 ( S 18 + S 25 ) K C ) − 1 . ( 9 )

K о с с н 2 = ( 1 1 + S 21 ( S 24 + S 17 ) K C − 1 1 + S 20 ( S 25 + S 18 ) K C ) − 1 . ( 10 )

Таким образом, в МОУ фиг.2 коэффициенты KОССН1, KОССН2

минимизируются глубиною вводимой в схему обратной связи (KC) без изменения дифференциальных коэффициентов передачи каналов (1) и (2). Особенностью настоящей схемы является жесткая корреляция коэффициентов усиления отдельных каналов преобразования входного дифференциального сигнала

K 1 + K 2 + = K 1 − K 2 − = R 26 R 19 . ( 11 )

Поэтому использование этого МОУ в устройствах с обратной связью

обеспечивает через R19 и R26 необходимую корреляцию и согласование локальных передаточных функций сложных электрических схем.

Как видно из (1), (2) увеличение ZH7, ZH10 и симметричность каналов позволяет уменьшить влияние разности граничных напряжений активных элементов схемы. В частности, дрейф нуля усилителя в разомкнутом состоянии МОУ определяется выражением

U д р = U д р 1 K , ( 12 )

где Uдр1 - дрейф нуля входного двухканального дифференциального каскада МОУ, K - дифференциальный коэффициент усиления дополнительного дифференциального буферного каскада 32.

Кроме этого граничные напряжения входных цепей МОУ, в пределах которых обеспечивается их линейный диапазон работы, увеличиваются за счет применения указанных масштабирующих резисторов (R19, R26). Это и приводит к увеличению скорости нарастания выходного напряжения МОУ, а также стабилизирует режимы работы входных транзисторов 12, 13, 20 и 21. Действительно, граничные напряжения первого 1 и второго 6 входных дифференциальных преобразователей «напряжение-ток» соответственно определяются следующими выражениями

U г р 1 ≈ U г р .12 * + U г р .13 * + R 19 I 0 , ( 13 )

U г р 6 ≈ U г р .20 * + U г р .21 * + R 26 I 0 , ( 14 )

где I0=I17=I18=I24=I25 - статические токи источников опорного тока 17, 18, 24, 25.

U г р . i * - граничное входное напряжение i-го транзистора ( U г р . i * ≈ 25 м В ) .

Увеличение граничных напряжений (13) и (14) за счет резисторов R19 и R26 уменьшает влияние погрешности изготовления входных преобразователей транзисторов 12, 13; 20, 21 на токи эквивалентных нагрузок и, следовательно, дрейф нуля. Как видно из формул

i 12, ( 13 ) ( Δ U * ) = S 12, ( 13 ) Δ U * 1 + S 12, ( 13 ) R 19 + S 12, ( 13 ) / S 13, ( 12 ) ( 15 )

i 20, ( 21 ) ( Δ U * ) = S 20, ( 21 ) Δ U * 1 + S 20, ( 21 ) R 19 + S 20, ( 21 ) / S 21, ( 20 ) , ( 16 )

где ΔU∗ - технологическая разность граничных напряжений входных преобразователей, это приводит к повышению стабильности режимов работы активных элементов входных цепей МОУ.

Результаты компьютерного моделирования МОУ, представленные на графиках фиг.5-12? подтверждают, что заявляемое устройство имеет более высокие значения коэффициента ослабления входных синфазных сигналов и характеризуется улучшенными значениями других параметров.

Предлагаемый МОУ может использоваться в структуре широкополосных интерфейсов, датчиковых и измерительных систем.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4835488, fig.3.

2. Патентная заявка US 2008/0064359, fig.4.

3. Патент US 7205799, fig.4.

4. Патентная заявка WO 2007/022705.

5. Патент US 7271647.

6. Патент ФРГ 2146418.

7. Патентная заявка US 2003/0084377.

8. Патент US 5045804, fig.2.

1. Мультидифференциальный операционный усилитель, содержащий первый (1) входной дифференциальный преобразователь «напряжение-ток», первый (2) и второй (3) противофазные токовые выходы которого соединены с соответствующими первым (4) и вторым (5) противофазными токовыми выходами второго (6) входного дифференциального преобразователя «напряжение-ток», первый (7) двухполюсник нагрузки, включенный между первой (8) шиной источника питания и первым (2) токовым выходом первого (1) входного дифференциального преобразователя «напряжение-ток», соединенным с первым (9) выходом устройства, второй (10) двухполюсник нагрузки, второй (11) выход устройства, причем первый (1) входной дифференциальный преобразователь «напряжение-ток» включает первый (12) и второй (13) входные транзисторы, базы которых соединены с первой группой (14), (15) соответствующих противофазных входов (14), (15) устройства, эмиттер первого (12) входного транзистора связан со второй (16) шиной источника питания через первый (17) источник опорного тока, эмиттер второго (13) входного транзистора связан со второй (16) шиной источника питания через второй (18) источник опорного тока, между эмиттерами первого (12) и второго (13) входных транзисторов включен первый (19) масштабирующий резистор, причем второй (6) входной дифференциальный преобразователь «напряжение-ток» включает второй (10) двухполюсник нагрузки, включенный между первой (8) шиной источника питания и вторым (3) токовым выходом первого (1) входного дифференциального преобразователя «напряжение-ток», соединенным со вторым (5) токовым выходом второго (6) входного дифференциального преобразователя «напряжение-ток» и вторым (11) выходом устройства, причем второй (6) входной дифференциальный преобразователь «напряжение-ток» включает третий (20) и четвертый (21) входные транзисторы, базы которых соединены со второй группой (22, 23) противофазных входов (22), (23) устройства, эмиттер третьего (20) входного транзистора связан со второй (16) шиной источника питания через третий (24) источник опорного тока, эмиттер четвертого (21) входного транзистора связан со второй (16) шиной источника питания через четвертый (25) источник опорного тока, между эмиттерами третьего (20) и четвертого (21) входных транзисторов включен второй (26) масштабирующий резистор, отличающийся тем, что первый (17) и второй (18) источники опорного тока выполнены в виде управляемых источников опорного тока с соответствующими управляющими входами (27) и (28), которые подключены к выходу каскада (29) выделения выходного синфазного напряжения первого (1) входного дифференциального преобразователя «напряжение-ток», причем входы каскада (29) выделения выходного синфазного напряжения первого (1) входного дифференциального преобразователя «напряжение-ток» соединены с соответствующими первым (2) и вторым (3) противофазными токовыми выходами первого (1) входного дифференциального преобразователя «напряжение-ток».

2. Мультидифференциальный операционный усилитель по п.1, отличающийся тем, что третий (24) и четвертый (25) источники опорного тока второго (6) входного дифференциального преобразователя «напряжение-ток» выполнены в виде управляемых источников опорного тока с соответствующими управляющими входами (30) и (31), которые подключены к выходу каскада (29) выделения выходного синфазного напряжения первого (1) входного дифференциального преобразователя «напряжение-ток».

3. Мультидифференциальный операционный усилитель по п.1, отличающийся тем, что в качестве первого (12), второго (13), третьего (20) и четвертого (21) входных транзисторов используются составные транзисторы в виде полевых транзисторов, истоки которых соответствуют эмиттерам, стоки - коллекторам, а затворы - базам биполярных транзисторов.

4. Мультидифференциальный операционный усилитель по п.1 или 2, отличающийся тем, что выходы (11) и (9) устройства связаны со входами дополнительного дифференциального буферного каскада (32).