Цифровой функциональный преобразователь

Иллюстрации

Показать всеИзобретение относится к цифровой вычислительной и информационной технике и может быть использовано для первичной обработки данных в автоматизированных системах научных исследований. Технический результат заключается в реализации логарифмической зависимости при цифровом преобразовании экспериментальных данных и снижении вдвое абсолютной погрешности преобразования. Цифровой функциональный преобразователь состоит из накапливающего сумматора-вычитателя, первого и второго регистров, блока управления. В него дополнительно введены двоичный счетчик, два блока элементов И, блок элементов ИЛИ и блок формирования параллельного кода функции из унитарного кода, чтобы реализовать разностно-итерационный принцип слежения за оценочной функцией, значение которой определяется в накапливающем сумматоре-вычислителе и корректируется на каждом такте интерполяции логарифмической кривой путем подсуммирования (или вычитания) содержимого двоичного счетчика (или регистра) в зависимости от знака сумматора-вычислителя. При этом значение двоичного счетчика увеличивается на два в каждом такте. Подсчитывается число единичных приращений ординаты, и в конце преобразования оно выдается в качестве выходного значения логарифмической функции. 2 з.п. ф-лы, 1ил.

Реферат

Изобретение относится к цифровой и информационной технике и может быть использовано для предварительной обработки экспериментальной входной информации в автоматизированных системах научных исследований.

Известны цифровые функциональные преобразователи [А.с. 444187А1 SU G06F 15/20, А.с. 744595Al SU G06F 17/10] на базе разностно-итерационных принципов их функционирования. Недостатком таких функциональных преобразователей является их невозможность функционального преобразования входных данных по закону логарифма.

Наиболее близким по технической сущности является цифровой функциональный преобразователь [А.с. 1188750 А1, SU, G06F 17/10]. Он состоит из накапливающего сумматора-вычислителя, первого и второго регистров, блока управления, причем выходы блока управления соединены с синхровходом занесения данных в накапливающий сумматор-вычитатель, а входы накапливающего сумматора-вычитателя связаны с выходами регистров. Недостатками этого цифрового функционального преобразователя являются невозможность реализации им логарифмической зависимости и большая абсолютная погрешность (единица младшего разряда).

Задачей настоящего изобретения является расширение функциональных возможностей цифрового функционального преобразователя в части возможности функционального преобразования экспериментальных данных по закону логарифмической функции и понижение в два раза максимальной абсолютной погрешности.

Технический результат - заявленный цифровой функциональный преобразователь позволяет реализовать логарифмическую зависимость при цифровом преобразовании экспериментальных данных и вдвое снизить абсолютную погрешность преобразования.

Технический результат достигается предложенным цифровым преобразователем, содержащим накапливающий сумматор-вычитатель, первый и второй регистры, блок управления, причем выходы блока управления соединены с синхровходами занесения данных в сумматор-вычитатель, а входы накапливающего сумматора-вычитателя связаны с выходами регистров. Также в него дополнительно введены двоичный счетчик, первый и второй блоки элементов И, блок элементов ИЛИ и блок формирования параллельного кода функции из унитарного кода, причем выходы двоичного счетчика через первый блок элементов И и блок элементов ИЛИ связаны со входами накапливающего сумматора-вычитателя, а выходы первого регистра - через второй блок элементов И и блок элементов ИЛИ также связаны со входами накапливающего сумматора-вычитателя, знаковый разряд которого связан с блоком управления, выходы которого связаны с синхровходами первого и второго блоков элементов И, а входы и выход блока формирования параллельного кода функции связаны с блоком управления, выход которого связан со вторым младшим разрядом двоичного счетчика. Блок формирования параллельного кода функции из унитарного кода содержит второй счетчик аргумента, третий счетчик функции, третий блок логических элементов И и второй регистр функции, причем счетные входы счетчика аргумента и счетчика функции связаны с блоком управления, синхровходы третьего блока логических элементов И связаны с выходом второго счетчика аргумента и с блоком управления, с которым также связаны входы сброса в "0" второго регистра функции и третьего счетчика функции. Блок управления содержит триггер, первую и вторую линии задержки, первый, второй и третий элемент И, первый и второй элемент НЕ, причем инверсный выход триггера соединен с выходом блока управления "окончание преобразования" и через второй элемент НЕ - со входом третьего элемента И, другой вход которого связан со входом / тактовых импульсов, а выход третьего элемента И связан со входами первого и второго элементов И, другие входы которых соединены с прямым выходом триггера, причем выход третьего элемента И связан со счетным входом второго счетчика аргумента и со входом второго младшего разряда двоичного счетчика, кроме того, вход первого элемента НЕ и вход второго элемента И связаны со знаковым разрядом накапливающего сумматор-вычитателя, а выход первого элемента НЕ связан со входом первого элемента И, выход которого через первую линию задержки связан с синхровходами второго блока элементов И, а выход второго элемента И через вторую линию задержки связан с синхровходами первого блока элементов И и со счетным входом третьего счетчика функции, вход сброса в "0" которого, как и второго регистра функции, связан со входом предварительной установки ПУ, который связан еще и со входом сброса в "0" триггера, вход установки в "1" которого связан со входом "Пуск" и, наконец, вход сброса в "0" триггера связан с выходом второго счетчика аргумента.

Отличительные признаки позволили реализовать функциональное преобразование по закону логарифма, а связь блока управления со знаковым разрядом накапливающего сумматора-вычитателя и со вторым младшим разрядом двоичного счетчика обеспечили снижение абсолютной погрешности в два раза (менее 0,5 единицы младшего разряда). Это является новым техническим решением в технике цифрового функционального преобразования, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявленная совокупность блоков, узлов и элементов, а также их связей позволяет произвести цифровое функциональное преобразование по логарифмическому закону.

Предложенный цифровой функциональный преобразователь промышленно применим, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральные логические микросхемы).

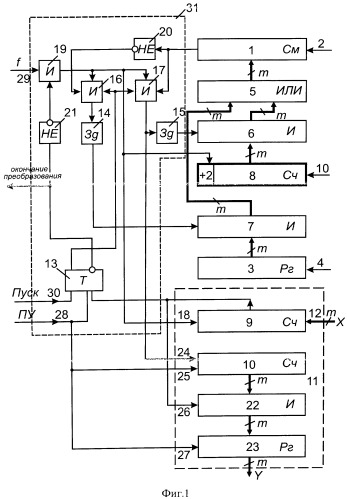

На фиг.1 приведена функциональная схема цифрового функционального преобразователя.

Заявленное устройство содержит (фиг.1) накапливающий сумматор-вычитатель 1 со входом 2 предварительной установки его значения, первый регистр 3 со входом 4 предварительной установки его значения, блок элементов "ИЛИ" 5, два блока элементов "И" 6, 7, три счетчика 8, 9, 10, два последних 9, 10 из которых находятся в блоке 11 формирования параллельного кода функции Y из унитарного кода, имеющего вход 12 ввода аргумента X. В этот же блок 11 формирования параллельного кода функции Y из унитарного кода входит третий блок элементов И 22 и второй регистр 23. Кроме того, заявленное устройство содержит блок управления 31, в который входят триггер 13, первая 14 и вторая 15 линии задержки, первый 16, второй 17 и третий 19 элементы И, первый 20 и второй 21 элементы НЕ.

Накапливающий сумматор-вычитатель 1, все регистры, все счетчики, блок элементов ИЛИ 5, блоки элементов И 6, 7 содержат m двоичных разрядов, где m - максимальная разрядность входных и выходных данных, включая знак. Причем, первый регистр 3 через блок элементов И 7, как и двоичный счетчик 8 через блок элементов И 6, связаны с блоком элементов ИЛИ 5, который связан с накапливающим сумматором-вычитателем 1. Кроме того, разрешающие входы блоков элементов И 7 и 6 связаны с выходами первой 14 и второй 15 линий задержки, находящихся в блоке управления 31. В блоке 31 управления триггер 13 имеет прямой и инверсный выходы а также входы установки "1" и сброса в "0". Элемент И 19 имеет два входа, а два элемента И 16, 17 имеют по три входа. Далее, в блоке 11 счетчик 9 имеет вход 12 для ввода аргумента X, счетчик 10 через блок "И" 22 соединен с регистром 23 выходного значения функции Y. Кроме того, счетчик 10 имеет счетный вход 24 и вход 25 сброса в "0". Блок "И" 22 имеет синхровход 26, а регистр 23 имеет вход 27 сброса в "0". Вход 28 - сигнал предварительной установки - обозначен "ПУ". Вход 29 - тактовых импульсов - обозначен "f". Вход 30 обозначен "Пуск". Выход 31 обозначен "окончание преобразования". Вход "ПУ" 28 связан со входом сброса в "0" триггера 13 и со входом 25 сброса счетчика 10 а также со входом 27 сброса в "0" второго регистра функции Y 23. Инверсный выход триггера 13 связан с выходом 31 "окончание отработки". В блоке управления 31 инверсный выход триггера 13 через второй элемент НЕ 21 соединен со входом третьего элемента И 19, на другой вход которого поступает тактовые импульсы f 29, а выход которого связан со входами первого 16 и второго 17 элементов И. Их выходы через первую 14 и вторую 15 линии задержки связаны с разрешающими входами блоков элементов И 7 и 6, соответственно. Прямой выход триггера 13 связан со входами первого 16 и второго 17 элементов И. Вход первого элемента 16 И через элемент НЕ 20 связан со знаковым разрядом Зн накапливающего сумматора-вычитателя 1. Этот же разряд Зн связан также со входом второго элемента И 17. Выход третьего элемента 19 И связан также со вторым младшим разрядом двоичного счетчика 8 и со входом 18 блока 11. А выход второго элемента 17 И связан также со входом 24 блока 11. Вход 28 ПУ блока управления 31 связан со входами 25 и 27 блока 11. Выход счетчика 9 в блоке 11 связан со входом установки сброса в "0" триггера 13 в блоке 31 и входом 26 блока 11.

Достоверность достижения цели изобретения - реализация функционального преобразования по логарифмическому закону - подтверждается математическим обоснованием, изложенным в журнале "Известия вузов. Северо-Кавказский регион, Технические науки, 2011, №2, с.16-18)"]. Логарифмическая функция имеет вид y = M − log a ( 1 + x B ) , где М и В - масштабы по осям Y и X, соответственно, A = M ln a , B≥A,а>1, Параметры А и В должны быть округлены до m - разрядных двоичных чисел.

В исходном состоянии цифрового преобразователя подачей импульса на вход 28 ПУ триггер 13 устанавливается в "0". Кроме того, по входу 2 в накапливающий сумматор-вычитатель 1 заносится константа (В-2А), по входу 4 в первый регистр 3 заносится константа (2А1-1) в дополнительном коде, по входу 10 в двоичный счетчик 8 заносится константа (2В-2А), и по входу 12 в счетчик 9 аргумента X заносится аргумент X со знаком "-" все величины в дополнительном коде. Счетчик 10 функции Y и второй регистр сброшены в "0". Цифровой функциональный преобразователь готов к работе. Спустя некоторое время может поступить сигнал "Пуск" (вход 30) на начало преобразования. Он установит триггер 13 в "1".

Сигнал "0" с инверсного выхода триггера 13 проходит через элементы 21 "НЕ" и открывает элемент 19 "И". А очередной положительный импульс с частотой f (вход 29) проследует на вход первого и второго элементов "И" 16 и 17 а также на второй младший разряд двоичного счетчика 8, увеличив его содержимое на "+2", и на вход 18 счетчика 9 аргумента X, увеличив его содержимое на "+1". (Счетчик 9 практически работает как вычитающий). Одновременно положительный импульс с выхода второго элемента 17 "И" поступит на вход 24 счетчика 10 функции Y, если знак накапливающего сумматора-вычитателя 1 будет "-" (единица в знаковом разряде Зн).

Если же знак накапливающего сумматор-вычитателя 1 будет "+" (ноль в знаковом разряде), то на вход 24 счетчика 10 функции Y ничего не поступит (элемент 17 И будет закрыт). А сигнал "1" появится на выходе первого элемента НЕ 20. Он проследует на вход первого элемента 16 И. Спустя некоторое время (менее четверти периода f) возникает положительный импульс на выходе первой линии задержки Зд 14 или второй линии задержки Зд 15 (только одной), каждый из которых подсуммирует либо содержимое регистра Рг 3 (через второй блок элементов "И" 7 и блок элементов "ИЛИ" 5) к накапливающему сумматору-вычитателю 1, либо содержимое двоичного счетчика 8 (через первый блок элементов "И" 6 и блок элементов "ИЛИ" 5) -к накапливающему сумматору-вычитателю 1. На этом один такт входных импульсов f закончится. Новое значение знака Зн накапливающего сумматора-вычитателя 1 будеть управлять работой функционального преобразователя в следующем такте. Каждый отработанный такт входных импульсов f (вход 29) подсчитывается по входу 18 счетчиком аргумента X 9 (он вычитающий).

При поступлении ровно X (аргумент) импульсов счетчик аргумента X 9 выдаст сигнал на сброс в "0" триггера 13. Сигнал "1" с его инверсного выхода пройдет на выход "окончание преобразования", а также через второй элемент НЕ 21 и закроет третий элемент И 19, прервав тем самым поступление импульсов со входа f 29. Одновременно положительный ("1") сигнал с выхода счетчика аргумента X 9 поступит на синхровходы 26 третьего блока элементов И 22, и содержимое счетчика функции Y 10 занесется во второй регистр функции Y 23, являющийся выходным для цифрового функционального преобразователя. Работа цифрового функционального преобразователя закончена.

В результате преобразования аргумента X будет получена логарифмическая функция Y = M ⋅ log a ( x B ) .

Достоверность функционирования для аргумента Х=12 подтвердим на простом примере М=А=7 и В=11 (а=е, где е - основание натуральных алгоритмов (см. таблицу 1)). Малые значения А и В взяты по соображениям сокращения размеров таблицы 1.

| Таблица 1 | ||||||

| Результаты работы цифрового функционального преобразователя: (при А=7, В=11, а=е, Х=12) | ||||||

| i | См 1 | Сч 8 | Рг3 | Сч9 | Сч 10 | 7 ⋅ ln ( 1 + x 11 ) |

| 0 | -3 | 10 | -13 | -12 | 0 | 0 |

| 1 | 7 | 12 | -13 | -11 | 1 | 0,609 |

| 2 | -6 | 14 | -13 | -10 | 1 | 1,169 |

| 3 | 8 | 16 | -13 | -9 | 2 | 1,688 |

| 4 | -5 | 18 | -13 | -8 | 2 | 2,171 |

| 5 | 13 | 20 | -13 | -7 | 3 | 2,623 |

| 6 | 0 | 22 | -13 | -6 | 3 | 3,047 |

| 7 | -13 | 24 | -13 | -5 | 3 | 3,447 |

| 8 | 11 | 26 | -13 | -4 | 4 | 3,826 |

| 9 | -2 | 28 | -13 | -3 | 4 | 4,185 |

| 10 | 26 | 30 | -13 | -2 | 5 | 4,526 |

| 11 | 13 | 32 | -13 | -1 | 5 | 4,852 |

| 12 | 0 | 34 | -13 | 0 | 5 | 5,163 |

| X | Y | Yточное |

1. Цифровой функциональный преобразователь, содержащий накапливающий сумматор-вычитатель, первый и второй регистры, блок управления, причем выходы блока управления соединены с синхро-входами занесения данных в сумматор-вычитатель, а входы накапливающего сумматора-вычитателя связаны с выходами регистров, отличающийся тем, что в него дополнительно введены двоичный счетчик, первый и второй блоки элементов И, блок элементов ИЛИ и блок формирования параллельного кода функции из унитарного кода, причем выходы двоичного счетчика через первый блок элементов И и блок элементов ИЛИ связаны со входами накапливающего сумматора-вычитателя, а выходы первого регистра - через второй блок элементов И и блок элементов ИЛИ также связаны со входами накапливающего сумматора-вычитателя, знаковый разряд которого связан с блоком управления, выходы которого связаны с синхровходами первого и второго блоков элементов И, а входы и выход блока формирования параллельного кода функции связаны с блоком управления, выход которого связан со вторым младшим разрядом двоичного счетчика.

2. Устройство по п.1, отличающееся тем, что блок формирования параллельного кода функции из унитарного кода содержит второй счетчик аргумента, третий счетчик функции, третий блок логических элементов И и второй регистр функции, причем счетные входы счетчика аргумента и счетчика функции связаны с блоком управления, синхровходы третьего блока логических элементов И связаны с выходом второго счетчика аргумента и с блоком управления, с которым также связаны входы сброса в "0" второго регистра функции и третьего счетчика функции.

3. Устройство по п.1, отличающееся тем, что блок управления содержит триггер, первая и вторая линии задержки, первый, второй и третий элемент И, первый и второй элемент НЕ, причем инверсный выход триггера соединен с выходом блока управления "окончание преобразования" и через второй элемент НЕ - со входом третьего элемента И, другой вход которого связан со входом f тактовых импульсов, а выход третьего элемента И связан со входами первого и второго элементов И, другие входы которых соединены с прямым выходом триггера, причем выход третьего элемента И связан со счетным входом второго счетчика аргумента и со входом второго младшего разряда двоичного счетчика, кроме того, вход первого элемента НЕ и вход второго элемента И связаны со знаковым разрядом накапливающего сумматор-вычитателя, а выход первого элемента НЕ связан со входом первого элемента И, выход которого через первую линию задержки связан с синхровходами второго блока элементов И, а выход второго элемента И через вторую линию задержки связан с синхровходами первого блока элементов И и со счетным входом третьего счетчика функции, вход сброса в "0" которого, как и второго регистра функции связан со входом предварительной установки ПУ, который связан еще и со входом сброса в "0" триггера, вход установки в "1" которого связан со входом "Пуск" и, наконец, вход сброса в "0" триггера связан с выходом второго счетчика аргумента.