Гетерогенный процессор

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники, а именно к области цифровой обработки сигналов. Технический результат - снижение энергопотребления на единицу производительности и повышение производительности процессора. Гетерогенный процессор содержит: универсальный процессор с портом, блок ввода/вывода с портом, контроллер оперативной памяти с портом, блок ускоренного выполнения алгоритмов цифровой обработки сигналов с портом, состоящий из контроллера прямого доступа к памяти, блока памяти программ и блока управления вычислительными секциями, каждая из которых состоит из блока регистрового файла с портами, соединенного с портом блока управления вычислительными секциями, блока локального ОЗУ и блока арифметико-логического устройства, состоящего из блоков входных регистров, блоков выходных регистров, блоков умножителей и блоков сумматоров, установленных в количестве, достаточном для выполнения операции B±C×D каждый такт, где B, C и D - комплексные числа, действительные и мнимые, части которых являются 32-разрядными числами с плавающей запятой, а процессор снабжен блоком буферной памяти с портами. 3 ил.

Реферат

Изобретение относится к области вычислительной техники, а именно к области цифровой обработки сигналов, где необходимо совмещение функций универсального микропроцессора и функций процессора цифровой обработки сигналов.

Известно, что универсальные микропроцессоры традиционно используются для построения компьютеров, серверов (Intel, AMD, IBM), а также для встраивания в другие системы (ARM, MIPS). Для универсальных микропроцессоров характерны задачи с большим количеством условных переходов и незначительным уровнем внутреннего параллелизма, соответственно, универсальные микропроцессоры оптимизируются с целью эффективного предсказания переходов и извлечения встроенного параллелизма команд. Для программирования универсальных микропроцессоров используются языки программирования высокого уровня, такие как язык Си. Другой класс микропроцессоров, называемых процессорами цифровой обработки сигналов, применяется в областях вычислительной техники, где имеется поток входных данных, над которым требуется выполнить набор определенных действий в режиме их поступления. В качестве входных данных могут быть оцифрованные значения с видеокамеры, микрофона, локатора и других источников. Задачи цифровой обработки сигналов характеризуются высокой степенью параллелизма по данным, незначительным количеством условных переходов и высокой скоростью поступления входных данных. Для эффективного программирования процессоров цифровой обработки сигналов традиционно используют языки низкого уровня, типа ассемблер.

С развитием концепции систем-на-кристалле, предполагающей интеграцию на одном кристалле кремния нескольких функциональных устройств, стали появляться микросхемы, объединяющие функциями универсального микропроцессора и процессора цифровой обработки сигналов.

Наиболее близким по технической сути и достигаемому результату является микропроцессор Cell компании IBM, включающий универсальный процессор с портом, блок ввода/вывода с портом, контроллер оперативной памяти с портом и 8 блоков ускоренного выполнения алгоритмов цифровой обработки сигналов с портом (J.A.Kahle, М.N. Day и др. " Introduction to the Cell multiprocessor", IBM J. RES& DEV. VOL. 49 NO. 4/5, JULY/SEPTEMBER 2005, p.589-504).

Данный микропроцессор позволяет достаточно эффективно решать задачи, совмещающие задачи управления и задачи цифровой обработки сигналов для большинства типов данных, таких как целочисленные и вещественные данные. Однако существуют задачи, в которых данные представлены в виде комплексных чисел, действительные и мнимые части которых являются 32-разрядными числами с плавающей запятой. Для такого типа данных операция вида B±C×D, которая является основной операций быстрого преобразования Фурье, требует 10 арифметических операций - 4 умножения и 6 сложений/вычитаний с 32-разрядными числами с плавающей запятой. Традиционно, арифметические операции выполняются последовательно, при этом для каждой операции требуется выполнять считывание данных из регистрового файла и сохранение результат в регистровом файле. В описываемом процессоре применены современные схемы умножения и сложения, что позволяет выполнять операции за 1 такт процессорной частоты, в результате чего операция B±C×D с комплексными числами будет выполняться за 10 тактов и потребует 20 считываний и 10 записей в регистровый файл на одну операцию, что приводит к необходимости выполнения значительного количества дополнительных действий, что приводит к увеличению энергопотребления.

Таким образом, недостатком описанного выше процессора является высокое энергопотребление на единицу производительности.

Задачей изобретения является снижение энергопотребления на единицу производительности.

Техническим результатом от использования изобретения является снижение энергопотребления на единицу производительности и повышение производительности процессора, путем увеличение скорости и энергоэффективности выполнения программ, сочетающих задачи управления и задачи цифровой обработки сигналов.

Указанный технический результат достигается тем, что в гетерогенном процессоре, включающем универсальный процессор с портом, блок ввода/вывода с портом, контроллер оперативной памяти с портом и блок ускоренного выполнения алгоритмов цифровой обработки сигналов с портом, процессор снабжен блоком буферной памяти с портами, один из которых связан с блоком ввода/вывода, а универсальный процессор, блок ускоренного выполнения алгоритмов цифровой обработки сигналов и контроллер оперативной памяти снабжены дополнительными портами каждый, при этом универсальный процессор и блок ускоренного выполнения алгоритмов цифровой обработки сигналов посредством своих портов связаны с портами блока буферной памяти и портами контроллера оперативной памяти, а блок ускоренного выполнения алгоритмов цифровой обработки сигналов состоит из контроллера прямого доступа к памяти, блока памяти программ и блока управления вычислительными секциями, каждая из которых состоит из блока регистрового файла с портами, соединенного с портом блока управления вычислительными секциями, блока локального ОЗУ и блока арифметико-логического устройства, состоящего из блоков входных регистров, блоков выходных регистров, блоков умножителей и блоков сумматоров, установленных в количестве, достаточном для выполнения операции B±C×D каждый такт, где B, C и D - комплексные числа, действительные и мнимые, части которых являются 32-разрядными числами с плавающей запятой.

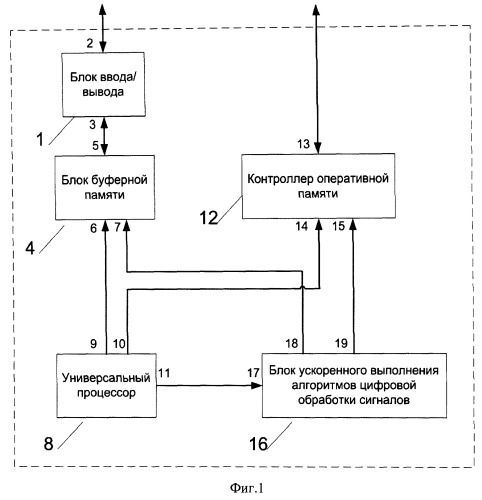

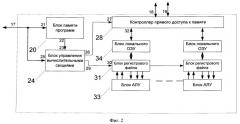

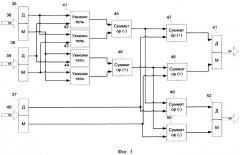

Изобретение поясняется чертежами, где на фиг.1 изображена общая схема гетерогенного процессора, на фиг. 2 - структурная схема блока ускоренной обработки алгоритмов цифровой обработки сигналов, на фиг.3 - структурная схема блока арифметико-логического устройства.

Гетерогенный процессор состоит из блока ввода/вывода 1 с портами 2 и 3, блока буферной памяти 4 с портами 5, 6 и 7, универсального процессора 8 с портами 9, 10 и 11, контроллера прямого доступа к памяти 12 с портами 13, 14 и 15, блока ускоренной обработки алгоритмов цифровой обработки сигналов 16 с портами 17, 18 и 19.

К порту 2 блока вода/вывода 1 подключены внешние линии связи, соединяющие гетерогенный процессор с другими внешними устройствами, порт 3 блока ввода/вывода 1 подключен к порту 5 блока буферной памяти 4, порт 6 блока буферной памяти 4 соединен с портом 9 универсального процессора 8, порт 7 блока буферной памяти 4 соединен с портом 18 блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16, порт 10 универсального процессора 8 соединен с портом 14 контроллера прямого доступа к оперативной памяти 12, а порт 11 универсального процессора 8 подключен к порту 17 блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16, порт 19 которого соединен с портом 15 контроллера оперативной памяти 12, порт 13 которого подключен к микросхемам вешней оперативной памяти.

Блок ускоренного выполнения алгоритмов цифровой обработки сигналов 16 состоит из блока памяти программ 20, порт 21 которого соединен с портом 11 универсального процессора 8, а порт 22 соединен с портом 23 блока управления вычислительными секциями 24, порт 25 которого соединен с портом 11 универсального процессора 8, порт 26 соединен с портом 27 контроллера прямого доступа к памяти 28, а порт 29 соединен с портом 30 блока регистрового файла 31. Порты 32 контроллера прямого доступа к памяти 28 соединены с вычислительными секциями, каждая из которых состоит из блока арифметико-логического устройства 33, блока регистрового файла 31 и блока локального ОЗУ 34, последовательно соединенных между собой. Порты 18 и 19 блока контроллера прямого доступа к памяти 28 соединены с портами 7 буферной памяти 4 и 15 контроллера оперативной памяти 12 соответственно.

Блок арифметико-логического устройства 33 каждой секции содержит блоки входных регистров 35, 36, 37, с входными портами 38, 39, 40 соответственно, связанных с портами блоков умножителей 41, 42, 43, 44, которые в свою очередь соединены с блоками сумматоров 45, 46. Блоки сумматоров 47, 48, 49, 50 связаны с блоками выходных регистров 51, 52, с выходными портами 53, 54.

Блок ввода/вывода 1 предназначен для приема данных, поступающих с внешних линий связи на его порт 2, и записи их в блок буферной памяти 4, а также для чтения данных из блока буферной памяти 4 и передачи их на внешние линии связи через вход 2.

Блок буферной памяти 4 предназначен для хранения данных, переданных от блока ввода/вывода 1, через порт 5, и обеспечения доступа к этим данным со стороны универсального процессора 8 через порт 6 или со стороны блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16 через порт 7. В блоке буферной памяти 4 также хранятся данные, переданные с порта 9 универсального процессора 8 через порт 6, при этом обеспечивается доступ к этим данным со стороны блока ввода/вывода 1 через порт 5, или блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16 через порт 7. Блок буферной памяти 4 также используется для хранения данных, переданных со стороны блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16 через порт 7, и обеспечения доступа к этим данным со стороны универсального процессора 8 через вход 6, или со стороны блока ввода/вывода 1 через порт 5. Блок буферной памяти 4 может быть построен на основе стандартной статической памяти с произвольным доступом и схемой управления доступом.

Универсальный процессор 8 предназначен для выполнения задач управления, а также для загрузки управляющей программы с порта 11 в порт 17 блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16. При этом универсальный процессор 8 хранит промежуточные данные во внешней оперативной памяти, к которой он обращается через контроллер оперативной памяти 12.

Контроллер оперативной памяти 12 предназначен для обслуживания запросов к микросхемам внешней памяти со стороны универсального процессора 8, поступающих на порт 14, и со стороны блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16, поступающих на порт 15. Контроллер оперативной памяти 12 может быть построен на основе стандартного контроллера оперативной памяти.

Блок ускоренного выполнения алгоритмов цифровой обработки сигналов 16, содержащий блок памяти программ 20, блок управления вычислительными секциями 24, контроллер прямого доступа к памяти 28 и несколько вычислительных секций, каждая из которых содержит блок арифметико-логического устройства 33, блок регистрового файла 31 и блок локального ОЗУ 34, предназначен для выполнения арифметических команд с 32-разрядными числами с плавающей запятой каждый такт, в том числе операций типа B±C×D, где В, С и D - комплексные числа, действительные и мнимые, части которых являются 32-разрядными числами с плавающей запятой каждый такт.

Описанный выше гетерогенный процессор работает следующим образом.

Блок ввода/вывода 1 записывает данные, поступающие с внешних линий связи на его вход 2, в блок буферной памяти 4, а также производит чтение данных из блока буферной памяти 4 и передает их на внешние линии связи через вход 2. Данные, поступающие с внешних линий связи, могут быть программой для универсального процессора 8, данными для универсального процессора 8, программой для блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16 или данными для блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16.

Если гетерогенный процессор выполняет задачу управления, то с внешних линий связи 2 через блок ввода/вывода 1 в блок буферной памяти 4 передается программа для управляющего процессора 8. Управляющей процессор 8 считывает программу из блока буферной памяти 4 и приступает к ее выполнению. В процессе выполнения программы может происходить обмен данными между универсальным процессором 8 и микросхемами внешней оперативной памяти через контроллер оперативной памяти 12.

Если гетерогенный процессор выполняет задачу цифровой обработки сигналов, то с внешних линий связи 2 через блок ввода/вывода 1 в блок буферной памяти 4 передается программа для блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16. Универсальный процессор 8 считывает из блока буферной памяти 4 программу для блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16 и записывает ее в блок памяти программ 20 блока ускоренного выполнения алгоритмов цифровой обработки сигналов 16, после чего передает управление блоку управления вычислительными секциями 24. Блок управления вычислительными секциями 24 управляет следующим процессами:

- управляет контроллером прямого доступа к памяти 28 для передачи данных из блока буферной памяти 4 в микросхемы внешней памяти через контроллер оперативной памяти 12 и наоборот;

- управляет контроллером прямого доступа к памяти 28 для передачи данных из блока локального ОЗУ вычислительных секций 34 в микросхемы внешней памяти через контроллер оперативной памяти 12 и наоборот;

- управляет обменом между блоком локального ОЗУ вычислительных секций 34 и блоками регистрового файла вычислительных секций 31.

Все вышеперечисленные операции выполняются одновременно.

Блок арифметико-логического устройства 33, входящий в состав вычислительной секции при выполнении операции вида B±C×D, где В, С и D - комплексные числа, действительные и мнимые части которых являются 32-разрядными числами с плавающей запятой, работает следующим образом:

из блока регистрового файла 31 считываются три комплексных числа B, C и D и записываются через входные порты 38, 39, 40 в блоки входных регистров 35, 36, 37, при этом с порта 38 в регистр 35 подается число C, с порта 39 в регистр 36 подается число D, с порта 40 в регистр 37 подается число В. Операция умножения комплексных чисел C и D требует четырех умножений, одного сложения и одного вычитания, которые выполняются в блоках умножителей 41, 42, 43, 44 и блоках сумматорах 45 и 46 соответственно. Операция сложения комплексных чисел требует две операции сложения, которые выполняются блоками сумматоров 47 и 48, а операция вычитания комплексных чисел требует двух операций вычитания, которые выполняются блоками сумматоров 49 и 50 соответственно. Результат операции B+C×D запоминается в блоке выходного регистра 51, результат операции B-C×D запоминается в блоке выходного регистра 52, и с их выходных портов 53 и 54 результаты записываются в регистровый файл 31.

Таким образом, за счет обеспечения возможности выполнения операции вида B±C×D, где В, С и D - комплексные числа, действительные и мнимые части которых являются 32-разрядными числами с плавающей запятой каждый такт, выполняя при этом одно считывание кода команды, одно чтение из регистрового файла и одну запись в регистровый файл, достигается снижение энергопотребления на единицу производительности и повышение производительности процессора.

Гетерогенный процессор, включающий универсальный процессор с портом, блок ввода/вывода с портом, контроллер оперативной памяти с портом и блок ускоренного выполнения алгоритмов цифровой обработки сигналов с портом, отличающийся тем, что процессор снабжен блоком буферной памяти с портами, один из которых связан с блоком ввода/вывода, а универсальный процессор, блок ускоренного выполнения алгоритмов цифровой обработки сигналов и контроллер оперативной памяти снабжены дополнительными портами каждый, при этом универсальный процессор и блок ускоренного выполнения алгоритмов цифровой обработки сигналов посредством своих портов связаны с портами блока буферной памяти и портами контроллера оперативной памяти, а блок ускоренного выполнения алгоритмов цифровой обработки сигналов состоит из контроллера прямого доступа к памяти, блока памяти программ и блока управления вычислительными секциями, каждая из которых состоит из блока регистрового файла с портами, соединенного с портом блока управления вычислительными секциями, блока локального ОЗУ и блока арифметико-логического устройства, состоящего из блоков входных регистров, блоков выходных регистров, блоков умножителей и блоков сумматоров, установленных в количестве, достаточном для выполнения операции B±C×D каждый такт, где B, C и D -комплексные числа, действительные и мнимые, части которых являются 32-разрядными числами с плавающей запятой.