Ограничение областей памяти для считывания команд в зависимости от аппаратного режима и флага безопасности

Иллюстрации

Показать всеИзобретение относится к области систем обработки данных, имеющих множество аппаратных режимов работы, а также к управлению доступом к памяти в зависимости от текущего аппаратного режима. Техническим результатом является обеспечение возможности осуществления процессором доступа к данным памяти даже в том случае, если эта возможность заблокирована в текущем режиме работы процессора. Устройство для обработки данных (2) включает в себя процессор (8), память (6) и схему (12) управления памятью. Процессор (8) работает во множестве аппаратных режимов, включающих в себя привилегированный режим и пользовательский режим. При работе в привилегированном режиме схема (12) управления памятью блокирует выборку команд процессором (8) из адресных зон (34, 38, 42) памяти в памяти (6), в которые можно производить запись в пользовательском режиме, если флаг безопасности в регистре (46) установлен таким образом, что указывает на то, что этот механизм блокировки действует. 4 н. и 9 з.п. ф-лы, 4 ил.

Реферат

Это изобретение относится к области систем обработки данных. В частности, оно относится к системам обработки данных, имеющим множество аппаратных режимов работы, а также к управлению доступом к памяти в зависимости от текущего аппаратного режима.

Известны системы обработки данных, в которых процессор имеет множество аппаратных режимов работы, включающих в себя привилегированный режим и пользовательский режим. Привилегированный режим обычно будет использоваться для более надежного программного кода, например ядра операционной системы, и будет иметь доступ к большему числу областей памяти, чем в случае, когда процессор работает в пользовательском режиме. Пользовательский режим, как правило, будет использоваться для менее надежных программ, например прикладных программ. Таким образом можно предотвратить вредоносный или случайный доступ из программы в заранее определенные области памяти за счет использования блока управления памятью или блока защиты памяти, распознающих текущий режим работы процессора и предотвращающих доступ в заранее определенные области памяти, если процессор не находится в привилегированном режиме. В таких системах используется модель, при которой привилегированный режим работы имеет доступ к большему количеству системных ресурсов, например областей в памяти, чем пользовательский режим.

Одним из типов вредоносной атаки на безопасность либо неудачной ошибочной работы, который может возникнуть, является ситуация, когда систему без соответствующей необходимости заставляют исполнить команды программы, хранящиеся в областях памяти, в которые можно производить запись в пользовательском режиме, причем исполнить их в привилегированном режиме. Таким образом, в качестве одного из примеров, человек может записать команды вредоносной программы в области памяти, которые доступны в пользовательском режиме, а затем переключить процессор в привилегированный режим, в котором может быть выполнен доступ в безопасные зоны памяти и исполнить вредоносные команды, считанные из области памяти, доступной в пользовательском режиме.

Согласно одному аспекту настоящего изобретения, предлагается устройство для обработки данных, содержащее:

- процессор, способный реагировать на поток команд программы для выполнения операций обработки; и

- схему управления памятью, соединенную с упомянутым процессором и памятью и выполненную с возможностью управлять доступом упомянутого процессора к упомянутой памяти,

причем:

упомянутый процессор имеет множество аппаратных режимов работы, включающих в себя, по меньшей мере, первый режим и второй режим;

упомянутая схема управления памятью управляет доступом к упомянутой памяти таким образом, что:

- (i) при нахождении упомянутого процессора в упомянутом первом режиме, упомянутая схема управления памятью разрешает доступ для записи к первому участку упомянутой памяти и не разрешает, по меньшей мере, доступ для записи ко второму участку упомянутой памяти, и

- (ii) при нахождении упомянутого процессора в упомянутом втором режиме упомянутая схема управления памятью разрешает доступ для записи к упомянутому первому участку упомянутой памяти и разрешает доступ для записи ко второму участку упомянутой памяти; и

упомянутая схема управления памятью способна реагировать на флаг безопасности, имеющий установленное значение, чтобы предоставлять упомянутому процессору в упомянутом первом режиме право, не предоставленное упомянутому процессору в упомянутом втором режиме посредством предотвращения считывания упомянутым процессором из упомянутого первого участка памяти команд программы для исполнения упомянутым процессором в упомянутом втором режиме,

причем, если упомянутый флаг безопасности имеет упомянутое установленное значение, а упомянутый процессор находится в упомянутом втором режиме, то упомянутая схема управления памятью разрешает упомянутому процессору считывать значения данных из упомянутого первого участка упомянутой памяти.

В представленном способе учитывается, что на практике у системы мало причин для законного исполнения команд программы в привилегированном режиме, если эти команды программы считаны из зоны памяти, запись в которую может производиться в пользовательском режиме. Код, исполняемый в привилегированном режиме, обычно хранится в памяти, запись в которую можно производить только в привилегированном режиме. Это защищает команды программы, исполняемые в привилегированном режиме, от случайного изменения без соответствующей необходимости, а также от вредоносного изменения. Таким образом, представленный способ препятствует нанесению общего технического ущерба при предоставлении привилегированному режиму больших прав доступа, чем у пользовательского режима, путем использования схемы управления памятью для предотвращения считывания процессором команд программы, которые будут исполняться в привилегированном режиме, из областей памяти, запись в которые может производиться в пользовательском режиме. Эту функцию схемы управления памятью можно на глобальном уровне включать и отключать при помощи флага безопасности, в результате чего аппаратно можно поддерживать системы, в которых разработчик пожелает в привилегированном режиме исполнять команды программы, хранящиеся в областях памяти, запись в которые можно производить в пользовательском режиме, в то же время, обеспечивая простой путь отключения этой возможности с использованием флага безопасности для управления механизмом аппаратного контроля, обеспеченным схемой управления памятью. Понятно, что, хотя выше в качестве аппаратных режимов указаны привилегированный режим и пользовательский режим, представленный способ не ограничивается использованием в системах, имеющих такие режимы, и в более общем случае может быть использован в системах, имеющих первый режим и второй режим, где во втором режиме имеется доступ к большему числу зон памяти, чем в первом режиме, но при этом во втором режиме выборочно предотвращается исполнение команд, считанных из зон памяти, запись в которые может производиться в первом режиме. Если флаг безопасности имеет установленное значение, схема управления памятью может разрешить процессору, работающему во втором режиме, считывать значения данных из первого участка памяти, так как эти значения данных не выбираются из памяти как команды, которые нужно исполнить, а выбираются в маршрут передачи данных как значения данных, с которыми нужно работать.

Схема управления памятью может быть способна реагировать на данные управления для идентификации одной или более адресных зон памяти в памяти как части первого участка и одной или более адресных зон памяти в памяти как части второго участка. Таким образом, первый участок и второй участок не обязательно должны быть непрерывными в памяти, и могут определяться данными управления, считанными схемой управления памятью. В некоторых вариантах реализации настоящего изобретения это могут быть данные таблицы страниц памяти, считываемые блоком управления памятью.

Представленный способ особенно полезен в системах, в которых первый режим представляет собой пользовательский режим, служащий для исполнения прикладных программ, а второй режим представляет собой привилегированный режим, служащий для исполнения, по меньшей мере, программы ядра операционной системы.

Понятно, что схема управления памятью может принимать множество различных форм. Примерами схемы управления памятью являются блок управления памятью и блок защиты памяти.

Флаг безопасности можно удобным образом записывать под управлением команды программы, когда процессор находится во втором режиме, и этот флаг нельзя записывать под управлением команды программы, когда процессор находится в первом режиме. Таким образом, безопасность, обеспеченную флагом безопасности, нельзя нарушить путем изменения значения этого флага во время работы в первом режиме.

Согласно другому аспекту настоящего изобретения, предлагается устройство для обработки данных, содержащее:

- процессорное средство для выполнения операций обработки в ответ на поток команд программы; и

- схему средства управления памятью, соединенную с упомянутым процессорным средством и с запоминающим средством для хранения данных, для управления доступом упомянутого процессорного средства к упомянутому запоминающему средству,

причем:

упомянутое процессорное средство имеет множество аппаратных режимов работы, включающих в себя, по меньшей мере, первый режим и второй режим;

упомянутое средство управления памятью управляет доступом к упомянутому запоминающему средству таким образом, что:

- (i) при нахождении упомянутого процессорного средства в упомянутом первом режиме, упомянутое средство управления памятью разрешает доступ для записи к первому участку упомянутого запоминающего средства и не разрешает, по меньшей мере, доступ для записи ко второму участку упомянутого запоминающего средства, и

- (ii) при нахождении упомянутого процессорного средства в упомянутом втором режиме, упомянутое средство управления памятью разрешает доступ для записи к упомянутому первому участку упомянутого запоминающего средства и разрешает доступ для записи ко второму участку упомянутого запоминающего средства; и

упомянутое средство управления памятью способно реагировать на флаг безопасности, имеющий установленное значение, чтобы предоставлять упомянутому процессору в упомянутом первом режиме право, не предоставленное упомянутому процессору в упомянутом втором режиме посредством предотвращения считывания упомянутым процессорным средством из упомянутого первого участка упомянутого запоминающего средства команд программы для исполнения упомянутым процессорным средством в упомянутом втором режиме,

причем, если упомянутый флаг безопасности имеет упомянутое установленное значение, а упомянутое процессорное средство находится в упомянутом втором режиме, то упомянутое средство управления памятью разрешает упомянутому процессорному средству считывать значения данных из упомянутого первого участка упомянутого запоминающего средства.

Согласно еще одному аспекту настоящего изобретения, предлагается способ обработки данных, причем упомянутый способ содержит этапы, на которых:

- выполняют операции обработки процессором в ответ на поток команд программы; и

- управляют доступом упомянутого процессора к памяти с использованием схемы управления памятью, соединенной с упомянутым процессором и упомянутой памятью,

причем:

упомянутый процессор имеет множество аппаратных режимов работы, включающих в себя, по меньшей мере, первый режим и второй режим;

упомянутая схема управления памятью управляет доступом к упомянутой памяти таким образом, что:

- (i) при нахождении упомянутого процессора в упомянутом первом режиме, упомянутая схема управления памятью разрешает доступ для записи к первому участку упомянутой памяти и не разрешает, по меньшей мере, доступ для записи ко второму участку упомянутой памяти, и

- (ii) при нахождении упомянутого процессора в упомянутом втором режиме упомянутая схема управления памятью разрешает доступ для записи к упомянутому первому участку упомянутой памяти и разрешает доступ для записи ко второму участку упомянутой памяти; и

упомянутая схема управления памятью способна реагировать на флаг безопасности, имеющий установленное значение, чтобы предоставлять упомянутому процессору в упомянутом первом режиме право, не предоставленное упомянутому процессору в упомянутом втором режиме посредством предотвращения считывания упомянутым процессором из упомянутого первого участка упомянутой памяти команд программы для исполнения упомянутым процессором в упомянутом втором режиме,

причем, если упомянутый флаг безопасности имеет упомянутое установленное значение, а упомянутый процессор находится в упомянутом втором режиме, то упомянутая схема управления памятью разрешает упомянутому процессору считывать значения данных из упомянутого первого участка упомянутой памяти.

Настоящее изобретение также может быть реализовано в виде виртуальной машины, имеющей указанные выше признаки.

Теперь будут описаны варианты реализации настоящего изобретения только в качестве примера и со ссылкой на сопровождающие чертежи, из которых:

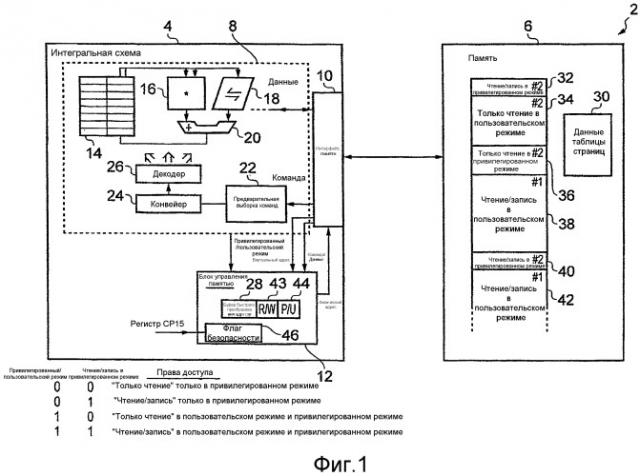

на фиг.1 схематично показана система обработки данных, включающая в себя процессор и память;

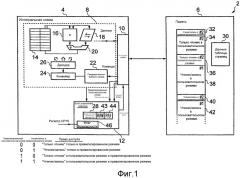

фиг.2 представляет собой блок-схему последовательности операций, иллюстрирующую управление операцией считывания из памяти в зависимости от следующего: типа аппаратного режима процессора; того, является ли чтение выборкой команды; и того, производится ли чтение из места в памяти, которое доступно в пользовательском режиме;

на фиг.3 схематично показаны многочисленные аппаратные режимы работы и связанные с ними права доступа и типичное использование этих режимов; и

на фиг.4 схематично показана реализация виртуальной машины.

На фиг.1 схематично показана система 2 обработки данных, включающая в себя интегральную схему 4, соединенную с памятью 6. Интегральная схема 4 включает в себя процессор 8, схему 10 интерфейса памяти и блок 12 управления памятью. Внутри процессора 8 имеются банк 14 регистров общего назначения, умножитель 16, схема 18 сдвига и сумматор 20, которые образуют маршрут передачи данных для выполнения операций обработки над значениями D данных, выбранными из памяти 6 под управлением команд I программы. Команды I программы, выбранные из памяти 6 блоком 22 предварительной выборки команд, подаются на конвейер 24 команд. Конвейер 24 команд управляет декодером 26 команд для генерации сигналов управления для маршрута 14, 16, 18, 20 передачи данных, чтобы сконфигурировать этот маршрут для выполнения требуемой операции (операций) обработки, указанной декодируемой командой, и управлять этим маршрутом. Специалистам в данной области техники будет понятно, что процессор 8 в типичном случае будет содержать значительно больше схемных элементов, которые опущены на фиг.1 для ясности.

В состав интегральной схемы 4 также включены схема 10 интерфейса памяти и блок 12 управления памятью. Схема 10 интерфейса памяти ответственна за генерацию сигналов доступа к памяти (которые могут быть чтением или записью), посылаемых от интегральной схемы 4 в память 6. Эти сигналы доступа к памяти используют физические адреса в памяти 6. Процессор 8 работает с использованием виртуальных адресов, хотя такая организация является только примером системы, в которой могут быть использованы представленные способы. Блок 12 управления памятью преобразует виртуальные адреса в физические адреса с использованием данных 30 таблицы страниц. Эти данные таблицы страниц представляют собой данные управления для блока 12 управления памятью. Данные таблицы страниц для зон памяти, доступ к которым был осуществлен в последнее время, хранятся внутри блока 12 управления памятью в буфере 28 быстрого преобразования адресов. Если данные таблицы страниц для конкретного доступа к памяти отсутствуют в буфере 28 быстрого преобразования адресов, то подходящие данные таблицы страниц выбираются из всего объема данных 30 таблицы страниц, хранящегося в памяти 6.

Память 6 предоставляет адресное пространство, адресуемое с использованием физических адресов, сгенерированных схемой интерфейса памяти. Память 6 может не обеспечивать объем хранения, соответствующий всему возможному адресному пространству. Адресное пространство разделено на адресные зоны 32, 34, 36, 38, 40, 42 памяти и т.д. Каждая из этих адресных зон 32-42 памяти имеет связанные с ней данные таблицы страниц, которые используются блоком 12 управления памятью для управления доступом к этим зонам памяти. Как будет понятно специалистам в данной области техники, эти данные таблицы страниц могут включать в себя данные, указывающие на то, может или нет быть произведен доступ к рассматриваемой адресной зоне памяти (либо только чтение, либо чтение/запись), если процессор 18 работает в привилегированном режиме или пользовательском режиме. Эта часть данных таблицы страниц указывается данными 44 флага P/U (Privileged/User - Привилегированный/пользовательский), изображенными как часть буфера 28 быстрого преобразования адресов. Данные таблицы страниц также включают данные 43 флага R/W (Read/Write - Чтение/Запись), которые указывают, представляет собой разрешенный доступ только чтение или чтение/запись. В таблице, показанной на фиг.1, приведен один из примеров различных значений данных 44 флага P/U и данных 43 флага R/W, отражающих разные права доступа. Адресные зоны 32, 34, 36, 40 памяти вместе образуют второй участок памяти 6, в который нельзя производить запись, когда процессор 8 находится в пользовательском режиме. Адресные зоны 32, 36 и 40 памяти доступны только в привилегированном режиме. Адресная зона 34 памяти в пользовательском режиме доступна только для считывания, и в нее нельзя производить запись в этом режиме. Адресные зоны 38 и 42 памяти образуют первый участок памяти 6, в который можно производить запись и чтение, когда процессор находится в пользовательском режиме, можно производить запись, когда процессор 8 находится в привилегированном режиме, можно производить чтение значений данных, когда процессор 8 находится в привилегированном режиме, но нельзя производить чтение значений команд, когда процессор 8 находится в привилегированном режиме.

Этот порядок в данном примерном варианте реализации настоящего изобретения контролируется блоком 12 управления памятью. Блок 12 управления памятью получает входной сигнал P/U от процессора 8, указывающий на то, в каком режиме в текущий момент находится процессор 8 - привилегированном режиме или пользовательском режиме. Блок 12 управления памятью также получает входной сигнал I/D (Instruction/Data - Команда/Данные) от схемы 10 интерфейса памяти, указывающий на то, к чему относится выполняемый доступ к памяти - выборке команды или операции доступа к данным. С использованием этих входных сигналов и значения флага безопасности, хранящегося в регистре 46 блока 12 управления памятью, может быть проведено предотвращение исполнения в привилегированном режиме команд программы, которые считаны из первого участка 38 и 42 памяти 6.

Фиг.2 представляет собой блок-схему последовательности операций, иллюстрирующую часть работы блока 12 управления памятью. Понятно, что блок 12 управления памятью может также быть обеспечен в виде блока защиты памяти. На этапе 48 ожидают получения схемой 10 интерфейса памяти запроса на чтение из памяти от процессора 8. После чего на этапе 50, используя входной сигнал P/U, поступающий в блок 12 управления памятью, определяют, находится ли процессор 8 в текущий момент в привилегированном режиме. Если процессор 8 не находится в привилегированном режиме, то процессор 8, в данном простом примере, будет находиться в пользовательском режиме, и происходит переход на этап 52. На этапе 52 определяют, помечен ли адрес памяти, к которому производится попытка доступа для считывания, в данных 30 таблицы страниц как доступный только при нахождении в привилегированном режиме. Если адрес памяти не помечен как "только для привилегированного", то происходит переход на этап 54, на котором разрешается доступ для считывания. Однако если адрес памяти помечен как адрес "только для привилегированного", то на этапе 56 доступ запрещается.

Если на этапе 50 определено, что процессор 8 в текущий момент находится в привилегированном режиме, происходит переход на этап 58. На этапе 58 определяют, установлен ли в текущий момент флаг безопасности, хранящийся в регистре 46. Если флаг безопасности установлен (имеет установленное значение), то будет проводиться политика недопущения выполнения процессором 8 команд, считанных из первого участка 38 и 42 памяти. Если на этапе 58 определено, что флаг безопасности не установлен, то происходит переход на этап 60, где разрешается доступ.

Если флаг безопасности установлен, как определено на этапе 58, то происходит переход на этап 62, где определяют, что собой представляет выполняемый доступ: выборку команды или доступ к данным. Это определение можно выполнять с использованием входного сигнала I/D, поступающего в блок 12 управления памятью. Если выполняемый доступ к памяти представляет собой доступ к данным, то происходит переход на этап 60, где снова разрешается доступ. Однако если установлен флаг безопасности, как определено на этапе 58, а операция доступа представляет собой выборку команды, как определено на этапе 62, то происходит переход на этап 64, где определяют, является ли рассматриваемый адрес памяти частью первого участка памяти 6, т.е. в этом примере - одной из зон 38 и 42 памяти, указанных в данных таблицы страниц (т.е. данными 44 флага P/U и данными 43 флага R/W), для адреса, по которому предпринимается попытка доступа для считывания. Если адрес памяти не находится в первом участке, то операция выборки команды может быть разрешена, и происходит переход на этап 60. Однако если предпринимается попытка выполнить операцию выборки команды из первого участка 38 и 42 памяти, то происходит переход на этап 66, где рассматриваемый доступ запрещается.

Если доступ к памяти запрещается, например, на этапе 56 или 66, то может инициироваться прекращение работы с памятью, в результате чего выполняется программный код обработки непредвиденной ситуации в виде прекращения работы с памятью. Этот тип обработки прекращения работы с памятью знаком специалистам в данной области техники.

На фиг.3 схематично показаны многочисленные аппаратные режимы работы процессора 8 (или режимы, эмулирующие такие аппаратные режимы при реализации в виде виртуальной машины). В этом примере показаны только два режима, а именно привилегированный режим и пользовательский режим. Понятно, что представленные способы могут быть использованы с процессорами, имеющими большее число режимов. Привилегированный режим разрешает доступ только для считывания или доступ для считывания/записи к адресным зонам памяти, помеченным как привилегированные. Привилегированный режим также позволяет выполнять доступ только для считывания или доступ для считывания/записи по маршруту передачи данных к адресным зонам памяти, помеченным как зоны, к которым можно выполнять доступ для считывания/записи в пользовательском режиме. При нахождении в привилегированном режиме, если установлен флаг безопасности в регистре 46, исполнение команд из памяти, доступной для считывания/записи в пользовательском режиме, не разрешается. При этом в привилегированном режиме при доступе только для считывания или доступе для считывания/записи к указанной выше привилегированной памяти разрешается выполнение команд, выбранных из этой привилегированной памяти.

При работе в пользовательском режиме не разрешается доступ только для считывания или доступ для считывания/записи к адресным зонам памяти, помеченным как адресные зоны памяти для привилегированного режима. При этом разрешается доступ только для считывания и доступ для считывания/записи к адресным зонам памяти, помеченным как адресные зоны памяти для пользовательского режима.

Понятно, что в типичном случае в разных аппаратных режимах будут выполняться разные типы программ. Более надежные программы, например, программа ядра операционной системы, в типичном случае будут работать в привилегированном режиме. Прикладные программы в типичном случае будут работать в пользовательском режиме.

Флаг безопасности в регистре 46, который управляет тем, разрешается ли исполнение в привилегированном режиме команд, хранящихся в памяти, в которую можно производить запись в пользовательском режиме, устанавливается под управлением команд программы. Регистр 46 может быть выполнен в виде регистра сопроцессора, запись в который, чтобы установить флаг безопасности, можно производить с использованием команды сопроцессора. Чтобы сохранить безопасность механизма, обеспечиваемого при использовании флага безопасности, флаг безопасности может быть записан только при нахождении в привилегированном режиме. Это предотвращает вредоносный или, по меньшей мере, неавторизованный сброс флага безопасности программой, выполняемой в пользовательском режиме, в результате чего разрешается исполнение в привилегированном режиме команд, хранящихся в памяти, запись в которую можно производить в пользовательском режиме.

На фиг.4 показана реализация в виде виртуальной машины, которую можно использовать. Хотя в ранее описанных вариантах настоящее изобретение реализовано в виде устройства и способа для работы конкретных аппаратных средств обработки, поддерживающих рассматриваемые способы, также можно предложить различные варианты реализации аппаратных средств в виде так называемой виртуальной машины. Эти варианты реализации в виде виртуальной машины исполняются в ведущем процессоре 530, работающем под управлением ведущей операционной системы 520, поддерживающей программу 510 виртуальной машины. Как правило, для обеспечения вариантов реализации в виде виртуальной машины требуются большие мощные процессоры, которые работают с приемлемой скоростью, но в определенных ситуациях такой подход может быть оправдан, например, если требуется выполнить код, понимаемый другим процессором, по причинам обеспечения совместимости или повторного использования. Программа 510 виртуальной машины предоставляет прикладной программе 500 интерфейс прикладной программы, идентичный интерфейсу прикладной программы, который был бы предоставлен реальными аппаратными средствами, представляющими собой устройство, моделируемое программой 510 виртуальной машины. Таким образом, команды, включая описанное выше управление доступом к памяти, могут выполняться из прикладной программы 500 с использованием программы 510 виртуальной машины для моделирования их взаимодействия с аппаратными средствами виртуальной машины.

1. Устройство для обработки данных, содержащее:- процессор, способный реагировать на поток команд программы для выполнения операций обработки; и- схему управления памятью, соединенную с упомянутым процессором и памятью и выполненную с возможностью управлять доступом упомянутого процессора к упомянутой памяти,причем:упомянутый процессор имеет множество аппаратных режимов работы, включающих в себя, по меньшей мере, первый режим и второй режим;упомянутая схема управления памятью управляет доступом к упомянутой памяти таким образом, что:- (i) при нахождении упомянутого процессора в упомянутом первом режиме, упомянутая схема управления памятью разрешает доступ для записи к первому участку упомянутой памяти и не разрешает, по меньшей мере, доступ для записи ко второму участку упомянутой памяти, и- (ii) при нахождении упомянутого процессора в упомянутом втором режиме, упомянутая схема управления памятью разрешает доступ для записи к упомянутому первому участку упомянутой памяти и разрешает доступ для записи ко второму участку упомянутой памяти; иупомянутая схема управления памятью способна реагировать на флаг безопасности, имеющий установленное значение, чтобы предоставлять упомянутому процессору в упомянутом первом режиме право, не предоставленное упомянутому процессору в упомянутом втором режиме посредством предотвращения считывания упомянутым процессором из упомянутого первого участка упомянутой памяти команд программы для исполнения упомянутым процессором в упомянутом втором режиме,причем, если упомянутый флаг безопасности имеет упомянутое установленное значение, а упомянутый процессор находится в упомянутом втором режиме, то упомянутая схема управления памятью разрешает упомянутому процессору считывать значения данных из упомянутого первого участка упомянутой памяти.

2. Устройство по п. 1, в котором упомянутый процессор считывает команды программы для исполнения из упомянутого второго участка упомянутой памяти.

3. Устройство по любому из пп. 1 или 2, в котором упомянутая схема управления памятью способна реагировать на данные управления для идентификации одной или более адресных зон памяти в упомянутой памяти как части упомянутого первого участка и одной или более адресных зон памяти в упомянутой памяти как части упомянутого второго участка.

4. Устройство по любому из пп. 1 или 2, в котором упомянутый первый режим является пользовательским режимом для исполнения прикладных программ, а упомянутый второй режим является привилегированным режимом для исполнения, по меньшей мере, программы ядра операционной системы.

5. Устройство по любому из пп. 1 или 2, в котором упомянутая схема управления памятью содержит одно из следующего:- блок управления памятью; и- блок защиты памяти.

6. Устройство по любому из пп. 1 или 2, в котором упомянутый флаг безопасности записывают под управлением команд программы, когда упомянутый процессор находится в упомянутом втором режиме, и упомянутый флаг безопасности не может быть записан под управлением команд программы, когда упомянутый процессор находится в упомянутом первом режиме.

7. Устройство для обработки данных, содержащее:- процессорное средство для выполнения операций обработки в ответ на поток команд программы; и- схему средства управления памятью, соединенную с упомянутым процессорным средством и с запоминающим средством для хранения данных, для управления доступом упомянутого процессорного средства к упомянутому запоминающему средству,причем:упомянутое процессорное средство имеет множество аппаратных режимов работы, включающих в себя, по меньшей мере, первый режим и второй режим;упомянутое средство управления памятью управляет доступом к упомянутому запоминающему средству таким образом, что:- (i) при нахождении упомянутого процессорного средства в упомянутом первом режиме, упомянутое средство управления памятью разрешает доступ для записи к первому участку упомянутого запоминающего средства и не разрешает, по меньшей мере, доступ для записи ко второму участку упомянутого запоминающего средства, и- (ii) при нахождении упомянутого процессорного средства в упомянутом втором режиме, упомянутое средство управления памятью разрешает доступ для записи к упомянутому первому участку упомянутого запоминающего средства и разрешает доступ для записи ко второму участку упомянутого запоминающего средства; иупомянутое средство управления памятью способно реагировать на флаг безопасности, имеющий установленное значение, чтобы предоставлять упомянутому процессору в упомянутом первом режиме право, не предоставленное упомянутому процессору во втором режиме посредством предотвращения считывания упомянутым процессорным средством из упомянутого первого участка упомянутого запоминающего средства команд программы для исполнения упомянутым процессорным средством в упомянутом втором режиме,причем, если упомянутый флаг безопасности имеет упомянутое установленное значение, а упомянутое процессорное средство находится в упомянутом втором режиме, то упомянутое средство управления памятью разрешает упомянутому процессорному средству считывать значения данных из упомянутого первого участка упомянутого запоминающего средства.

8. Способ обработки данных, причем упомянутый способ содержит этапы, на которых:- выполняют операции обработки процессором в ответ на поток команд программы; и- управляют доступом упомянутого процессора к памяти с использованием схемы управления памятью, соединенной с упомянутым процессором и упомянутой памятью,причем:упомянутый процессор имеет множество аппаратных режимов работы, включающих в себя, по меньшей мере, первый режим и второй режим;упомянутая схема управления памятью управляет доступом к упомянутой памяти таким образом, что:- (i) при нахождении упомянутого процессора в упомянутом первом режиме, упомянутая схема управления памятью разрешает доступ для записи к первому участку упомянутой памяти и не разрешает, по меньшей мере, доступ для записи ко второму участку упомянутой памяти, и- (ii) при нахождении упомянутого процессора в упомянутом втором режиме, упомянутая схема управления памятью разрешает доступ для записи к упомянутому первому участку упомянутой памяти и разрешает доступ для записи ко второму участку упомянутой памяти; иупомянутая схема управления памятью способна реагировать на флаг безопасности, имеющий установленное значение, чтобы предоставлять упомянутому процессору в упомянутом первом режиме право, не предоставленное упомянутому процессору в упомянутом втором режиме посредством предотвращения считывания упомянутым процессором из упомянутого первого участка упомянутой памяти команд программы для исполнения упомянутым процессором в упомянутом втором режиме,причем, если упомянутый флаг безопасности имеет упомянутое установленное значение, а упомянутый процессор находится в упомянутом втором режиме, то упомянутая схема управления памятью разрешает упомянутому процессору считывать значения данных из упомянутого первого участка упомянутой памяти.

9. Способ по п.8, в котором упомянутый процессор считывает команды программы для исполнения из упомянутого второго участка упомянутой памяти.

10. Способ по любому из пп. 8 или 9, в котором упомянутая схема управления памятью способна реагировать на данные управления для идентификации одной или более адресных зон памяти в упомянутой памяти как части упомянутого первого участка и одной или более адресных зон памяти в упомянутой памяти как части упомянутого второго участка.

11. Способ по любому из пп. 8 или 9, в котором упомянутый первый режим является пользовательским режимом для исполнения прикладных программ, а упомянутый второй режим является привилегированным режимом для исполнения, по меньшей мере, программы ядра операционной системы.

12. Способ по любому из пп. 8 или 9, в котором упомянутая схема управления памятью содержит одно из следующего:- блок управления памятью; и- блок защиты памяти.

13. Устройство для обработки данных, имеющее схему обработки, управляемую компьютерной программой, чтобы обеспечить устройство в виде виртуальном машины для выполнения способа по п.8.