Способ сверточного турбокодирования и устройство для реализации способа кодирования

Иллюстрации

Показать всеИзобретение относится к способу кодирования в системе беспроводной мобильной связи. Более конкретно, настоящие изобретение относится к способу сверточного турбокодирования (СТС) и устройству для реализации способа. Технический результат заключается в повышении надежности кодирования при отображении по битам модуляции высшего порядка изображения. Способ для CTC включает в себя этапы кодирования информационных битов A и B с использованием компонентного кодера и вывода последовательностей Y1 и W1 четности, перемежения информационных битов A и B с использованием модуля CTC-перемежения, чтобы получать информационные биты C и D, и кодирования перемеженных информационных битов C и D с использованием компонентного кодера, чтобы получать последовательности Y2 и W2 четности, перемежения информационных битов A и B, последовательностей Y1 и W1 четности и последовательностей Y2 и W2 четности, соответственно, при этом биты в по меньшей мере одной из группы битов, состоящей из информационных битов A и B, группы битов, состоящей из последовательностей Y1 и W1, и группы битов, состоящей из последовательностей Y2 и W2, попеременно отображаются в биты точек совокупности с высокой надежностью и низкой надежностью, и прокалывания результата перемежения, чтобы получать кодированные битовые последовательности. 4 н. и 8 з.п. ф-лы, 7 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к способу кодирования в системе беспроводной мобильной связи. Более конкретно, настоящее изобретение относится к способу сверточного турбокодирования (CTC) и устройству для реализации способа.

УРОВЕНЬ ТЕХНИКИ

Мобильный стандарт общемировой совместимости широкополосного беспроводного доступа (WiMAX) является технологией широкополосного доступа для реализации доступа на "последнем километре" посредством использования беспроводного режима вместо использования проводного режима. Она интегрирует мобильные устройства со стационарной широкополосной сетью и предоставляет удобное и высокоскоростное мобильное широкополосное соединение посредством использования технологии широкополосного беспроводного доступа и гибкой сетевой структуры. WiMAX-технология основана на стандартах Института инженеров по электротехнике и радиоэлектронике (IEEE) 802.16, которые предлагаются для полос частот микроволнового и миллиметрового диапазона. WiMAX-стандарт для мобильных устройств предложен после того, как WiMAX-стандарт для стационарных устройств IEEE 802.16d предложен. WiMAX для мобильных устройств нацелен на то, чтобы поддерживать мобильность широкополосного доступа посредством базирования на исследовании, начатом в ходе стандартизации WiMAX-стандарта для стационарных устройств. Сверточный турбокод (CTC) является классом турбокода с использованием нескольких схем сверточного кодирования. CTC включается в стандарты IEEE 802.16 и цифровой широковещательной передачи видео на основе обратного канала через спутник (DVB-RCS) вследствие их высокой эффективности коррекции ошибок.

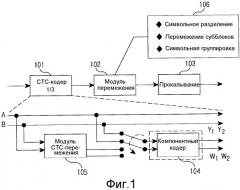

Фиг.1 иллюстрирует CTC-кодер согласно предшествующему уровню техники. Ссылаясь на фиг.1, CTC-кодер может содержать CTC-кодер 101 1/3, модуль 102 перемежения и модуль 103 прокалывания (прореживания). Как показано на фиг.1, входные информационные биты вводятся в CTC-кодер 101 1/3. Здесь, число кодированных выходных информационных битов и битов четности в три раза превышает число информационных битов. Кодированные данные затем перемежаются посредством модуля 102 перемежения. Модуль 103 прокалывания прокалывает перемеженные данные на основе скорости передачи, т.е. он выбирает биты данных, которые должны быть переданы, и получает кодированную битовую последовательность так, чтобы завершать процесс кодирования.

Более конкретно, в CTC-кодере 101 1/3, используется двухбинарный кольцевой рекурсивный систематический сверточный (CRSC) код. Как показано на фиг.1, CTC-кодер 101 1/3 может содержать модуль 105 CTC-перемежения и компонентный кодер 104. Здесь, вводы A и B в модуль 105 CTC-перемежения представляют входные информационные биты, которые кодируются два раза. Во-первых, двухбинарное CRSC-кодирование выполняется для информационных битов A и B. Таким образом, набор информационных битов Ai и Bi одновременно вводится в компонентный кодер 104 для кодирования, и получаются последовательности Yi и Wi четности. Информационные биты A и B также перемежаются посредством модуля 105 CTC-перемежения. Второй процесс компонентного кодирования затем выполняется для перемеженных последовательностей. Таким образом, перемеженные информационные биты Aj и Bj одновременно вводятся в компонентный кодер 104 так, чтобы получать последовательности Y2 и W2 четности. Каждый кодовый блок, вводимый в компонентный кодер 104, содержит k информационных битов или N пар информационных битов, т.е. k=2×N, где k является кратным 8, а N является кратным 4, и 32<N<4096.

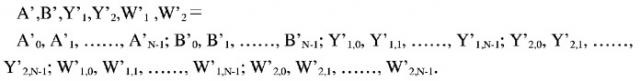

Как показано в блоке 106, модуль 102 перемежения может содержать модуль символьного разделения, модуль перемежения субблоков и модуль символьной группировки. Модуль символьного разделения используется для того, чтобы выделять информационные биты и кодированные биты для 6 субблоков, которыми являются поочередно A, B, Y1, Y2, W1 и W2, описанные выше. Модуль перемежения субблоков используется для того, чтобы перемежать эти 6 субблоков, соответственно, в каждом из субблоков. Порядок перемежения является идентичным для каждого субблока. Допустим, что после того, как перемежение субблоков выполнено, соответственно, для блоков A, B, Y1, Y2, W1 и W2, полученные битовые последовательности обозначаются как A', B', Y'1, Y'2, W'1 и W'2, затем

Фиг.2 иллюстрирует операции перемежения субблоков согласно предшествующему уровню техники. Ссылаясь на фиг.2, модуль символьного разделения разделяет кодированные биты на субблоки A, B, Y1, Y2, W1 и W2 на этапе 201. Перемежение субблоков выполняет операцию перемежения для субблоков A, B, Y1, Y2, W1 и W2 на этапе 202, и модуль символьной группировки группирует перемеженные субблоки на этапе 203. В данном документе субблоки A и B выводятся посредством модуля символьной группировки, и два субблока Y1 и Y2 и субблока W1 и W2 попеременно выводятся. После символьной группировки выходными последовательностями являются

В CTC предшествующего уровня техники, не принимается во внимание надежность по битам в модуляции высшего порядка. Здесь, надежность означает среднее расстояние, между точкой совокупности, в которой определенный отображенный бит равен "0", и точкой совокупности, в которой этот отображенный бит равен "1" в созвездии модуляции. Чем больше расстояние, тем больше надежность отображенного бита.

В системе мобильной связи, чтобы повышать скорость передачи данных без увеличения полосы пропускания, может применяться схема квадратурной амплитудной модуляции M-го порядка (M-QAM). Тем не менее, модуляция высшего порядка является модуляцией с неравномерной защитой от ошибок. Для M>4, соответствующие биты, отображенные в M-QAM-символы, имеют различные частоты ошибок по битам (BER). Внутренние точки совокупности имеют меньше энергии и тем самым могут легче подвергаться замиранию. Соответственно, биты, составляющие эти символы, являются менее надежными. Напротив, биты, составляющие точки, находящиеся вне совокупности, являются более надежными.

Фиг.3 иллюстрирует надежность побитового отображения модуляции высшего порядка согласно предшествующему уровню техники. Ссылаясь на фиг.3, порядком отображения битов является i1i2q1q2 с i1=0 и i1=1, соответственно, согласно точкам совокупности в правой полуплоскости и в левой полуплоскости, и i2=0 и i2=1, соответственно, согласно точкам совокупности в середине и по двум сторонам совокупности. Таким образом, среднее расстояние между точками совокупности, где i1=1 и где i1=0, превышает расстояние согласно i2. Следовательно, в приемной стороне, i1 имеет более высокую надежность, чем i2.

Фиг.4 иллюстрирует компонентный кодер CTC-кодера 1/3, реализующего двухбинарное CRSC-кодирование согласно предшествующему уровню техники. Ссылаясь на фиг.4, когда CTC выполняется, входной бит Ai 401 и входной бит Bi 402 используются в качестве набора вводов в CTC-кодер 1/3, и биты Yi и Wi четности реализуют комбинированную информацию из информационного бита Ai и информационного бита Bi. В этом типе двухбинарного кодирования бит Ai и бит Bi должны рассматриваться в целом и обрабатываться как единица группы. В схеме CTC предшествующего уровня техники, если бит Ai отображается в бит с высокой надежностью, бит Bi также отображается в бит с высокой надежностью. Помимо этого, если бит Ai отображается в бит с низкой надежностью, бит Bi также отображается в бит с низкой надежностью. Информационные биты в последовательности A и информационные биты в последовательности B, которые одновременно вводятся в компонентный кодер, как считается, составляют группу битов. Следовательно, с точки зрения единицы группы (Ai, Bi), различные единицы группы имеют неравномерную надежность по битам. Некоторые единицы группы имеют высокую надежность, тогда как некоторые имеют низкую надежность.

Соответственно, в технологии предшествующего уровня техники существует проблема в том, что комбинирование Ai и Bi для побитового отображения не принимается во внимание. Помимо этого, в технологии предшествующего уровня техники существует проблема в том, что надежность по битам модуляции высшего порядка не принимается во внимание во время отображения.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Решение задачи

Аспект настоящего изобретения заключается в том, чтобы разрешать, по меньшей мере, вышеуказанные проблемы и/или недостатки и предоставлять, по меньшей мере, преимущества, описанные ниже. Согласно аспекту настоящего изобретения, предусмотрен способ сверточного турбокодирования (CTC). Способ включает в себя этапы кодирования информационных битов A и B с использованием компонентного кодера и вывода последовательностей Y1 и W1 четности, перемежения информационных битов A и B с использованием модуля CTC-перемежения, чтобы получать информационные биты C и D, и кодирования перемеженных информационных битов C и D с использованием компонентного кодера, чтобы получать последовательности Y2 и W2 четности, перемежения информационных битов A и B, последовательностей Y1 и W1 четности и последовательностей Y2 и W2 четности, соответственно, при этом биты, по меньшей мере, в одной из группы битов, состоящей из информационных битов A и B, группы битов, состоящей из последовательностей Y1 и W1, и группы битов, состоящей из последовательностей, Y2 и W2 попеременно отображаются в биты точек совокупности с высокой надежностью и низкой надежностью, и прокалывания результата перемежения, чтобы получать кодированные битовые последовательности.

Согласно другому аспекту настоящего изобретения, предусмотрено устройство для CTC. Устройство включает в себя компонентный кодер для кодирования информационных битов A и B и вывода последовательностей Y1 и W1 четности, модуль CTC-перемежения для перемежения информационных битов A и B, чтобы получать новые информационные биты C и D, и для предоставления перемеженных информационных битов C и D в компонентный кодер для кодирования, чтобы получать последовательности Y2 и W2 четности, модуль перемежения для перемежения информационных битов A и B, последовательностей Y1 и W1 четности и последовательностей Y2 и W2 четности, соответственно, при этом биты, по меньшей мере, в одной из группы битов, состоящей из информационных битов A и B, группы битов, состоящей из последовательностей Y1 и W1, и группы битов, состоящей из последовательностей, Y2 и W2 попеременно отображаются в биты точек совокупности с высокой надежностью и низкой надежностью, и модуль прокалывания для прокалывания выходных последовательностей из модуля перемежения, чтобы получать кодированные битовые последовательности.

Согласно еще одному аспекту настоящего изобретения, предусмотрено устройство для турбокодера. Устройство включает в себя перемеженный субблок A информации, перемеженный субблок B информации, при этом субблоки A и B информации обходятся, побитово мультиплексированную последовательность четности перемеженных последовательностей субблоков Y1 и Y2, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков Y1 и Y2 состоит из первого выводимого бита из модуля перемежения субблоков Y1, первого выводимого бита из модуля перемежения субблоков Y2, второго выводимого бита из модуля перемежения субблоков Y1 и второго выводимого бита из модуля перемежения субблоков Y2, и побитово мультиплексированную последовательность четности перемеженных последовательностей субблоков W2 и W1, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков W2 и W1 состоит из первого выводимого бита из модуля перемежения субблоков W2, первого выводимого бита из модуля перемежения субблоков W1, второго выводимого бита из модуля перемежения субблоков W2 и второго выводимого бита из модуля перемежения субблоков W1.

Согласно еще одному другому аспекту настоящего изобретения, Ai и Bi комбинируются для побитового отображения. Кроме того, надежность по битам модуляции высшего порядка принимается во внимание во время отображения, так что надежность кодирования повышается.

Другие аспекты, преимущества и характерные признаки изобретения должны становиться очевидными специалистам в данной области техники из последующего подробного описания, которое, при рассмотрении вместе с прилагаемыми чертежами, раскрывает примерные варианты осуществления изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеуказанные и другие примерные аспекты, признаки и преимущества примерных вариантов осуществления настоящего изобретения должны становиться более понятными из последующего подробного описания, рассматриваемого вместе с прилагаемыми чертежами, из которых:

Фиг.1 иллюстрирует сверточный турбокод (CTC) согласно предшествующему уровню техники;

Фиг.2 иллюстрирует операции перемежения субблоков согласно предшествующему уровню техники;

Фиг.3 иллюстрирует надежность побитового отображения модуляции высшего порядка согласно предшествующему уровню техники;

Фиг.4 иллюстрирует компонентный кодер CTC-кодера 1/3, реализующего двухбинарное кольцевое рекурсивное систематическое сверточное (CRSC) кодирование согласно предшествующему уровню техники;

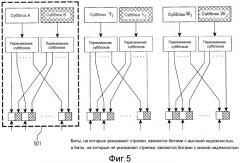

Фиг.5 иллюстрирует операции повторного отображения согласно первому примерному варианту осуществления настоящего изобретения;

Фиг.6 иллюстрирует операции повторного отображения согласно второму примерному варианту осуществления настоящего изобретения; и

Фиг.7 иллюстрирует операции повторного отображения согласно третьему примерному варианту осуществления настоящего изобретения.

Следует отметить, что на всех чертежах аналогичные номера ссылок используются для того, чтобы иллюстрировать идентичные или аналогичные элементы, признаки и структуры.

НАИЛУЧШИЙ РЕЖИМ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Последующее описание со ссылкой на прилагаемые чертежи предоставляется для того, чтобы помогать в полном понимании примерных вариантов осуществления изобретения, как задано посредством формулы изобретения и ее эквивалентов. Оно включает в себя различные сведения, чтобы помогать в этом понимании, но они должны рассматриваться просто как примерные. Соответственно, специалисты в данной области техники должны признавать, что различные изменения и модификации вариантов осуществления, описанных в данном документе, могут осуществляться без отступления от сущности и объема изобретения. Помимо этого, описания хорошо известных функций и структур опущены для ясности и краткости.

Термины и слова, используемые в последующем описании и формуле изобретения, не ограничены библиографическими значениями, а используются автором изобретения просто для того, чтобы предоставлять ясное и последовательное понимание изобретения. Соответственно, специалистам в данной области техники должно быть очевидным, что последующее описание примерных вариантов осуществления настоящего изобретения предоставляется только для цели иллюстрации, а не для цели ограничения изобретения, как задано посредством прилагаемой формулы изобретения и ее эквивалентов.

Следует понимать, что формы единственного числа включают в себя несколько объектов ссылки, если контекст явно не предписывает иное. Таким образом, например, ссылка на "поверхность компонента" включает в себя ссылку на одну или более таких поверхностей.

Примерные варианты осуществления настоящего изобретения предоставляют усовершенствования модуля символьной группировки, к примеру модуля 102 перемежения сверточного турбокода (CTC), проиллюстрированного на фиг.1. Далее предполагается, что выводами из модуля перемежения субблоков в модуле перемежения являются последовательности A', B', Y'1, Y'2, W'1 и W'2.

Согласно примерной схеме, сначала отображается последовательность A'. Затем обнаруживается соответствующий бит в последовательности B', который вводится в CTC-кодер одновременно с каждым битом в последовательности A'. Бит, который вводится в CTC-кодер одновременно с A'i, обозначается как B'j. B'j упоминается как бит соответствия единице группы A'j. Затем последовательность B' отображается. Если A'j отображается в бит с высокой надежностью, его бит B'j соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если A'j отображается в бит с низкой надежностью, его бит B'j соответствия единице группы должен отображаться в бит с высокой надежностью.

Кроме того, согласно второй примерной схеме, может сначала отображаться последовательность Y'1. Затем соответствующий бит в последовательности W'1, который выводится из CTC-кодера одновременно с каждым битом в последовательности Y'1, обнаруживается. Бит четности, который выводится из CTC-кодера одновременно с Y'1,i, обозначается как W'1,i. W'1,i упоминается как единица группы, соответствующая единице Y'1,i. Затем, последовательность W'1 отображается. Если Y'1,i отображается в бит с высокой надежностью, его бит соответствия единице группы W'1,j должен отображаться в бит с низкой надежностью. Кроме того, если Y'1,i отображается в бит с низкой надежностью, его бит соответствия единице группы W'1,j должен отображаться в бит с высокой надежностью. Биты четности в последовательности Y'1 и биты в последовательности W'1, которые одновременно выводятся из компонентного кодера, составляют группу битов.

Кроме того, согласно третьей примерной схеме, последовательность Y'2 также может отображаться сначала. Затем, соответствующий бит в последовательности W'2, который выводится из CTC-кодера одновременно с каждым битом в последовательности Y'2, обнаруживается. Бит четности, который выводится из CTC-кодера одновременно с Y'2,i, обозначается как W'2,j. W'2,j упоминается как бит соответствия единице группы Y'2,i. Затем последовательность W'2 отображается. Если Y'2,i отображается в бит с высокой надежностью, его бит соответствия единице группы W'2,j должен отображаться в бит с низкой надежностью. Кроме того, если Y'2,i отображается в бит с низкой надежностью, его бит соответствия единице группы W'2,j должен отображаться в бит с высокой надежностью. Биты четности в последовательности Y'2 и биты в последовательности W'2, которые одновременно выводятся из компонентного кодера, составляют группу битов.

Вышеуказанные три примерных схемы могут быть реализованы независимо посредством комбинирования любых двух из них или посредством комбинирования их всех. Согласно результату моделирования, наименьшее повышение производительности получается посредством применения только второй или третьей схем. Если как вторая, так и третья схемы применяются, достигается небольшое повышение производительности. Когда только первая схема применяется, производительность превосходит производительность, полученную посредством применения и второй, и третьей схем. Если применяются первая, вторая и третья схемы, в общем, должна получаться наилучшая производительность.

На основе стандарта в реализации Института инженеров по электротехнике и радиоэлектронике (IEEE) 802.16e, операции перемежения субблоков согласно примерному варианту осуществления настоящего изобретения описываются ниже со ссылкой на фиг.5.

Фиг.5 иллюстрирует операции повторного отображения согласно первому примерному варианту осуществления настоящего изобретения.

На фиг.5, предполагается, что выводами из модуля перемежения субблоков в модуле перемежения являются последовательности . Здесь, конкретно компонуются как

Ссылаясь на фиг.5, как показано в блоке 501, сначала отображается последовательность A'. На основе стандарта IEEE 802.16e, соответствующим битом в последовательности B', который вводится в CTC-кодер одновременно с A'i, является B'i. Затем последовательность B' отображается. Если A'i отображается в бит с высокой надежностью, его бит B'i соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если A'i отображается в бит с низкой надежностью, его бит B'i соответствия единице группы должен отображаться в бит с высокой надежностью.

Конечно, вышеуказанные операции также могут выполняться для группы битов, состоящей из последовательностей Y'i и W'i, и группы битов, состоящей из последовательностей Y'2 и W'2, соответственно.

Фиг.6 иллюстрирует операции повторного отображения согласно второму примерному варианту осуществления настоящего изобретения.

Ссылаясь на фиг.6, сначала отображается последовательность Y'1. В стандарте IEEE 802.16e, битом четности, который выводится из CTC-кодера одновременно с Y'1,i, является W1,i. Затем отображается последовательность W'1. Если Y'1,i отображается в бит с высокой надежностью, его бит W'1,i соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если Y'1,i отображается в бит с низкой надежностью, его бит W'1,i соответствия единице группы должен отображаться в бит с высокой надежностью.

Затем последовательность Y'2 отображается. На основе стандарта IEEE 802.16e, битом четности, который выводится из CTC-кодера одновременно с Y'2,i, является W'2,i. Затем, последовательность W'2 отображается. Если Y'2,i отображается в бит с высокой надежностью, его бит W'2,i соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если Y'2,i отображается в бит с низкой надежностью, его бит W'2,i соответствия единице группы должен отображаться в бит с высокой надежностью.

Конечно, операция альтернативного отображения может выполняться сначала для битов в группе битов, состоящей из последовательностей A' и B', и затем в группе битов, состоящей из последовательностей Y'1 и W'1, или группе битов, состоящей из последовательностей Y'2 и W2, соответственно.

Третий примерный вариант осуществления настоящего изобретения, который комбинирует первый и второй примерные варианты осуществления настоящего изобретения, описывается ниже со ссылкой на фиг.7.

Фиг.7 иллюстрирует операции повторного отображения согласно третьему примерному варианту осуществления настоящего изобретения.

Ссылаясь на фиг.7, сначала может отображаться последовательность A'. Соответствующим битом в последовательности B', который вводится в CTC-кодер одновременно с A'i, является B'i. Затем, отображается последовательность B'. Если A'i отображается в бит с высокой надежностью, его бит B'i соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если A'i отображается в бит с низкой надежностью, его бит соответствия единице группы B'i должен отображаться в бит с высокой надежностью. Кроме того, как показано на фиг.7, последовательность Y'i отображается. В стандарте IEEE 802.16e, битом четности, который выводится из CTC-кодера одновременно с Y'1,i, является W'1,i. Затем, отображается последовательность W'1. Если Y'1,i отображается в бит с высокой надежностью, его бит W'1,i соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если Y'1,i отображается в бит с низкой надежностью, его бит W'1,i соответствия единице группы должен отображаться в бит с высокой надежностью. Затем, отображается последовательность Y'2. В стандарте IEEE 802.16e, битом четности, который выводится из CTC-кодера одновременно с Y'2,i, является W'2,i. Затем отображается последовательность W'2. Если Y'2,i отображается в бит с высокой надежностью, его бит W'2,i соответствия единице группы должен отображаться в бит с низкой надежностью. Кроме того, если Y'2,i отображается в бит с низкой надежностью, его бит W'2,i соответствия единице группы должен отображаться в бит с высокой надежностью.

На фиг.7 биты с высокой надежностью указываются посредством битов, на которые указывают стрелки. Если биты с высокой надежностью являются нечетными битами, а биты с низкой надежностью являются четными битами, как показано на фиг.7, то выходные последовательности являются

Хотя изобретение показано и описано со ссылкой на его конкретные примерные варианты осуществления, специалисты в данной области техники должны понимать, что различные изменения по форме и содержанию могут осуществляться без отступления от сущности и объема изобретения, заданного посредством прилагаемой формулы изобретения и ее эквивалентов.

1. Способ кодирования содержащий этапы, на которых:a) кодируют информационные биты А и В с использованием компонентного кодера и выводят последовательности Y1 и W1 четности;b) перемежают информационные биты А и В с использованием модуля СТС-перемежения (СТС - сверточное турбокодирование), чтобы получать информационные биты С и D, и кодируют перемеженные информационные биты С и D с использованием компонентного кодера, чтобы получать последовательности Y2 и W2 четности;c) перемежают информационные биты А и В, последовательности Y1 и W1 четности и последовательности Y2 и W2 четности, соответственно; иd) выводят перемеженный субблок А информации, перемеженный субблок В информации, побитово мультиплексированную последовательность перемеженных последовательностей субблоков Y1 и Y2, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков Y1 и Y2 состоит из первого выводимого бита из модуля перемежения субблоков Y1, первого выводимого бита из модуля перемежения субблоков Y2, второго выводимого бита из модуля перемежения субблоков Y1 и второго выводимого бита из модуля перемежения субблоков Y2 по порядку, ипобитово мультиплексированную последовательность перемеженных последовательностей субблоков W2 и W1, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков W2 и W1 состоит из первого выводимого бита из модуля перемежения субблоков W2, первого выводимого бита из модуля перемежения субблоков W1, второго выводимого бита из модуля перемежения субблоков W2 и второго выводимого бита из модуля перемежения субблоков W1 по порядку.

2. Способ кодирования по п.1,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с низкой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с высокой надежностью,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с высокой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с низкой надежностью,в котором соответствующий бит перемеженной последовательности субблока W1 отображается в бит точки совокупности с низкой надежностью, если бит перемеженного субблока Y1 отображается в бит точки совокупности с высокой надежностью, ив котором соответствующий бит перемеженной последовательности субблока W1 отображается в бит точки совокупности с высокой надежностью, если бит перемеженного субблока Y1 отображается в бит точки совокупности с низкой надежностью.

3. Способ кодирования по п.1, в котором перемеженные информационные биты А и В обходят при побитовом мультиплексировании последовательностей четности.

4. Устройство кодирования, содержащее:- компонентный кодер для кодирования информационных битов А и В и вывода последовательностей Y1 и W1 четности;- модуль СТС-перемежения (СТС - сверточное турбокодирование) для перемежения информационных битов А и В, чтобы получать новые информационные биты С и D, и для подачи перемеженных информационных битов С и D в компонентный кодер для кодирования, чтобы получать последовательности Y2 и W2 четности; и- модуль перемежения для перемежения информационных битов А и В, последовательностей Y1 и W1 четности и последовательностей Y2 и W2 четности, соответственно, и для вывода:перемеженного субблока А информации,перемеженного субблока В информации,побитово мультиплексированной последовательности перемеженных последовательностей субблоков Y1 и Y2, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков Y1 и Y2 состоит из первого выводимого бита из модуля перемежения субблоков Y1, первого выводимого бита из модуля перемежения субблоков Y2, второго выводимого бита из модуля перемежения субблоков Y1 и второго выводимого бита из модуля перемежения субблоков Y2 по порядку, ипобитово мультиплексированной последовательности перемеженных последовательностей субблоков W2 и W1, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков W2 и W1 состоит из первого выводимого бита из модуля перемежения субблоков W2, первого выводимого бита из модуля перемежения субблоков W1, второго выводимого бита из модуля перемежения субблоков W2 и второго выводимого бита из модуля перемежения субблоков W1 по порядку.

5. Устройство кодирования по п.4,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с низкой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с высокой надежностью,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с высокой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с низкой надежностью,в котором соответствующий бит перемеженной последовательности субблока W1 отображается в бит точки совокупности с низкой надежностью, если бит перемеженного субблока Y1 отображается в бит точки совокупности с высокой надежностью, ив котором соответствующий бит перемеженной последовательности субблока W1 отображается в бит точки совокупности с высокой надежностью, если бит перемеженного субблока Y1 отображается в бит точки совокупности с низкой надежностью.

6. Устройство кодирования по п.4, в котором перемеженные информационные биты А и В обходят при побитовом мультиплексировании последовательности четности.

7. Способ для турбокодера, причем способ содержит этапы, на которых:принимают по меньшей мере одним модулем перемежения субблоков субблок А информации, субблок В информации, последовательность четности субблока Y1, последовательность четности субблока Y2, последовательность четности субблока W2 и последовательность четности субблока W1; ивыводят по меньшей мере одним модулем перемежения субблоковперемеженный субблок А информации,перемеженный субблок В информации,побитово мультиплексированную последовательность перемеженных последовательностей субблоков Y1 и Y2, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков Y1 и Y2 состоит из первого выводимого бита из модуля перемежения субблоков Y1, первого выводимого бита из модуля перемежения субблоков Y2, второго выводимого бита из модуля перемежения субблоков Y1 и второго выводимого бита из модуля перемежения субблоков Y2 по порядку, ипобитово мультиплексированную последовательность перемеженных последовательностей субблоков W2 и W1, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков W2 и W1 состоит из первого выводимого бита из модуля перемежения субблоков W2, первого выводимого бита из модуля перемежения субблоков W1, второго выводимого бита из модуля перемежения субблоков W2 и второго выводимого бита из модуля перемежения субблоков W1 по порядку.

8. Способ по п.7,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с низкой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с высокой надежностью,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с высокой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с низкой надежностью,в котором соответствующий бит перемеженной последовательности субблока W1 отображается в бит точки совокупности с низкой надежностью, если бит перемеженного субблока Y1 отображается в бит точки совокупности с высокой надежностью, ив котором соответствующий бит перемеженной последовательности субблока W1 отображается в бит точки совокупности с высокой надежностью, если бит перемеженного субблока Y1 отображается в бит точки совокупности с низкой надежностью.

9. Способ по п.7, в котором перемеженные субблоки А и В информации обходят при побитовом мультиплексировании последовательности четности.

10. Устройство для турбокодера, причем устройство содержит:по меньшей мере один модуль перемежения субблоков для приема субблока А информации, субблока В информации, последовательности четности субблока Y1, последовательности четности субблока Y2, последовательности четности субблока W2 и последовательности четности субблока W1 и для вывода:перемеженного субблока А информации,перемеженного субблока В информации,побитово мультиплексированной последовательности перемеженных последовательностей субблоков Y1 и Y2, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков Y1 и Y2 состоит из первого выводимого бита из модуля перемежения субблоков Y1, первого выводимого бита из модуля перемежения субблоков Y2, второго выводимого бита из модуля перемежения субблоков Y1 и второго выводимого бита из модуля перемежения субблоков Y2 по порядку, ипобитово мультиплексированной последовательности перемеженных последовательностей субблоков W2 и W1, причем побитово мультиплексированная последовательность перемеженных последовательностей субблоков W2 и W1 состоит из первого выводимого бита из модуля перемежения субблоков W2, первого выводимого бита из модуля перемежения субблоков W1, второго выводимого бита из модуля перемежения субблоков W2 и второго выводимого бита из модуля перемежения субблоков W1 по порядку.

11. Устройство по п.10,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точки совокупности с низкой надежностью, если бит перемеженной последовательности субблока Y2 отображается в бит точки совокупности с высокой надежностью,в котором соответствующий бит перемеженной последовательности субблока W2 отображается в бит точ