Устройство запоминания частот свч сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может быть использовано в приемных устройствах, входящих в состав аппаратуры радионаблюдения и радиопротиводействия. Технический результат заключается в увеличении диапазона рабочих частот и динамического диапазона за счет подавления в первой ступени преобразования частот комбинационных частот, возникших во второй ступени. Устройство запоминания частот СВЧ сигналов состоит из первой и второй ступеней преобразования частот. В первую ступень преобразования частот входят: восемь смесителей, четыре делителя мощности, два сумматора, которые имеют по три входа, четыре выключателя, четыре гетеродина, шесть электрических фильтров. Во вторую ступень преобразования частот сигналов входят: входной делитель мощности, выходной сумматор, две фазовые секции на π/2, два входных смесителя и два выходных смесителя, гетеродин, два устройства цифровой памяти. 12 ил.

Реферат

Изобретение относится к области радиотехники и может быть использовано в приемных устройствах, входящих в состав аппаратуры радионаблюдения и радиопротиводействия.

Известно устройство запоминания частот СВЧ сигналов, использующее линию задержки, в качестве которой применена бухта коаксиального кабеля или волновода [1]. Недостатком такого устройства является малое время задержки, а также большие размеры устройства и большие потери в линии задержки. Для получения больших задержек использовались также акустические линии задержки. Поскольку скорость распространения акустических волн в различных материальных средах намного меньше скорости света, физические размеры таких линий задержки примерно в 105 раз меньше размеров кабеля, эквивалентного по задержке [1]. Недостатком этих устройств являются ограничения по потерям и по времени задержки.

Также известно сверхбыстродействующее запоминающее устройство с цифровым запоминанием частот СВЧ сигналов [2], принятое за прототип изобретения (фиг.1). Прототип содержит шесть смесителей: входной 1 и выходной 2 первой ступени преобразования частот, два входных 8, 9 и два выходных смесителя 10, 11 второй ступени преобразования частот, гетеродин 3 первой ступени преобразования частот, входной делитель мощности 4 с двумя выходами, выходной сумматор 5 с двумя входами, две фазовые секции 6, 7 на π/2, гетеродин 12 второй ступени преобразования частот и первое 13 и второе 14 устройства цифровой памяти.

Вход входного смесителя 1 является входом устройства запоминания частот СВЧ сигналов, а выход выходного смесителя 2 - выходом устройства запоминания частот СВЧ сигналов. Выход смесителя 1 соединен с входом делителя мощности 4. Гетеродинные входы смесителей 1 и 2 соединены с выходом гетеродина 3.

Гетеродинные входы двух входных 8, 9 и двух выходных 10,11 смесителей второй ступени преобразования частот соединены с выходом второго гетеродина 12.

Первый выход делителя мощности 4 соединен с входом первого входного смесителя 8 второй ступени преобразования, выход которого соединен с входом первого устройства цифровой памяти 13. Выход устройства 13 соединен с сигнальным входом первого выходного смесителя 10 второй ступени преобразования частот, выход которого соединен с входом первой фазовой секции 7, выход которой соединен с первым входом сумматора 5.

Второй выход делителя мощности 4 соединен с входом второй фазовой секции 6, выход которой соединен с сигнальным входом второго входного смесителя 9, выход которого соединен со вторым устройством цифровой памяти 14. Выход устройства 14 соединен с сигнальным входом второго выходного смесителя 11 второй ступени преобразования частот, выход которого соединен со вторым входом сумматора 5.

Выход сумматора 5 соединен с сигнальным входом выходного смесителя 2 первой ступени преобразования частот.

Принцип работы второй ступени преобразования частот, схема которой показана на фиг.2, заключается в следующем. Частоты входных СВЧ сигналов понижаются в смесителях 1, 8, 9 и поступают в устройства цифровой памяти 13, 14, в которых преобразуются из аналоговой формы в цифровую, запоминаются и далее преобразуются в аналоговую форму, а их частоты восстанавливаются до значений частот входных СВЧ сигналов.

Одновременно могут записываться и считываться несколько СВЧ сигналов с любыми видами частотной и фазовой модуляции. При этом время хранения информации не ограничено. В качестве устройств цифровой памяти 13, 14 могут использоваться устройства, описанные, например, в полезной модели [3].

Рассмотрим работу устройства запоминания частот СВЧ сигналов на примере устройства, описанного в статье [2]. Из этой же статьи также заимствованы значения частот СВЧ сигналов до и после их преобразования и частоты гетеродинов, что не уменьшает общность последующего рассмотрения.

Частоты входных СВЧ сигналов с помощью входного смесителя 1 и первого гетеродина 3 последовательно преобразуются из рабочего диапазона 8,0…16,0 ГГц в диапазон 0,75…1,25 ГГц. Далее частоты с помощью смесителей 8, 9 и второго гетеродина 12 преобразуются из диапазона 0,75…1,25 ГГц в диапазон рабочих частот устройства цифровой памяти, после чего с помощью смесителей 10, 11 и второго гетеродина 12 преобразуются обратно в диапазон частот 0,75…1,25 ГГц, и далее с помощью выходного смесителя 2 и первого гетеродина 3 преобразуются в рабочий диапазон частот устройства запоминания частот СВЧ сигналов 8,0…16,0 ГГц. Как следует из статьи [2], особенностью этого устройства является возможность запоминания частот СВЧ сигналов, изменяющихся в диапазоне частот шириной 0,5 ГГц, с помощью цифровых запоминающих устройств, работающих в полосе частот не шире 0,25 ГГц.

Входной СВЧ сигнал, преобразованный первым смесителем 1, делится на две равные части делителем мощности 4 (фиг.1, 2). С первого выхода делителя 4 сигнал поступает в левую ветвь устройства на вход смесителя 8, с помощью которого преобразуется из диапазона частот 0,75…1,25 ГГц в диапазон рабочих частот устройства цифровой памяти Ωmin…0,25 ГГц. Значение нижней границы диапазона Ωmin близко к нулю. Частота гетеродина 12 выбрана равная 1 ГГц [2]. С выхода смесителя 8 СВЧ сигнал поступает на вход устройства цифровой памяти 13, содержащего аналого-цифровой преобразователь, запоминающее устройство и цифроаналоговый преобразователь. С выхода устройства цифровой памяти СВЧ сигнал поступает на вход смесителя 10, с помощью которого его частота преобразуется в диапазон 0,75…1,25 ГГц, и после изменения фазы на π/2 с помощью фазовой секции 7 поступает на первый вход сумматора 5.

Со второго выхода делителя мощности 4 СВЧ сигнал поступает в правую ветвь устройства, которая аналогична левой, за исключением того, что в ней фазовая секция на π/2 6 включена между вторым выходом делителя 4 и входом смесителя 9, а выход смесителя 11 соединен со вторым входом сумматора 5.

Последовательность преобразования СВЧ сигналов второй ступенью преобразования частот и формулы, определяющие сами сигналы, приведены в таблицах 1, 2, 3, 4 (фиг.7, 8, 9, 10). Таблицы 1 и 2 построены для случая, когда частота СВЧ сигнала ω<ωг, где ωг частота сигнала гетеродина 12, а таблицы 3 и 4 для случая ω>ωг.. Таблицы 1 и 3 построены для левой ветви схемы, а таблицы 2 и 4 для правой ветви. В столбце «Сигнал» приведены формулы для СВЧ сигналов, поступающих из элементов, записанных в первом столбце таблицы, на вход элементов, записанных во втором столбце. Например, из таблицы 1 следует, что в случае ω<ωг СВЧ сигнал, поступающий из смесителя 8 левой ветви на устройство цифровой памяти 13, имеет вид u=a1UsinΩt, где Ω=ωг-ω, U и ω - амплитуда и частота входного СВЧ сигнала, an - коэффициент, учитывающий потери при преобразовании СВЧ сигналов.

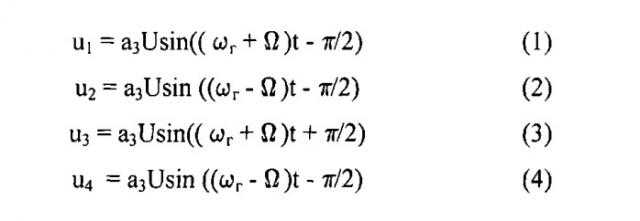

С помощью вышеупомянутых таблиц 1, 2, 3 и 4 определяют СВЧ сигналы, которые образуются в результате многократного преобразования во второй ступени преобразования частот (фиг.2) и поступают с выхода второй ступени на вход выходного смесителя первой ступени 2 (фиг.1). В случае ω<ωг (таблицы 1, 2, фиг.7, 8) на первый и второй входы сумматора 5 поступают СВЧ сигналы:

Из этих соотношений видно, что СВЧ сигналы u1 и u3 поступают на входы сумматора 5 в противофазе и компенсируют друг друга, а СВЧ сигналы u2 и u4 будут иметь равные фазы, сложатся в сумматоре 5 и поступят с его выхода на сигнальный вход смесителя 2 первой ступени преобразования частот, в котором частота СВЧ сигнала будет восстановлена до ее первоначального значения в диапазоне частот 8,0…16,0 ГГц.

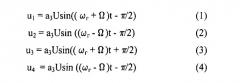

В случае ω>ωг (таблицы 3 и 4, фиг.9, 10) на первый и второй входы сумматора 5 поступают СВЧ сигналы:

Из этих соотношений также видно, что в противофазе на входы сумматора 5 поступают СВЧ сигналы u6 и u8 и компенсируют друг друга, а СВЧ сигналы u5 и u7 имеют одинаковые фазы, сложатся и поступят с выхода сумматора 5 на вход выходного смесителя 2, в котором частота СВЧ сигнала будет восстановлена до ее первоначального значения 8,0…16,0 ГГц.

Недостатком описанного устройства запоминания частот СВЧ сигналов является возможность образования в рабочем диапазоне выходных частот устройства вместе с полезным СВЧ сигналом большого числа комбинационных составляющих, образующихся на выходах смесителей второй ступени преобразования 8, 9, 10, 11 (фиг.2) [4]. Причем количество этих составляющих существенно зависит от того, насколько частоты полезных СВЧ сигналов, поступающих на вторую ступень преобразования, отличаются от частоты гетеродина 12. Это свойство является следствием того, что значение частоты гетеродина 1 ГГц равно среднему значению диапазона входных частот второй ступени преобразования 0,75…1,25 ГГц, т.е. на оси частот расположено посередине диапазона входных частот. Если при перестройке частоты входного СВЧ сигнала ее значение слева или справа по оси частот стремится к значению частоты гетеродина (к 1 ГГц), то значение промежуточной частоты, равное разнице значений входного СВЧ сигнала и гетеродина, стремится к нулю. При этом относительная ширина полосы промежуточных частот резко увеличивается, стремясь к бесконечному числу октав. В результате этого в полосу выходных (промежуточных) частот попадает большое число комбинационных частот. Это видно на фиг.3, 4, на которых изображены спектры выходных частот смесителей 10 и 11 для случая ω>ωг. На выходе смесителей помимо гетеродинного и полезных выходных СВЧ сигналов с частотами ωг и ω=ωг+Ω будут также образовываться комбинационные составляющие с частотами ω=ωг+mΩ. Разность комбинационных частот равна либо Ω, либо кратна ей. Здесь Ω рабочая частота СВЧ сигнала, поступающего на входы устройств цифровой памяти 13 и 14, a m - целые числа натурального ряда чисел: 0, 1, 2, 3… Полезный сигнал на фиг.3, 4 помечен цифрой 1.

Изменением частоты гетеродина 12 эту проблему решить невозможно, т.к. устройство, спроектированное по схеме, приведенной в [2] и изображенной на фиг.1, работать не будет из-за нарушений фазовых соотношений СВЧ сигналов на выходах левой и правой ветвей второй ступени преобразования частот (фиг.2).

Часть комбинационных составляющих и гетеродинные сигналы можно подавить путем использования балансных или двойных балансных смесителей [5]. При этом число комбинационных составляющих в выходном спектре частот уменьшится, но проблема решена не будет. Комбинационные составляющие с частотами ω=ωг-mΩ в рассмотренном случае будут отсутствовать в выходных спектрах, поскольку, как это было показано выше, они будут подавлены устройством второй ступени преобразования (фиг.2). Таким образом, из-за увеличения относительной ширины диапазона выходных (промежуточных) частот в полосе выходных частот всегда будет присутствовать большое количество неподавленных комбинационных составляющих [5]. Кроме того, на частоте 1 ГГц и в небольшой области вокруг этой точки на оси частот устройство, выполненное по схеме на фиг.2, работать не будет из-за равенства или близости частот входных сигналов к частоте гетеродина. Эта область определяется параметрами устройства цифровой памяти, а именно значением нижней границы диапазона рабочих частот этого устройства Ωmin.

Из приведенных на фиг.3, 4 частотных планах видно, что в полосу выходных частот не будут попадать комбинационные частоты только в случае выполнения условия Ω>ΔΩ/2, где Ω - частота входного СВЧ сигнала устройства цифровой памяти, а ΔΩ - ширина полосы рабочих частот устройств цифровой памяти 13 и 14, равной в рассматриваемом случае 0,25 ГГц. Размножение выходных СВЧ сигналов в устройствах радионаблюдения будет приводить к неоднозначности получаемых результатов. В случае радиопротиводействия, к снижению эффективности работы аппаратуры, поскольку при ограниченной мощности выходного усилителя станции выходная мощность будет распределяться между большим числом составляющих выходного спектра, поэтому уровень мощности полезного выходного сигнала при этом будет намного меньше требуемого значения.

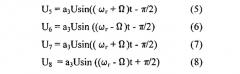

Области, пораженные комбинационными частотами на фиг.3, 4, затенены. На фиг.5 приведены частотные планы входных сигналов для диапазона 8,0…12,0 ГГц (А), второй ступени преобразования (Б) и выходных сигналов (В), на которых пораженные области также затенены. Из приведенных частотных планов видно, что в диапазоне частот выходных сигналов области однозначности и неоднозначности чередуются с периодом, равным ширине рабочего диапазона частот устройств цифровой памяти 13 и 14, равной 0,25 ГГц. При этом однозначность воспроизведения будет только в половине диапазона входных частот всего устройства, что и является главным недостатком прототипа.

Общие признаки прототипа и изобретения первой (ПСПЧ) ступени преобразования частот: первый 1, второй 2 смесители, первый гетеродин 3, выход которого соединен с гетеродинными входами первого 1 и второго 2 смесителей. Кроме того, вход первого смесителя 1 является входом устройства запоминания частот СВЧ сигналов, выход второго смесителя 2 является выходом устройства запоминания частот СВЧ сигналов.

Общие признаки прототипа и изобретения второй (ВСПЧ) ступени преобразования частот: входной делитель 4 мощности, который имеет два выхода - первый и второй, выходной сумматор 5 с двумя входами - первым и вторым, две фазовые секции на π/2 6, 7 - вторая и первая, два входных смесителя 8, 9 - первый и второй и два выходных смесителя 10, 11 - первый и второй, гетеродин 12, два устройства цифровой памяти 13, 14 - первое и второе, причем вход входного делителя 4 является входом устройства ВСПЧ 15, а выход выходного сумматора 5 является выходом устройства ВСПЧ 15, причем гетеродинные входы двух входных 8, 9 и двух выходных 10, 11 смесителей соединены с выходом гетеродина 12 ВСПЧ, первый выход входного делителя мощности 4 ВСПЧ соединен с сигнальным входом первого входного смесителя 8, выход которого соединен с входом первого устройства цифровой памяти 13, выход которого соединен с сигнальным входом первого выходного смесителя 10, выход которого соединен с входом первой фазовой секции 7, выход которой соединен с первым входом сумматора 5 ВСПЧ, кроме того, второй выход входного делителя мощности 4 ВСПЧ соединен с входом второй фазовой секции 6, выход которой соединен с сигнальным входом второго входного смесителя 9, выход которого соединен с входом второго устройства цифровой памяти 14, выход которого соединен с сигнальным входом второго выходного смесителя 11, выход которого соединен со вторым входом сумматора (5).

Технической задачей изобретения является расширение диапазона рабочих частот и увеличение динамического диапазона входных СВЧ сигналов, что позволяет существенно улучшить технические параметры аппаратуры радионаблюдения и радиопротиводействия, сделав ее работоспособной в широком динамическом диапазоне и в широком диапазоне частот входных сигналов.

Техническим результатом изобретения является увеличение в два раза диапазона рабочих частот устройства запоминания частот СВЧ сигналов и увеличение динамического диапазона устройства более чем на 30...50 дБ. Прототип эффективно работает только на частотах, составляющих половину рабочего диапазона частот устройства.

Технический результат изобретения достигается благодаря тому, что в первую ступень преобразования частот (ПСПЧ) дополнительно введены: четыре делителя мощности 16, 17, 18 и 19, два сумматора 20 и 21, четыре выключателя 22, 23, 24 и 25, три гетеродина 26, 27 и 28, шесть электрических фильтров 29, 30, 31, 32, 33 и 34, шесть смесителей 35, 36, 37, 38, 39 и 40.

Введение в ПСПЧ новых элементов и новых связей позволяет исключить из диапазона рабочих частот устройства запоминания частот СВЧ сигналов комбинационные составляющие, образующиеся во второй ступени преобразования частот, что в свою очередь позволяет ликвидировать в диапазоне рабочих частот устройства области неоднозначности определения частот, что и решает поставленную задачу.

Изобретение поясняется чертежами:

На фиг.1 приведена электрическая схема устройства запоминания частот СВЧ сигналов (прототип).

На фиг.2 приведена электрическая схема второй ступени преобразования частот устройств запоминания частот СВЧ сигналов прототипа и изобретения.

На фиг.3 показан спектр выходных частот второй ступени преобразования частот, при условии Ω>ΔΩ/2.

На фиг.4 показан спектр выходных частот второй ступени преобразования частот, при условии Ω>ΔΩ/2.

На фиг.5 показаны:

A) - участок диапазона частот входных сигналов 8,0…12,0 ГГц;

Б) - частотный план на выходе второй ступени преобразования частот;

B) - области, пораженные комбинационными составляющими в диапазоне 8,0…12,0 ГГц.

На фиг.6 приведена электрическая схема устройств запоминания частот СВЧ сигналов по изобретению.

На фиг.7 в таблице 1 приведены формулы для сигналов, поступающих из элементов, записанных в первом столбце таблицы, на вход элементов, записанных во втором столбце для случая ω<ωг, левая ветвь.

На фиг.8 в таблице 2 приведены формулы для сигналов, поступающих из элементов, записанных в первом столбце таблицы, на вход элементов, записанных во втором столбце для случая ω<ωг, правая ветвь.

На фиг.9 в таблице 3 приведены формулы для сигналов, поступающих из элементов, записанных в первом столбце таблицы, на вход элементов, записанных во втором столбце для случая ω<ωг, левая ветвь.

На фиг.10 в таблице 4 приведены формулы для сигналов, поступающих из элементов, записанных в первом столбце таблицы, на вход элементов, записанных во втором столбце для случая ω<ωг, правая ветвь.

На фиг.11 в таблице 5 приведены значения входных и выходных частот смесителей второй ступени преобразования 35 и 36, частоты гетеродинов 26 и 28 и частоты гетеродинного сигнала смесителя 36.

На фиг.12 в таблице 6 приведены значения входных и выходных частот смесителей второй ступени преобразования 37 и 38, частоты гетеродинов 27, 28 и частоты гетеродинного сигнала смесителя 37.

На чертежах введены обозначения: 1 и 2 - первый и второй смесители первой ступени преобразования частот (ПСПЧ); 3 - гетеродин ПСПЧ; 4 - входной делители мощности второй ступени преобразования частот (ВСПЧ); 5 - выходной сумматор ВСПЧ; 6 и 7 - фазовые секции на π/2 ВСПЧ; 8 и 9 - входные смесители ВСПЧ; 10 и 11 - выходные смесители ВСПЧ; 12 - гетеродин ВСПЧ; 13 и 14 - первое и второе устройства цифровой памяти ВСПЧ; 15 - устройство ВСПЧ; 16, 17, 18, 19 - делители мощности ПСПЧ; 20 и 21 - сумматоры ПСПЧ; 22, 23, 24, 25 - выключатели ПСПЧ; 26, 27, 28 - гетеродины ПСПЧ; 29, 30, 31, 32, 33, 34 - электрические фильтры ПСПЧ; 35, 36, 37, 38, 39, 40 - смесители ПСПЧ.

Технический результат изобретения достигается благодаря тому, что устройство по изобретению (фиг.2, 6) содержит первую и вторую ступень преобразования частот 15.

В первую ступень преобразования частот (ПСПЧ) (фиг.6) входят: восемь смесителей 1, 2, 35, 36, 37, 38, 39, 40 - первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой, четыре делителя мощности 16, 17, 18, 19 - первый, второй, третий и четвертый, которые имеют по два выхода, два сумматора 20, 21 - первый и второй, которые имеют по три входа - первый, второй и третий, четыре выключателя 22, 23, 24, 25 - первый, второй, третий и четвертый, четыре гетеродина 3, 26, 27, 28 - первый, второй, третий и четвертый, шесть электрических фильтров 29, 30, 31, 32, 33, 34 - первый, второй, третий, четвертый, пятый и шестой.

Во вторую ступень преобразования частот (ВСПЧ) (фиг.2) 15 входят: входной делитель 4 мощности, который имеет два выхода - первый и второй, выходной сумматор 5 с двумя входами - первым и вторым, две фазовые секции на π/2 6, 7 - вторая и первая, два входных смесителя 8, 9 - первый и второй, два выходных смесителя 10, 11 - первый и второй, гетеродинный генератор 12, два устройства цифровой памяти 13, 14 - первое и второе.

Электрические соединения блоков по изобретению (фиг.6)

Выход первого гетеродина 3 соединен с гетеродинными входами первого 1 и второго 2 смесителей, причем сигнальный вход первого смесителя 1 является входом устройства запоминания частот СВЧ сигналов, а выход второго смесителя 2 является выходом устройства запоминания частот СВЧ сигналов.

Выход первого смесителя 1 соединен с входом первого делителя мощности 16, выходы которого соединены соответственно с входами первого 22 и второго 23 выключателей.

Выход первого выключателя 22 соединен с входом второго делителя мощности 17, выходы которого соединены соответственно с входами первого и второго электрических фильтров 29, 30, выходы которых соединены соответственно с первым и вторым входами первого сумматора 20, выход которого соединен с входом устройства ВСПЧ 15. Выход ВСПЧ 15 соединен с входом третьего делителя мощности 18, выходы которого соединены соответственно с входами третьего и четвертого выключателей 24, 25.

Выход третьего выключателя 24 соединен с входом четвертого делителя мощности 19, выходы которого соединены соответственно с входами третьего 31 и четвертого 32 электрических фильтров, выходы которых соединены соответственно с первым и вторым входами второго сумматора 21, выход которого соединен с сигнальным входом второго смесителя 2.

Выход второго выключателя 23 соединен с сигнальным входом третьего смесителя 35, выход которого соединен с входом пятого электрического фильтра 33, выход которого соединен с сигнальным входом четвертого смесителя 36, выход которого соединен с третьим входом первого сумматора 20.

Выход четвертого выключателя 25 соединен с сигнальным входом пятого смесителя 37, выход которого соединен с входом шестого электрического фильтра 34, выход которого соединен с сигнальным входом шестого смесителя 38, выход которого соединен с третьим входом второго сумматора 21.

Выход четвертого гетеродина 28 соединен с входами седьмого и восьмого смесителей 39, 40.

Выходы второго гетеродина 26 соединены соответственно с гетеродинными входами третьего и седьмого смесителей 35, 39.

Выход третьего гетеродина 27 соединен с гетеродинными входами шестого 38 и восьмого 40 смесителей.

Выход седьмого смесителя 39 соединен с гетеродинным входом четвертого смесителя 36, причем выход восьмого смесителя 40 соединен с гетеродинным входом пятого смесителя 37.

Электрические соединения блоков в ВСПЧ 15 (фиг.2)

Вход входного делителя 4 ВСПЧ является входом устройства ВСПЧ 15, а выход выходного сумматора 5 ВСПЧ является выходом устройства ВСПЧ 15.

Гетеродинные входы двух входных 8, 9 и двух выходных 10, 11 смесителей ВСПЧ соединены с выходом гетеродина 12 ВСПЧ, первый выход входного делителя мощности 4 ВСПЧ соединен с сигнальным входом первого входного смесителя 8, выход которого соединен с входом первого устройства цифровой памяти 13, выход которого соединен с сигнальным входом первого выходного смесителя 10, выход которого соединен с входом первой фазовой секции 7, выход которой соединен с первым входом сумматора 5 ВСПЧ.

Второй выход входного делителя мощности 4 ВСПЧ соединен с входом второй фазовой секции 6, выход которой соединен с сигнальным входом второго входного смесителя 9 ВСПЧ, выход которого соединен с входом второго устройства цифровой памяти 14, выход которого соединен с сигнальным входом второго выходного смесителя 11 ВСПЧ, выход которого соединен со вторым входом сумматора 5 ВСПЧ, выход которого является выходом ВСПЧ.

Элементы СВЧ устройства по изобретению являются стандартными и могут быть выполнены, например, в микрополосковом исполнении на основе тонких или толстых пленок. Для проектирования вышеперечисленных элементов может быть использован пакет прикладных программ «Microwave Office», который содержит мощный и гибкий комплекс программ САПР. В его рабочей библиотеке имеются программы проектирования упомянутых элементов.

В качестве устройств цифровой памяти может быть использовано устройство, описанное, например, в [3].

Устройство запоминания частот СВЧ сигналов (фиг.1) работает следующим образом. Для большей наглядности рассмотрения принципа работы устройства проведем его с использованием значений частот, приведенных в статье [2], что не нарушит общности проводимого рассмотрения. Для нормального функционирования устройства необходимо исключить область частот, примыкающую к частоте гетеродина, равной в рассматриваемом случае 1 ГГц. Для этого необходимо выполнить условие Ω>ΔΩ/2, где Ω - частота входного сигнала устройства цифрового запоминания частот, a ΔΩ - ширина полосы рабочих частот устройства цифрового запоминания частот, входящего в состав второй ступени преобразования частот 15. В рассматриваемом случае Ω может изменяться в диапазоне частот Ωmin…0,25 ГГц, где Ωmin - значение нижней границы диапазона, обычно близкое к нулю. Выполнение упомянутого выше условия уменьшит примерно в два раза полосу рабочих частот устройств цифровой памяти (13 и 14 на фиг.1), сужая ее до значений 0,125…0,25 ГГц, что в свою очередь лишает устройство одного из основных его достоинств.

Для достижения поставленной цели диапазон частот входных СВЧ сигналов устройства второй ступени преобразования частот 0,75…1,25 ГГц разбивается на четыре поддиапазона:

| 1 поддиапазон | 0,75…0,875 ГГц; |

| 2 поддиапазон | 0,875…1,0 ГГц; |

| 3 поддиапазон | 1,0…1,125 ГГц; |

| 4 поддиапазон | 1,125…1,25 ГГц. |

Для запоминания частот второго и третьего поддиапазонов частоты этих СВЧ сигналов преобразуются, соответственно, в первый и четвертый поддиапазоны, запоминаются, после чего восстанавливаются первоначальные значения. Для упрощения процесса фильтрации целесообразно преобразовывать частоты из второго поддиапазона в четвертый и из третьего в первый.

Частоты входных СВЧ сигналов первой ступенью преобразования с помощью смесителя 1 и гетеродина 3 преобразуются в диапазон частот 0,75…1,25 ГГц и поступают на вход делителя 16, выходные плечи которого нагружены выключателями 22 и 23. С выхода выключателя 22 СВЧ сигналы поступают на вход делителя мощности 17, выходы которого нагружены электрическими фильтрами 29 и 30, настроенные на частоты 1-го и 4-го поддиапазонов, и после суммирования в сумматоре 20 поступают на вход устройства второй ступени преобразования частот 15, где и происходит цифровое запоминание частот этих СВЧ сигналов.

Для запоминания частот СВЧ сигналов второго и третьего поддиапазонов частоты этих СВЧ сигналов преобразуются в первый и четвертый поддиапазоны. Прямое гетеродинное преобразование с помощью одного смесителя и одного гетеродинного генератора не решает поставленную задачу, поскольку при прямом и обратном преобразовании частот, как и в устройстве, выполненном по схеме на фиг.1, на выходе смесителя в рабочей полосе частот образуется большое количество комбинационных составляющих низкого порядка. Эту задачу позволяет решить компенсационный метод, существенно облегчающий фильтрацию выходных СВЧ сигналов смесителя, который подробно описан в книгах [7] и [8] и патенте [9]. Суть метода состоит в использовании двукратного преобразования частот. При первом преобразовании, осуществляющем «преобразование вверх» по оси частот, частоты сигналов увеличиваются, а относительная полоса уменьшается, что уменьшает вероятность попадания комбинационных частот в выходную полосу преобразователя. При этом комбинационные составляющие, частоты которых все же попадают в полосу рабочих частот, будут иметь высокие порядки и, соответственно, малые уровни мощности. Второе преобразование осуществляет преобразование частот СВЧ сигналов «вниз» по оси частот в заданный частотный диапазон.

В рассматриваемом случае преобразование частот СВЧ сигналов осуществляется следующим образом. Входные СВЧ сигналы с выхода выключателя 23 поступают на вход смесителя 35, в котором преобразуются вверх по оси частот, фильтруются электрическим фильтром 33, после чего смесителем 36 преобразуются в заданный диапазон частот и через сумматор 20 поступают на вход устройства второй ступени преобразования частот 15. Заметим, что если частоты гетеродинных сигналов преобразователей 35 и 36 будут одинаковыми, то частоты сигналов на входе преобразователя 35 и на выходе преобразователя 36 будут также одинаковыми. Для преобразования частот сигналов из второго и третьего диапазонов в первый и четвертый диапазоны гетеродинные частоты преобразователей 35 и 36 должны отличаться друг от друга на заданную величину. Это достигается тем, что сигнал гетеродина 26 поступает в смеситель 35 непосредственно, а в смеситель 36 с заданным сдвигом частоты, осуществляемым с помощью гетеродина 28 и смесителя 39.

Величины гетеродинных частот смесителей 35 и 36 выбираются существенно больше частот входных СВЧ сигналов (в пять-десять раз и более), что позволяет эффективно отфильтровывать фильтром 33 полезные сигналы от мощных комбинационных составляющих и гармоник низких порядков.

После прохождения СВЧ сигналов через устройство второй ступени преобразования частот 15 значения частот СВЧ сигналов второго и третьего поддиапазонов восстанавливаются до их первоначальных значений также с помощью компенсационных схем, содержащих смесители 37, 38 и 40, фильтр 34 и гетеродин 27. Для изменения гетеродинных частот смесителей 36 и 37 используется один и тот же генератор 28, поскольку и в первом, и во втором случае изменение значения частот одинаково. Работа компенсационных схем была подробно изложена выше. Очевидно, преобразование частот сигналов первого и четвертого поддиапазонов не требуется. Устройства, работающие в этих поддиапазонах, подключаются к устройству второй ступени преобразования частот 15 одновременно.

В диапазон входных и выходных частот 0,75…1,25 ГГц была спроектирована по схеме фиг.6 и с помощью таблиц 1, 2, 3 и 4 первая ступень преобразования частот устройства запоминания частот СВЧ сигналов. В качестве цифровой памяти рассмотрено устройство, работающее в диапазоне частот 0…0,25 ГГц. Возможный вариант формирования частот гетеродинных сигналов смесителей 35 и 36 приведен в таблице 5, а смесителей 37 и 38 в таблице 6. Переключение поддиапазонов осуществлялось изменением значений гетеродинных частот генераторов 26 и 27, входящих в правую ветвь схемы (в компенсационные устройства преобразования частот). Значения гетеродинных частот смесителей 35, 36, 37, 38 приведены в таблицах 5 и 6 в столбцах 2 и 5. Гетеродин 28 обеспечивает необходимую разность гетеродинных частот смесителей 35, 36 и 37, 38. Значение частоты этого гетеродина приведено в столбцах 4 таблиц 5 и 6.

В результате апробации описанных выше устройств был достигнут технический результат изобретения: обеспечена работоспособность устройства запоминания частот СВЧ сигналов во всем рабочем диапазоне частот. Динамический диапазон устройства по изобретению, по сравнению с прототипом, увеличен более чем на 50 дБ во всем диапазоне рабочих частот.

Отличительные признаки изобретения. Четыре делителя мощности 16, 17, 18, 19 - первый, второй, третий и четвертый, которые имеют по два выхода, два сумматора 20, 21 - первый и второй, которые имеют по три входа - первый, второй и третий, четыре выключателя 22, 23, 24, 25 - первый, второй, третий и четвертый, три гетеродина 26, 27, 28 - второй, третий и четвертый, шесть электрических фильтров 29, 30, 31, 32, 33, 34 - первый, второй, третий, четвертый, пятый и шестой, шесть смесителей 35, 36, 37, 38, 39, 40 - третий, четвертый, пятый, шестой, седьмой и восьмой.

Выход первого смесителя 1 соединен с входом первого делителя мощности 16, выходы которого соединены соответственно с входами первого 22 и второго 23 выключателей, выход первого выключателя 22 соединен с входом второго делителя мощности 17, выходы которого соединены соответственно с входами первого и второго электрических фильтров 29, 30, выходы которых соединены соответственно с первым и вторым входами первого сумматора 20, выход которого соединен с входом устройства ВСПЧ 15, выход которого соединен с входом третьего делителя мощности 18, выходы которого соединены соответственно с входами третьего и четвертого выключателей 24, 25.

Выход третьего выключателя 24 соединен с входом четвертого делителя мощности 19, выходы которого соединены соответственно с входами третьего 31 и четвертого 32 электрических фильтров, выходы которых соединены соответственно с первым и вторым входами второго сумматора 21, выход которого соединен с сигнальным входом второго смесителя 2.

Выход второго выключателя 23 соединен с сигнальным входом третьего смесителя 35, выход которого соединен с входом пятого электрического фильтра 33, выход которого соединен с сигнальным входом четвертого смесителя 36, выход которого соединен с третьим входом первого сумматора 20.

Выход четвертого выключателя 25 соединен с сигнальным входом пятого смесителя 37, выход которого соединен с шестым электрическим фильтром 34, выход которого соединен с сигнальным входом шестого смесителя 38, выход которого соединен с третьим входом второго сумматора 21.

Выход четвертого гетеродина 28 соединен с входами седьмого и восьмого смесителей 39, 40, причем выходы второго гетеродина 26 соединены соответственно с гетеродинными входами третьего и седьмого смесителей 35, 39.

Выход третьего гетеродина 27 соединен с гетеродинными входами шестого 38 и восьмого 40 смесителей, выход седьмого смесителя 39 соединен с гетеродинным входом четвертого смесителя 36, причем выход восьмого смесителя 40 соединен с гетеродинным входом пятого смесителя 37.

Литература

1. Ю.М.Перунов, К.И.Фомичев, Л.М.Юдин. "Радиоэлектронное подавление информационных каналов систем управления оружием". - Москва, "Радиотехника", 2008 г., стр.156 - 168.

2. А.Афинов. "Направления совершенствования средств РЭП индивидуальной защиты самолетов". "Зарубежное военное обозрение", 1998 г., №9, стр.35-43.

3. Патент РФ (полезная модель) №66587 от 05.03.2007 г.

4. "Кристаллические детекторы", под редакцией Е.Я.Пумпера, изд. "Сов. радио", Москва, 1950 г., том 1, стр.178-187.

5. М.Е.Мовшович, "Полупроводниковые преобразователи частоты", "Энергия", Ленинградское отделение, 1974, стр.244, 245.

6. В.Н.Олейников, В.В.Бойков, В.А.Лукьянчук. «Двойной балансный смеситель СВЧ». Техника средств связи. Радиоизмерительная техника. Выпуск 7(32), 1980 г., Москва, стр.56 -64.

7. Д.Н.Шапиро, А.А.Паин, "Основы теории синтеза частот". Москва, "Радио и связь", 1981 г., стр.111-118.

8. В.А.Левин, Г.А.Норкин, "Радиотехнические системы фильтрации с возвратным гетеродинированием". Москва, "Советское радио", 1979 г., стр.30.

9. Патент РФ №2133078 от 26.07.96 г.

Устройство запоминания частот СВЧ сигналов, содержащее первую (ПСПЧ) и вторую (ВСПЧ) ступени преобразования частот, причем в ПСПЧ входят первый, второй смесители, первый гетеродин, выход которого соединен с гетеродинными входами первого и второго смесителей, кроме того, вход первого смесителя является входом устройства запоминания частот СВЧ сигналов, выход второго смесителя является выходом устройства запоминания частот СВЧ сигналов, причем в ВСПЧ входят: входной делитель мощности, который имеет два выхода - первый и второй, выходной сумматор с двумя входами - первым и вторым, две фазовые секции на π/2 - вторая и первая, два входных смесителя - первый и второй и два выходных смесителя - первый и второй, гетеродин, два устройства цифровой памяти - первое и второе, причем вход входного делителя является входом устройства ВСПЧ, а выход выходного сумматора является выходом устройства ВСПЧ, причем гетеродинные входы двух входных и двух выходных смесителей соединены с выходом гетеродина ВСПЧ, первый выход входного делителя мощности ВСПЧ соединен с сигнальным входом первого входного смесителя, выход которого соединен с входом первого устройства цифровой памяти, выход которого соединен с сигнальным входом первого выходного смесителя, выход которого соединен с входом первой фазовой секции, выход которой соединен с первым входом сумматора ВСПЧ, кроме того, второй выход входного делителя мощности ВСПЧ соединен с входом второй фазовой секции, выход которой соединен с сигнальным входом второго входного смесителя, выход которого соединен с входом второго устройства цифровой памяти, выход которого соединен с сигнальным входом второго выходного смесителя, выход которого соединен со вторым входом сумматора, отличающееся тем, что в устройство ПСПЧ введены: четыре делителя мощности - первый, второй, третий и четвертый, которые имеют по два выхода