Импульсный селектор

Иллюстрации

Показать всеИзобретение относится к импульсной технике и может быть использовано для логической обработки синхронизированных по переднему фронту положительных импульсных сигналов x1,…,xn∈{0,1}, имеющих длительности τ1,…,τn. Техническим результатом является обеспечение воспроизведения любой из операций min(τ1,…,τn), supramin(τ1,…,τn), submax(τ1,…,τn), max(τ1,…,τn). Устройство содержит n-1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (11,…,1n-1), n-1 замыкающих ключей (21,…,2n-1), резистор (3), n-2 размыкающих ключей (41,…,4n-1) и n-2 дополнительных замыкающих ключей (51,…,5n-2). 2 ил., 1 табл.

Реферат

Изобретение относится к импульсной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны импульсные селекторы (см., например, патент РФ 2273090, кл. H03K 5/26, 2006 г.), которые воспроизводят любую из операций min(τ1,…,τn), max(τ1,…,τn), где τ1,…,τn есть длительности положительных импульсных сигналов x1,…,xn∈{0,1}, синхронизированных по переднему фронту.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных импульсных селекторов, относятся ограниченные функциональные возможности, обусловленные тем, что не воспроизводятся операции supramin(τ1,…,τn), submax(τ1,…,τn).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип импульсный селектор (патент РФ 2417516, кл. H03K 5/26, 2011 г.), который содержит n-1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n-1 замыкающих ключей, резистор и воспроизводит любую из операций min(τ1,…,τn), max(τ1,…,τn), где τ1,…,τn есть длительности положительных импульсных сигналов x1,…,xn∈{0,1}, синхронизированных по переднему фронту.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не воспроизводятся операции supramin(τ1,…,τn), submax(τ1,…,τn).

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения воспроизведения любой из операций min(τ1,…,τn), supramin(τ1,…,τn), submax(τ1,…,τn), max(τ1,…,τn), где τ1,…,τn есть длительности положительных импульсных сигналов x1,…,xn∈{0,1}, синхронизированных по переднему фронту.

Указанный технический результат при осуществлении изобретения достигается тем, что в импульсном селекторе, содержащем n-1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n-1 замыкающих ключей и резистор, выходу j-го ( j = 1, n − 2 ¯ ) замыкающего ключа и первый вход i-го ( i = 1, n − 1 ¯ ) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с входом (j+1)-го замыкающего ключа и i-ым информационным входом импульсного селектора, а резистор подсоединен между объединенными вторыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и объединенными выходом (n-1)-го замыкающего ключа, выходом импульсного селектора, особенность заключается в том, что в него введены n-1 размыкающих и n-2 дополнительных замыкающих ключей, управляющий вход j-ых замыкающего, размыкающего, дополнительного замыкающего ключей и управляющий вход (n-1)-ых замыкающего, размыкающего ключей соединены соответственно с выходом j-го и выходом (n-1)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вход (j+1)-го и выход i-го размыкающих ключей соединены соответственно с выходом j-го дополнительного замыкающего и выходом i-го замыкающего ключей, выход предыдущего дополнительного замыкающего ключа соединен с входом последующего дополнительного замыкающего ключа, а второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход первого замыкающего ключа и объединенные входы первых размыкающего, дополнительного замыкающего ключей соединены соответственно с первым, вторым и третьим настроечными входами импульсного селектора.

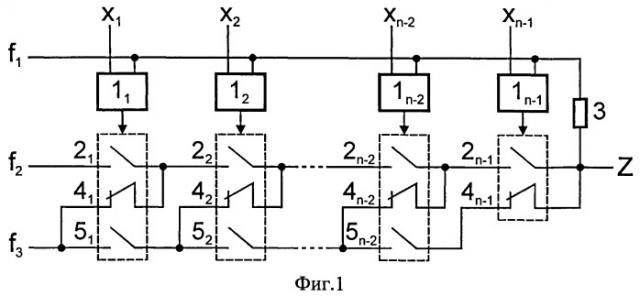

На фиг.1 представлена схема предлагаемого импульсного селектора. На фиг.2 приведены временные диаграммы, поясняющие принцип его работы (например, при n=4).

Импульсный селектор содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11,…,1n-1 замыкающие ключи 21,…,2n-1, резистор 3, размыкающие ключи 41,…,4n-1 и дополнительные замыкающие ключи 51,…,5n-2, причем выход ключа 2 j ( j = 1, n − 2 ¯ ) и первый вход элемента 1 i ( i = 1, n − 2 ¯ ) соединены соответственно с входом ключа 2j+1 и i-ым информационным входом импульсного селектора, резистор 3 подсоединен между объединенными вторыми входами элементов 11,…,1n-1 и объединенными выходом ключа 2n-1 и выходом импульсного селектора, управляющий вход ключей 2j, 4j, 5j и управляющий вход ключей 2n-1, 4n-1 соединены соответственно с выходами элементов 1j и вход ключа 4j+1 и выход ключа 4j соединены соответственно с выходами ключей 5j и 2i, выход предыдущего дополнительного замыкающего ключа соединен с входом последующего дополнительного замыкающего ключа, а второй вход элемента 11, вход ключа 21 и объединенные входы ключей 41, 51 соединены соответственно с первым, вторым и третьим настроечными входами импульсного селектора.

Работа предлагаемого импульсного селектора осуществляется следующим образом. На его первый,…, (n-1)-й информационные входы подаются соответственно синхронизированные по переднему фронту положительные импульсные сигналы x1,…,xn-1∈{0,1}, имеющие длительности τ1,…,τn-1 соответственно. На его первый и второй, третий настроечные входы подаются соответственно необходимые управляющие сигналы f1∈{0,1} и f2,f3∈{0,1,xn} (xn∈{0,1} - положительный импульсный сигнал, синхронизированный по переднему фронту с сигналами x1…xn-1 и имеющий длительность τn). Если на управляющем входе ключей 2j, 4j, 5j ( j = 1, n − 2 ¯ ) действует логическая «1» либо логический «0», то ключи 2/, 5/ соответственно замкнуты либо разомкнуты, а ключ 4j - соответственно разомкнут либо замкнут. Если на управляющем входе ключей 2n-1, 4n-1 присутствует логическая «1» либо логический «0», то ключ 2n-1(4n-1) соответственно замкнут (разомкнут) либо разомкнут (замкнут). Таким образом, имеем следующую таблицу

| f1 | f2 | f3 | Z |

| 0 | xn | 0 | { 1 п р и ∑ k = 1 n x k = n 0 п р и ∑ k = 1 n x k ≠ n |

| 0 | 1 | xn | { 1 п р и ∑ k = 1 n x k ≥ n − 1 0 п р и ∑ k = 1 n x k < n − 1 |

| 1 | 0 | xn | { 1 п р и ∑ k = 1 n x k ≥ 2 0 п р и ∑ k = 1 n x k < 2 |

| 1 | xn | 1 | { 1 п р и ∑ k = 1 n x k ≠ 0 0 п р и ∑ k = 1 n x k = 0 |

С учетом указанной таблицы и временных диаграмм (фиг.2) длительность импульсного сигнала Z, действующего на выходе предлагаемого селектора, определяется выражением

τ Z = { min ( τ 1 , … , τ n ) п р и f 1 = 0, f 2 = x n , f 3 = 0 sup r a min ( τ 1 , … , τ n ) п р и f 1 = 0, f 2 = 1, f 3 = x n s u b max ( τ 1 , … , τ n ) п р и f 1 = 1, f 2 = 0, f 3 = x n max ( τ 1 , … , τ n ) п р и f 1 = 1, f 2 = x n , f 3 = 1 .

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый импульсный селектор обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает воспроизведение любой из операций min(τ1,…,τn), supramin(τ1,…,τn), submax(τ1,…,τn), max(τ1,…,τn), где τ1,…,τn есть длительности положительных импульсных сигналов x1,…,xn∈{0,l}, синхронизированных по переднему фронту.

Импульсный селектор, содержащий n-1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, n-1 замыкающих ключей и резистор, причем выход j-го замыкающего ключа и первый вход i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с входом (j+1)-го замыкающего ключа и i-ым информационным входом импульсного селектора, а резистор подсоединен между объединенными вторыми входами всех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и объединенными выходом (n-1)-го замыкающего ключа, выходом импульсного селектора, отличающийся тем, что в него введены n-1 размыкающих и n-2 дополнительных замыкающих ключей, управляющий вход j-ых замыкающего, размыкающего, дополнительного замыкающего ключей и управляющий вход (n-1)-ых замыкающего, размыкающего ключей соединены соответственно с выходом j-го и выходом (n-1)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вход (j+1)-го и выход i-го размыкающих ключей соединены соответственно с выходом j-го дополнительного замыкающего и выходом i-го замыкающего ключей, выход предыдущего дополнительного замыкающего ключа соединен с входом последующего дополнительного замыкающего ключа, а второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход первого замыкающего ключа и объединенные входы первых размыкающего, дополнительного замыкающего ключей соединены соответственно с первым, вторым и третьим настроечными входами импульсного селектора.