Rs-триггер с многозначным внутренним представлением сигналов

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации. Техническим результатом является повышение быстродействия и создание элементной базы вычислительных устройств, работающих на принципах многозначной линейной алгебры. Устройство содержит R и S входы, выходные транзисторы, источник вспомогательного напряжения, инвертирующие усилители, в качестве которых используются токовые зеркала, токовые выходы, источники опорного тока, шины источника питания, дополнительные транзисторы. 1 з.п. ф-лы, 16 ил.

Реферат

Предлагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и т.п.

В различных вычислительных и управляющих системах широко используются устройства, реализованные на основе RS-триггеров, которые имеют два состояния в зависимости от потенциальных сигналов на R или S-входах [1-20]. Входные и выходные сигналы в классических триггерах представляют собой высокий или низкий потенциалы, соответствующие логической «1» или логическому «0» булевой алгебры.

В работе [21], а также монографиях соавтора настоящей заявки [22-23] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство относится к этому типу вычислительных устройств.

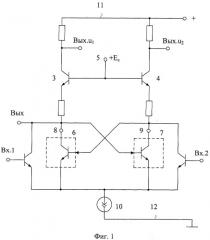

Ближайшим прототипом заявляемого устройства является RS-триггер, представленный в патенте RU № 2119716. Он содержит (фиг.1) R(1) и S(2) входы, выходные транзисторы 3 и 4, базы которых подключены к источнику вспомогательного напряжения 5, первый 6 и второй 7 инвертирующие усилители с соответствующими первым 8 и вторым 9 токовыми выходами, первый 10 источник опорного тока, первую 11 и вторую 12 шины источника питания.

Существенный недостаток известного RS-триггера состоит в том, что он, используя потенциальные двоичные сигналы, обладает усложненной структурой связей, нелинейностью рабочих режимов элементов и критичностью параметров структуры ПС, а также входных сигналов, что в конечном итоге приводит к снижению его быстродействия.

Основная задача предлагаемого изобретения состоит в создании устройства, в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов, определяемое состоянием входных токовых сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [22-23].

Поставленная задача решается тем, что в RS-триггере с многозначным внутренним представлением сигналов (фиг.1), содержащем R (1) и S (2) входы, выходные транзисторы 3 и 4, базы которых подключены к источнику вспомогательного напряжения 5, первый 6 и второй 7 инвертирующие усилители с соответствующими первым 8 и вторым 9 токовыми выходами, первый 10 источник опорного тока, первую 11 и вторую 12 шины источника питания, предусмотрены новые элементы и связи - в качестве первого 6 и второго 7 инвертиртирующих усилителей используются соответствующие первое 6 и второе 7 токовые зеркала, согласованные с первой 11 шиной источника питания, вход первого 6 токового зеркала соединен с коллектором первого 3 выходного транзистора, вспомогательный токовый выход 13 первого 6 токового зеркала соединен с эмиттером второго 4 выходного транзистора и S-входом (2) триггера, а также через второй 14 источник опорного тока связан со второй 12 шиной источника питания, вход второго 7 токового зеркала соединен с коллектором второго 4 выходного транзистора, вспомогательный токовый выход 15 второго 7 токового зеркала соединен с эмиттером первого 4 выходного транзистора и R-входом (1) триггера, а также через первый 10 источник опорного тока связан со второй 12 шиной источника питания, причем в качестве противофазных токовых выходов RS-триггера используются токовые выходы 8 и 9 первого 6 и второго 7 токовых зеркал.

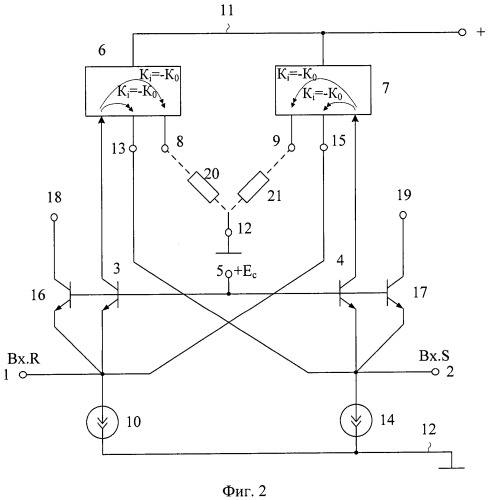

Схема RS-триггера - прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с пп.1 и 2 формулы изобретения для случая, когда первый 3 и второй 4 выходные транзисторы имеют n-р-n тип проводимости.

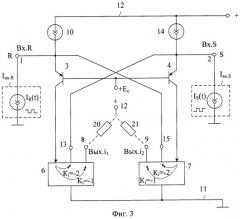

На чертеже фиг.3 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения для случая, когда первый 3 и второй 4 выходные транзисторы имеют р-n-р тип проводимости (примеры построения первого 6 и второго 7 токовых зеркал даны на чертеже фиг.9).

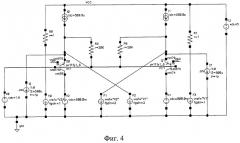

На чертеже фиг.4 приведена схема RS-триггера фиг.3 на идеальных элементах в среде Cadence на моделях SiGe инитегральных транзисторов.

На чертеже фиг.5 показан статический режим RS-триггера фиг.4 при входном токе на S входе I7=500 мкА.

На чертеже фиг.6 приведены временные диаграммы входных и выходных токов RS-триггера фиг.4.

На чертеже фиг.7 представлены временные диаграммы задержек в выходном токовом сигнале.

На чертеже фиг.8 представлена входная логика для построения RSC-триггера на базе заявляемого RS-триггера.

На чертеже фиг.9 показана схема RSC-триггера в среде MicroCap и функциональные обозначения его выводов на блоке «StageT» с входной логикой фиг.8 RS триггера фиг.3.

На чертеже фиг.10 показана функциональная схема и соединение выводов RS-триггера с блоком питания «Supply» (фиг.11), входным блоком преобразования потенциальных сигналов в токовые «Input» (фиг.12) и RS-триггером «StageT» (фиг.3).

На чертеже фиг.11 показан частный вариант построения цепей смещения потенциалов и питающих напряжений RS-триггера в виде блока питания «Supply».

На чертеже фиг.12 показан блок «Input» для формирования входных токовых сигналов RS-триггера фиг.3 из потенциальных сигналов. В большинстве случаев блок «Input» может отсутствовать.

На чертеже фиг.13 приведены временные диаграммы входных и выходных токовых сигналов одноступенчатого RSC-триггера фиг.9 (последовательность графиков: токи S, R, С, Q1, Q2).

На чертеже фиг.14 показан двухступенчатый RSC-триггер, реализуемый на основе заявляемого RS триггера.

На чертеже фиг.15 приведены временные диаграммы входных и выходных токовых сигналов двухступенчатого триггера фиг.14 (последовательность графиков: токи S, R, С, Q1_1, Q2_1, Ql_2, Q2_2).

На чертеже фиг.16 показан вариант построения Т-триггера на базе предлагаемого RS-триггера фиг.3.

RS-триггер с многозначным внутренним представлением сигналов фиг.2 содержит R (1) и S (2) входы, выходные транзисторы 3 и 4, базы которых подключены к источнику вспомогательного напряжения 5, первый 6 и второй 7 инвертирующие усилители с соответствующими первым 8 и вторым 9 токовыми выходами, первый 10 источник опорного тока, первую 11 и вторую 12 шины источника питания. В качестве первого 6 и второго 7 инвертиртирующих усилителей используются соответствующие первое 6 и второе 7 токовые зеркала, согласованные с первой 11 шиной источника питания, вход первого 6 токового зеркала соединен с коллектором первого 3 выходного транзистора, вспомогательный токовый выход 13 первого 6 токового зеркала соединен с эмиттером второго 4 выходного транзистора и S-входом (2) триггера, а также через второй 14 источник опорного тока связан со второй 12 шиной источника питания, вход второго 7 токового зеркала соединен с коллектором второго 4 выходного транзистора, вспомогательный токовый выход 15 второго 7 токового зеркала соединен с эмиттером первого 4 выходного транзистора и R-входом (1) триггера, а также через первый 10 источник опорного тока связан со второй 12 шиной источника питания, причем в качестве противофазных токовых выходов RS-триггера используются токовые выходы 8 и 9 первого 6 и второго 7 токовых зеркал.

Кроме этого, на чертеже фиг.2, в соответствии с п.2 формулы изобретения, в схему введены первый 16 и второй 17 дополнительные транзисторы, базы которых соединены с источником вспомогательного напряжения 5, эмиттеры соединены с эмиттерами соответствующих первого 3 и второго 4 выходных транзисторов, а коллекторы связаны с соответствующими вспомогательными токовыми выходами 18 и 19 устройства.

В качестве первого 6 и второго 7 токовых зеркал авторы рекомендуют использовать классические схемы, примеры построения которых даны на чертеже фиг.8 (элементы 26, 27) и чертеже фиг.9. Необходимый коэффициент передачи по току данных функциональных узлов (Ко=1÷2, фиг.2, фиг.3) устанавливается выбором соответствующих площадей эмиттерных переходов применяемых транзисторов.

Схема фиг.3 соответствует п.1 формулы изобретения, но реализована на р-n-р транзисторах 3 и 4.

Двухполюсники 20 и 21 моделируют свойства нагрузки RS-триггера по выходам 8 и 9. Входная логика RS-триггера фиг.8 реализована на транзисторах 22, 23, 24, 25, 26, 27. Входной логический сигнал данной логики подается на вход 28, а синхросигнал - на вход 29. Для установления статического режима логики используется вход 30, на который подается квант тока I0.

Рассмотрим работу предлагаемой схемы RS-триггера фиг.3.

Как известно, различают два режима работы триггера:

- режим установки триггера в некоторое состояние;

- режим хранения состояния.

Режим хранения состояния характеризуется отсутствием втекающих квантов тока на его входах Bx.R (1) и Bx.S (2). Если в состоянии «логический 1», например, транзистор 3 открыт, то в его коллекторной цепи протекает ток, равный кванту тока, задаваемый источником опорного тока 10. При этом первое 6 токовое зеркало через вспомогательный токовый выход 13 отбирает на себя квант тока источника опорного тока 14. Ток коллектора транзистора 4 отсутствует, следовательно, отсутствует и ток во втором 7 токовом зеркале. Поэтому его вспомогательный выход 15 не влияет на режим работы транзистора 3 и режим хранения RS-триггера, таким образом, поддерживается. При хранении триггером состояния «логического «0», когда открыт транзистор 4, процессы протекают аналогично.

Установка состояния RS-триггера производится подачей на один из его входов (R-вход (1) или S-вход (2)) управляющего сигнала в виде втекающего кванта тока. Пусть триггер находится в состоянии «логический 1». Подача кванта тока на R-вход (1) приводит к «пропаданию» тока через транзистор 3, он закрывается, при этом исчезает входной, а следовательно, и выходной ток токового зеркала 6 на вспомогательном выходе 13 и квант тока источника опорного тока 14 через транзистор 4 подается на вход токового зеркала 7. В результате квант тока опорного источника тока 10 направляется на вспомогательный выход 15 токового зеркала 7. По окончании управляющего кванта тока на R-входе (1) установленное состояние сохраняется. Переключение триггера из состояния «логического 0» в состояние «логический 1» с помощью управляющего кванта тока на S-входе (2) происходит аналогично.

Показанные на чертежах фиг.6, фиг.7, фиг.10, фиг.13, фиг.15 результаты моделирования подтверждают указанные свойства заявляемой схемы, которая может также реализовываться в базисе КМОП транзисторов. Следует отметить, что кратковременные импульсы на выходе триггера, возникающие в момент переключения входных сигналов, характерные и для других известных RS-триггеров, определяются различными временами переключения токовых зеркал и могут быть устранены в реальных схемах средствами технологии.

Таким образом, рассмотренные схемотехнические решения RS-триггеров характеризуются многозначным состоянием внутренних сигналов и двоичным представлением сигнала на его токовом выходе и могут быть положены в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 8.115.522 fig.2

2. Патент US 7.626.433

3. Патент US 7.236.029 fig.3

4. Патент US 6.268.752 fig.4

5. Патент US 6.486.720

6. Патентная заявка US 2002/0003443 fig.4

7. Патент US 6.714.060

8. Патент US 5.025.174

9. Патент US 5.945.858

10. Патент US 5.892.382 fig.2

11. Патент US 5.844.437 fig.2

12. Патент US 5.220.212

13. Патент US 5.815.019 fig.1

14. Патент US 5.541.544 fig.1

15. Патент US 5.001.361 fig.3

16. Патент US 5.969.556 fig.1

17. Патент US 4.156.819 fig.2

18. Патент US 4.779.009 fig.4

19. Патент US 4.309.625 fig.4

20. Патент US 3.305.728

21. Малюгин В.Д. Реализация булевых функций арифметическими полиномами.// Автоматика и телемеханика, 1982, №4, с.84-93.

22. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел.// Монография. - Таганрог: ТРТУ, 2001. - 147 с.

23. Чернов Н.И. Линейный синтез цифровых структур АСОИУ.// Учебное пособие. - Таганрог: ТРТУ, 2004 г. - 118 с.

1. RS-триггер с многозначным внутренним представлением сигналов, содержащий R (1) и S (2) входы, выходные транзисторы (3) и (4), базы которых подключены к источнику вспомогательного напряжения (5), первый (6) и второй (7) инвертирующие усилители с соответствующими первым (8) и вторым (9) токовыми выходами, первый (10) источник опорного тока, первую (11) и вторую (12) шины источника питания, отличающийся тем, что в качестве первого (6) и второго (7) инвертирующих усилителей используются соответствующие первое (6) и второе (7) токовые зеркала, согласованные с первой (11) шиной источника питания, вход первого (6) токового зеркала соединен с коллектором первого (3) выходного транзистора, вспомогательный токовый выход (13) первого (6) токового зеркала соединен с эмиттером второго (4) выходного транзистора и S-входом (2) триггера, а также через второй (14) источник опорного тока связан со второй (12) шиной источника питания, вход второго (7) токового зеркала соединен с коллектором второго (4) выходного транзистора, вспомогательный токовый выход (15) второго (7) токового зеркала соединен с эмиттером первого (4) выходного транзистора и R-входом (1) триггера, а также через первый (10) источник опорного тока связан со второй (12) шиной источника питания, причем в качестве противофазных токовых выходов RS-триггера используются токовые выходы (8) и (9) первого (6) и второго (7) токовых зеркал.

2. RS-триггер с многозначным внутренним представлением сигналов по п.1, отличающийся тем, что в схему введены первый (16) и второй (17) дополнительные транзисторы, базы которых соединены с источником вспомогательного напряжения (5), эмиттеры соединены с эмиттерами соответствующих первого (3) и второго (4) выходных транзисторов, а коллекторы связаны с соответствующими вспомогательными токовыми выходами (18) и (19) устройства.