Схема возбуждения линий сигнала сканирования и устройство отображения, включающее в себя данную схему

Иллюстрации

Показать всеГруппа изобретений относится к вычислительной технике и может быть использована в устройствах отображения. Техническим результатом является предотвращение возникновения неверного отображения за счет быстрого снижения уровня сигнала сканирования после того, как заканчивается период заряда в каждой строке. Схема возбуждения линий сигнала сканирования устройства отображения содержит множество сдвиговых регистров, причем каждый сдвиговый регистр включает в себя множество схем с двумя устойчивыми состояниями, причем синхросигнал, обеспеченный в каждый сдвиговый регистр в качестве синхросигнала возбуждения линии сигнала сканирования, изменяется между первым уровнем и вторым уровнем при конкретном тактировании, которое отличается от одного сдвигового регистра к другому, каждая схема с двумя устойчивыми состояниями содержит выходной узел, переключающий элемент управления выходом, блок включения первого узла, блок выключения первого узла. 3 н. и 18 з.п. ф-лы, 21 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к устройству отображения и к схеме возбуждения для устройства отображения, а более конкретно - к схеме возбуждения линий сигнала сканирования, которая включает в себя множество сдвиговых регистров для возбуждения линий сигнала сканирования, которые размещены в блоке отображения устройства отображения.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

В последние годы прогрессирующим образом развиваются монолитные структуры формирователя сигналов управления затвором (схем возбуждения линий сигнала сканирования), которые возбуждают линии затворной шины (линии сигнала сканирования) в жидкокристаллическом устройстве отображения. Традиционно формирователь сигналов управления затвором часто устанавливают на периферийной части подложки, которая составляет жидкокристаллическую панель, в качестве кристалла ИС (интегральной микросхемы). Однако в последние годы постепенно все чаще формируют формирователь сигналов управления затвором непосредственно на подложке. Такой формирователь сигналов управления затвором называют, например, «монолитным формирователем сигналов управления затвором». В жидкокристаллическом устройстве отображения, которое включает в себя монолитный формирователь сигналов управления затвором, в качестве элемента возбуждения традиционно используют тонкопленочный транзистор, в котором используют аморфный кремний (a-Si) (в дальнейшем называют «a-SiTFT»). Однако в последние годы в качестве эксперимента используют тонкопленочный транзистор, в котором используют микрокристаллический кремний (μc-Si) (в дальнейшем называют «μc-SiTFT»). Подвижность микрокристаллического кремния больше подвижности аморфного кремния, и дополнительно, μc-SiTFT формируют с помощью процесса, аналогичного процессу для a-SiTFT. Поэтому, основываясь на применении μc-SiTFT для элемента возбуждения, ожидается обеспечение уменьшения стоимости путем уменьшения площади рамки изображения и уменьшения количества кристаллов ИС формирователя, усовершенствование сборки готовых изделий, увеличение размера устройства отображения и тому подобное.

Блок отображения жидкокристаллического устройства отображения с активной матрицей включает в себя множество линий истоковой шины (линий видеосигнала), множество линий затворной шины и множество участков формирования пикселя, которые обеспечивают на соответствующих пересечениях множества линий истоковой шины и множества линий затворной шины. Участки формирования пикселя составляют массив пикселей с помощью размещения в форме матрицы. Каждый участок формирования пикселя включает в себя тонкопленочный транзистор, который является переключающим элементом, соединяющим вывод затвора с линией затворной шины, проходящей через соответствующее пересечение, и соединяющим вывод истока с линией истоковой шины, проходящей через данное пересечение, и включает в себя конденсатор пикселя, предназначенный для хранения значения напряжения пикселя. Дополнительно, жидкокристаллическое устройство отображения с активной матрицей снабжают формирователем сигналов управления затвором и формирователем сигналов управления истоком (схемой возбуждения линий видеосигнала) для возбуждения линии истоковой шины.

Видеосигнал, который указывает значение напряжения пикселя, передают с помощью линий истоковой шины, но по каждой из линий истоковой шины нельзя одновременно передавать видеосигнал, который указывает значения напряжения пикселей множества строк. Поэтому запись (заряд) видеосигналов в конденсатор пикселя в участках формирования пикселя, которые размещены в форме матрицы, выполняют последовательно строка за строкой. Следовательно, формирователь сигналов управления затвором формируют с помощью сдвигового регистра, который включает в себя множество каскадов, так что множество линий затворной шины последовательно выбирают в течение каждого предопределенного периода. Каждый каскад сдвигового регистра является схемой с двумя устойчивыми состояниями, которая находится в одном из двух состояний (в первом состоянии и во втором состоянии) в каждый момент времени и которая выводит сигнал, указывающий это состояние (в дальнейшем называют «сигнал состояния») в качестве сигнала сканирования. Активные сигналы сканирования последовательно выводят из множества схем с двумя устойчивыми состояниями в сдвиговом регистре, таким образом запись видеосигналов в конденсаторы пикселей выполняют последовательно строка за строкой, как описано выше.

Известна следующая относящаяся к настоящему изобретению информация о предшествующем уровне техники. Публикация выложенной японской патентной заявки № 2005-94335 раскрывает конфигурацию для устранения изменения пороговой характеристики транзистора, относящуюся к сдвиговому регистру, который обеспечивают в электронном устройстве, таком как устройство считывания изображения. Публикация выложенной японской патентной заявки № 2003-16794 раскрывает конфигурацию для предотвращения неправильной работы транзистора из-за паразитной емкости транзистора, относящуюся к сдвиговому регистру, который обеспечивают в электронном устройстве. Публикация выложенной японской патентной заявки № 2006-106394 раскрывает конфигурацию для работы двух формирователей сигналов управления затвором при использовании многофазных синхроимпульсов, относящуюся к жидкокристаллическому устройству отображения. Публикация выложенной японской патентной заявки № 2006-107692 раскрывает конфигурацию для предотвращения неправильной работы из-за изменения порогового напряжения транзистора, относящуюся к сдвиговому регистру, который обеспечивают на панели отображения. Публикация выложенной японской патентной заявки № 2006-127630 раскрывает конфигурацию для работы сдвигового регистра при использовании множества синхроимпульсов, относящуюся к сдвиговому регистру, который используют в жидкокристаллическом устройстве отображения. Публикация выложенной японской патентной заявки № 2001-52494 раскрывает конфигурацию для предотвращения уменьшения уровня выходного сигнала и изменения пороговой характеристики напряжения транзистора, относящуюся к сдвиговому регистру, который обеспечивают в электронном устройстве.

ДОКУМЕНТЫ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЕ ДОКУМЕНТЫ

[Патентный документ 1] Публикация выложенной японской патентной заявки № 2005-94335

[Патентный документ 2] Публикация выложенной японской патентной заявки № 2003-16794

[Патентный документ 3] Публикация выложенной японской патентной заявки № 2006-106394

[Патентный документ 4] Публикация выложенной японской патентной заявки № 2006-107692

[Патентный документ 5] Публикация выложенной японской патентной заявки № 2006-127630

[Патентный документ 6] Публикация выложенной японской патентной заявки № 2001-52494

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ПРОБЛЕМЫ, КОТОРЫЕ БУДУТ РЕШЕНЫ С ПОМОЩЬЮ ИЗОБРЕТЕНИЯ

Между прочим, в последние годы жидкокристаллического устройства отображения, которые включают в себя монолитный формирователь сигналов управления затвором, развиваются в сторону большого размера и более высокой разрешающей способности панели. Когда размер панели становится большим, нагрузочная емкость линии затворной шины соответственно увеличивается. В результате время, требуемое для снижения уровня сигнала сканирования (сигнала состояния), становится продолжительным. Следовательно, существует вероятность, что сигнал сканирования в определенной строке не снизится до низкого уровня (уровня, при котором тонкопленочный транзистор в участке формирования пикселя перейдет в состояние «выключено») до тех пор, когда начнется период заряда конденсатора пикселя следующей строки после завершения периода заряда конденсатора пикселя этой строки. В результате произойдет неверное отображение из-за смешивания цветов между цветом, который будут отображать в определенной строке, и цветом, который будут отображать в следующей строке. Дополнительно, время заряда одной линии становится коротким в соответствии с более высокой разрешающей способностью панели и поэтому происходит неверное отображение, относящееся к смешиванию цветов, которое описано выше. Возникновение неверного отображения, относящегося к смешиванию цветов, описано, основываясь на конфигурации схемы с двумя устойчивыми состояниями, которую включает в себя сдвиговый регистр, и на временной диаграмме сигналов ввода-вывода схемы с двумя устойчивыми состояниями. Последующее описание основано на предположении, что все тонкопленочные транзисторы, которые обеспечивают в схеме с двумя устойчивыми состояниями, являются транзисторами с каналом n-типа.

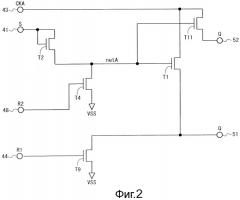

Фиг. 19 - принципиальная электрическая схема, на которой показан пример конфигурации схемы с двумя устойчивыми состояниями, которую включает в себя сдвиговый регистр формирователя сигналов управления затвором. Как показано на фиг. 19, схема с двумя устойчивыми состояниями включает в себя 12 тонкопленочных транзисторов T1-T12 и конденсатор CAP. Дополнительно, у схемы с двумя устойчивыми состояниями есть семь входных выводов 41-47 и два выходных вывода 51, 52 для вывода сигналов Q состояния в дополнение к входному выводу для напряжения VSS низкого уровня источника питания. Сигнал Q состояния, который выводят с выходного вывода 51, обеспечивают на линию затворной шины, соответствующую этой схеме с двумя устойчивыми состояниями, в качестве сигнала GOUT сканирования. Сигнал Q состояния, который выводят с выходного вывода 52, обеспечивают к схеме с двумя устойчивыми состояниями каскада, отличающегося от каскада этой схемы с двумя устойчивыми состояниями, в качестве сигнала Z для управления работой схемы с двумя устойчивыми состояниями другого каскада (в дальнейшем называют «управляющий сигнал другого каскада»).

Вывод затвора тонкопленочного транзистора T1, вывод истока тонкопленочного транзистора T2, вывод стока тонкопленочного транзистора T3, вывод стока тонкопленочного транзистора T4, вывод стока тонкопленочного транзистора T5, вывод затвора тонкопленочного транзистора T7 и вывод затвора тонкопленочного транзистора T11 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netA». Вывод затвора тонкопленочного транзистора T5, вывод истока тонкопленочного транзистора T6, вывод стока тонкопленочного транзистора T7 и вывод стока тонкопленочного транзистора T8 соединяют друг с другом. Область (соединения), в которой эти выводы соединяют друг с другом, для удобства называют «netB».

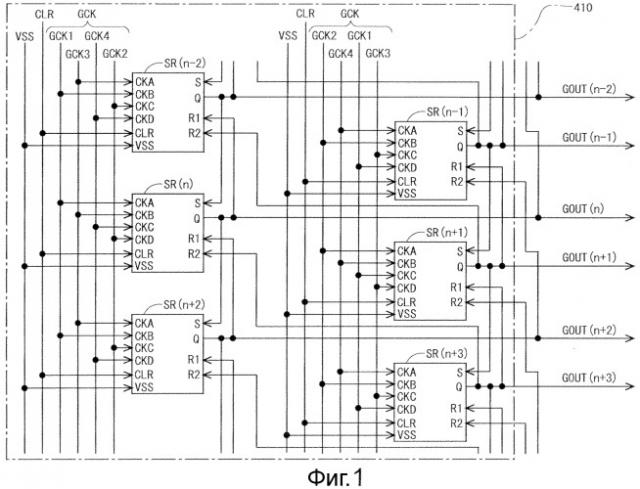

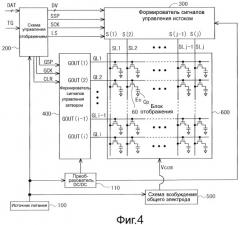

Описанный формирователь сигналов управления затвором, как предполагают, включает в себя два сдвиговых регистра. Сигнал GOUT сканирования, который выводят из схемы с двумя устойчивыми состояниями в одном сдвиговом регистре, обеспечивают на линии затворной шины нечетных строк, а сигнал GOUT сканирования, который выводят из схемы с двумя устойчивыми состояниями в другом сдвиговом регистре, обеспечивают на линии затворной шины четных строк. То есть можно полагать, что «эти два сдвиговых регистра реализуют один сдвиговый регистр, который последовательно выбирает каждую из множества линий затворной шины в блоке отображения». Поэтому в последующем описании конфигурацию, в которой объединяют множество (два в данном примере) сдвиговых регистров, которые обеспечивают для последовательного выбора каждой из множества линий затворной шины, называют «весь сдвиговый регистр».

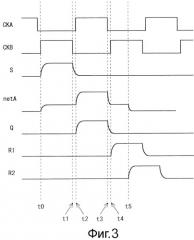

В вышеупомянутой конфигурации n-й каскад схемы с двумя устойчивыми состояниями всего сдвигового регистра работает следующим образом (см. фиг. 20). Первый синхроимпульс CKA, второй синхроимпульс CKB, третий синхроимпульс CKC и четвертый синхроимпульс CKD обеспечивают к входным выводам 43, 47, 45 и 46, соответственно. Управляющий сигнал Z(n-2) другого каскада, который выводят из схемы с двумя устойчивыми состояниями (n-2)-го каскада, обеспечивают к входному выводу 41 в качестве сигнала S установки. Управляющий сигнал Z(n+2) другого каскада, который выводят из схемы с двумя устойчивыми состояниями (n+2)-го каскада, обеспечивают к входному выводу 44 в качестве сигнала R сброса. Период с момента времени t1 до момента времени t2 и период с момента времени t3 до момента времени t4 не обеспечивают в общем случае или устанавливают как очень короткие периоды. На фиг. 20 период с момента времени t1 до момента времени t2 и период с момента времени t3 до момента времени t4 показаны как более продолжительные периоды, чем подлинные периоды. Для удобства момент времени t1 и момент времени t2 описаны отдельно, и момент времени t3 и момент времени t4 описаны отдельно. Это так же применяют к фиг. 3, фиг. 11 и фиг. 18 и к их описаниям.

Достигая момента времени t0, уровень сигнала S установки меняется с низкого уровня на высокий уровень. Соответственно, тонкопленочный транзистор T2 переходит в состояние «включено», конденсатор CAP заряжается, и уровень потенциала netA меняется с низкого уровня на высокий уровень. В результате тонкопленочные транзисторы T1, T11 переходят в состояние «включено». Достигая момента времени t1, уровень сигнала S установки меняется с высокого уровня на низкий уровень. Соответственно, тонкопленочный транзистор T2 переходит в состояние «выключено». В это время потенциал netA поддерживают с помощью конденсатора CAP, и поэтому его поддерживают на высоком уровне.

Достигая момента времени t2, уровень первого синхроимпульса CKA меняется с низкого уровня на высокий уровень. В это время, из-за того, что тонкопленочные транзисторы T1, T11 находятся в состоянии «включено», потенциалы сигналов Q состояния (потенциалы выходных выводов 51, 52) увеличиваются с увеличением потенциала входного вывода 43. Когда потенциал выходного вывода 51 увеличивается, потенциал netA также увеличивается через конденсатор CAP. В результате большое напряжение прикладывают к выводам затвора тонкопленочных транзисторов T1, T11, и потенциалы сигналов Q состояния увеличиваются до уровня, достаточного для того, чтобы линия затворной шины, соединенная с выходным выводом 51 схемы с двумя устойчивыми состояниями, перешла в выбранное состояние.

Достигая момента времени t3, уровень первого синхроимпульса CKA меняется с высокого уровня на низкий уровень. В это время, из-за того, что тонкопленочные транзисторы T1, T11 находятся в состоянии «включено», электрический ток между истоком и стоком тонкопленочных транзисторов T1, T11 постепенно уменьшается, основываясь на уменьшении потенциала входного вывода 43 и потенциалов сигналов Q состояния (потенциалов выходных выводов 51, 52). Поскольку конденсатор CAP обеспечивают между выходным выводом 51 и netA, как показано на фиг. 19, потенциал netA также уменьшается в соответствии с уменьшением потенциала выходного вывода 51. Однако из-за того, что потенциал netA уменьшается ориентировочно в соответствии с уменьшением потенциала выходного вывода 51, потенциал netA не уменьшается до низкого уровня, а поддерживается на высоком уровне.

Достигая момента времени t4, сигнал R сброса и второй синхроимпульс CKB изменяются с низкого уровня до высокого уровня, соответственно. Соответственно, тонкопленочные транзисторы T4, T9 и T10 переходят в состояние «включено». С помощью перехода тонкопленочного транзистора T4 в состояние «включено» потенциал netA уменьшается до низкого уровня. В это время потенциал выходного вывода 51 также уменьшается с помощью перехода тонкопленочных транзисторов T9, T10 в состояние «включено», данное уменьшение потенциала становится незначительным. Это происходит по следующей причине. Достигая момента времени t4, потенциал netA имеет низкий уровень и тонкопленочный транзистор T1 переходит в состояние «выключено». Поскольку в общем случае период с момента времени t3 до момента времени t4 не обеспечивают или устанавливают очень коротким, результат уменьшения потенциала выходного вывода 51, основанного на токе между истоком и стоком тонкопленочного транзистора T1, не получают.

Как описано выше, потенциал выходного вывода 51 уменьшается постепенно. То есть снижение уровня сигнала GOUT сканирования после того, как заканчивается период заряда в каждой строке, становится незначительным. Поэтому при тенденции к увеличению размера и повышению разрешающей способности панели увеличивается риск возникновения неверного отображения, относящегося к смешиванию цветов, которое описано выше.

Задачей настоящего изобретения является реализация формирователя сигналов управления затвором, который может вызывать быстрое снижение уровня сигнала сканирования после того, как период заряда в каждой строке заканчивается, для предотвращения возникновение неверного отображения, относящегося к смешиванию цветов.

СРЕДСТВО ДЛЯ РЕШЕНИЯ ПРОБЛЕМЫ

Первый аспект настоящего изобретения направлен на схему возбуждения линий сигнала сканирования устройства отображения, которая возбуждает множество линий сигнала сканирования, которые упорядочены в блоке отображения, причем упомянутая схема содержит:

множество сдвиговых регистров, причем каждый сдвиговый регистр включает в себя множество схем с двумя устойчивыми состояниями, имеющих первое состояние и второе состояние и соединенных последовательно друг с другом, и каждый сдвиговый регистр работает, основываясь на множестве синхросигналов, которые циклически повторяют первое изменение уровня для изменения со второго уровня на первый уровень и второе изменение уровня для изменения с первого уровня на второй уровень, и в каждом сдвиговом регистре данное множество схем с двумя устойчивыми состояниями последовательно переходят в первое состояние с помощью одного из множества синхросигналов, обеспечиваемых для каждой схемы с двумя устойчивыми состояниями в качестве синхросигнала возбуждения линии сигнала сканирования, причем

синхросигнал, тактирование изменения уровня которого отличается, обеспечен в каждый сдвиговый регистр в качестве синхросигнала возбуждения линии сигнала сканирования,

каждая схема с двумя устойчивыми состояниями включает в себя

выходной узел, который соединен с линией сигнала сканирования и который выводит сигнал состояния, который указывает либо первое состояние, либо второе состояние,

переключающий элемент управления выходом, имеющий второй электрод, на который обеспечен синхросигнал возбуждения линии сигнала сканирования, и третий электрод, соединенный с выходным узлом,

блок включения первого узла, который изменяет уровень первого узла, который соединен с первым электродом переключающего элемента управления выходом, на уровень «включено», основываясь на сигнале состояния, который выведен из схемы с двумя устойчивыми состояниями предшествующего каскада рассматриваемой схемы с двумя устойчивыми состояниями, и

блок выключения первого узла, который принимает сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями последующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения первого узла, и который изменяет уровень первого узла на уровень «выключено», основываясь на сигнале выключения первого узла, и

в каждой схеме с двумя устойчивыми состояниями после того, как рассматриваемая схема с двумя устойчивыми состояниями переходит в первое состояние, и после того, как синхросигнал возбуждения линии сигнала сканирования выполняет второе изменение уровня, уровень сигнала выключения первого узла меняется таким образом, что выполняется выключение первого узла, в течение периода с момента времени после того, как схема с двумя устойчивыми состояниями следующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в сдвиговом регистре, который включает в себя рассматриваемую схему с двумя устойчивыми состояниями, переходит в первое состояние, до момента времени, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения

каждая схема с двумя устойчивыми состояниями дополнительно включает в себя блок выключения выходного узла, который принимает сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями последующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения выходного узла, и который выключает выходной узел, основываясь на сигнале выключения выходного узла, и

в каждой схеме с двумя устойчивыми состояниями после того, как рассматриваемая схема с двумя устойчивыми состояниями переходит в первое состояние, уровень сигнала выключения первого узла меняется таким образом, что выполняется выключение первого узла в течение периода с момента времени после момента времени, когда уровень сигнала выключения выходного узла меняется таким образом, что выполняется выключение выходного узла, до момента времени, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения

каждая схема с двумя устойчивыми состояниями дополнительно включает в себя

переключающий элемент управления первым узлом, имеющий второй электрод, соединенный с первым узлом, и третий электрод, к которому приложен потенциал уровня «выключено», и

блок управления вторым узлом, который управляет потенциалом второго узла, который соединен с первым электродом переключающего элемента управления первым узлом, основываясь на другом синхросигнале, чем синхросигнал возбуждения линии сигнала сканирования из множества синхросигналов, и на потенциале первого узла.

Согласно четвертому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит два сдвиговых регистра, каждый из которых идентичен упомянутому сдвиговому регистру,

упомянутые два сдвиговых регистра поочередно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования, и

сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями третьего каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечен для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя упомянутые два сдвиговых регистра, в качестве сигнала выключения первого узла.

Согласно пятому аспекту настоящего изобретения, в четвертом аспекте настоящего изобретения

тактирования, когда выполняется вывод сигнала состояния в первом состоянии из упомянутых двух сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны двум периодам горизонтального сканирования.

Согласно шестому аспекту настоящего изобретения, в четвертом аспекте настоящего изобретения

упомянутые два сдвиговых регистра работают, основываясь на первом синхросигнале, который обеспечен для схемы с двумя устойчивыми состояниями первого каскада одного из сдвиговых регистров в качестве синхросигнала возбуждения сигнала сканирования, втором синхросигнале, имеющем фазу, сдвинутую относительно фазы первого синхросигнала на 180 градусов, третьем синхросигнале, имеющем фазу, задержанную относительно фазы первого синхросигнала на 90 градусов, и четвертом синхросигнале, имеющем фазу, сдвинутую относительно фазы третьего синхросигнала на 180 градусов.

Согласно седьмому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит m сдвиговых регистров, каждый из которых идентичен упомянутому сдвиговому регистру,

m сдвиговых регистров последовательно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования,

сигнал состояния, который выведен из схемы с двумя устойчивыми состояниями k-го каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечен для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя m сдвиговых регистров, в качестве сигнала выключения первого узла, и

зависимость между m и k соответствует следующему уравнению: m+1≤k≤2m-1, где m является целым числом, которое равно или больше двух.

Согласно восьмому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения

тактирования, когда выполняется вывод сигнала состояния в первом состоянии из m сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны m периодам горизонтального сканирования.

Согласно девятому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения

соединение для сигнала, который будет обеспечен для каждой схемы с двумя устойчивыми состояниями в качестве сигнала выключения первого узла, сформировано так, чтобы оно ответвлялось от соединения для сигнала, который будет обеспечен для схемы с двумя устойчивыми состояниями (k-m)-го каскада после рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения выходного узла.

Согласно десятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

соединение для передачи множества сигналов возбуждения для работы множества сдвиговых регистров обеспечены вместе для множества сдвиговых регистров, причем множество сигналов возбуждения включает в себя множество синхросигналов.

Согласно одиннадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые все имеют канал того же самого типа.

Согласно двенадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из аморфного кремния.

Согласно тринадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из микрокристаллического кремния.

Согласно четырнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из поликристаллического кремния.

Согласно пятнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения

переключающие элементы, которые включены в каждую схему с двумя устойчивыми состояниями, являются тонкопленочными транзисторами, которые выполнены из оксидных полупроводников.

Шестнадцатый аспект настоящего изобретения направлен на устройство отображения, которое включает в себя блок отображения и содержит схему возбуждения линий сигнала сканирования согласно первому аспекту настоящего изобретения.

Семнадцатый аспект настоящего изобретения направлен на способ возбуждения для возбуждения множества линий сигнала сканирования, упорядоченных в блоке отображения, с помощью схемы возбуждения линий сигнала сканирования, включающей в себя множество сдвиговых регистров, причем каждый сдвиговый регистр включает в себя множество схем с двумя устойчивыми состояниями, имеющих первое состояние и второе состояние и соединенных последовательно друг с другом, и каждый сдвиговый регистр работает, основываясь на множестве синхросигналов, которые циклически повторяют первое изменение уровня для изменения со второго уровня на первый уровень и второе изменение уровня для изменения с первого уровня на второй уровень, и в каждом сдвиговом регистре множество схем с двумя устойчивыми состояниями последовательно переходят в первое состояние с помощью одного из множества синхросигналов, обеспечиваемых для каждой схемы с двумя устойчивыми состояниями в качестве синхросигнала возбуждения линии сигнала сканирования, при этом упомянутый способ содержит:

первый этап возбуждения, на котором изменяют состояние каждой схемы с двумя устойчивыми состояниями со второго состояния на первое состояние; и

второй этап возбуждения, на котором изменяют состояние каждой схемы с двумя устойчивыми состояниями с первого состояния на второе состояние, причем

синхросигналы, тактирование изменения уровня которых отличается, обеспечивают в каждый сдвиговый регистр в качестве синхросигнала возбуждения линии сигнала сканирования,

каждая схема с двумя устойчивыми состояниями включает в себя

выходной узел, который соединяют с линией сигнала сканирования, и который выводит сигнал состояния, который указывает или первое состояние как уровень «включено», или второе состояние как уровень «выключено»,

переключающий элемент управления выходом, имеющий второй электрод, на который обеспечивают синхросигнал возбуждения линии сигнала сканирования, и третий электрод, соединенный с выходным узлом, и

первый узел, соединенный с первым электродом переключающего элемента управления выходом, и

в каждой схеме с двумя устойчивыми состояниями

первый этап возбуждения включает в себя

этап включения первого узла, на котором изменяют уровень первого узла до уровня «включено», основываясь на сигнале состояния, который выводят из схемы с двумя устойчивыми состояниями предшествующего каскада рассматриваемой схемы с двумя устойчивыми состояниями, и

этап включения сигнала состояния, на котором изменяют уровень сигнала состояния до уровня «включено», основываясь на первом изменении уровня синхросигнала возбуждения линии сигнала сканирования,

второй этап возбуждения включает в себя

этап выключения сигнала состояния, на котором изменяют уровень сигнала состояния до уровня «выключено», основываясь на втором изменении уровня синхросигнала возбуждения линии сигнала сканирования, и

этап выключения первого узла, на котором принимают сигнал состояния, который выводят из схемы с двумя устойчивыми состояниями последующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в качестве сигнала выключения первого узла, и изменяют уровень первого узла до уровня «выключено», основываясь на сигнале выключения первого узла, и

после того, как этап включения сигнала состояния заканчивают, и после того, как начинают этап выключения сигнала состояния, начинают этап выключения первого узла в течение периода с момента времени после того, как схема с двумя устойчивыми состояниями следующего каскада рассматриваемой схемы с двумя устойчивыми состояниями в сдвиговом регистре, который включает в себя рассматриваемую схему с двумя устойчивыми состояниями, завершает этап включения сигнала состояния, до момента времени, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня.

Согласно восемнадцатому аспекту настоящего изобретения, в семнадцатом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит два сдвиговых регистра, каждый из которых идентичен упомянутому сдвиговому регистру,

упомянутые два сдвиговых регистра поочередно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования, и

сигнал состояния, который выводят из схемы с двумя устойчивыми состояниями третьего каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечивают для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя упомянутые два сдвиговых регистра, в качестве сигнала выключения первого узла.

Согласно девятнадцатому аспекту настоящего изобретения, в восемнадцатом аспекте настоящего изобретения

тактирования, когда выполняют вывод сигнала состояния в первом состоянии из упомянутых двух сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны двум периодам горизонтального сканирования.

Согласно двадцатому аспекту настоящего изобретения, в семнадцатом аспекте настоящего изобретения

схема возбуждения линий сигнала сканирования содержит m сдвиговых регистров, каждый из которых идентичен упомянутому сдвиговому регистру,

m сдвиговых регистров последовательно выводят сигнал состояния в первом состоянии для каждой из множества линий сигнала сканирования,

сигнал состояния, который выводят из схемы с двумя устойчивыми состояниями k-го каскада после рассматриваемой схемы с двумя устойчивыми состояниями, обеспечивают для каждой схемы с двумя устойчивыми состояниями во всем сдвиговом регистре, который включает в себя m сдвиговых регистров, в качестве сигнала выключения первого узла, и

зависимость между m и k соответствует следующему уравнению:

m+1≤k≤2m-1,

где m является целым числом, которое равно или больше двух.

Согласно двадцать первому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения

тактирования, когда выполняют вывод сигнала состояния в первом состоянии из m сдвиговых регистров, сдвинуты на период, приблизительно равный одному периоду горизонтального сканирования, и

период от того, когда синхросигнал возбуждения линии сигнала сканирования выполняет первое изменение уровня, до того, когда упомянутый сигнал выполняет второе изменение уровня, и период от того, когда упомянутый сигнал выполняет второе изменение уровня, до того, когда упомянутый сигнал выполняет первое изменение уровня, являются периодами, которые приблизительно равны m периодам горизонтального сканирования.

РЕЗУЛЬТАТ ИЗОБРЕТЕНИЯ

Согласно первому аспекту настоящего изобретения, в каждой схеме с двумя устойчивыми состояниями множества сдвиговых регистров, которые составляют схему возбуждения линий сигнала сканирования, первый узел поддерживают в состоянии уровня «включено» в течение периода, который соответствует сдвигу по фазе между каждым из сдвиговых регистров, после того, как потенциал выходного узла начинает уменьшаться, основываясь на изменении синхросигнала возбуждения линии сигнала сканирования с первого уровня до второго уровня. Поэтому переключающий элемент управления выходом поддерживают в состоянии «включено» в течение периода, который соответствует сдвигу по фазе между каждым из сдвиговых регистров, после того, как потенциал выходного узла начинает уменьшаться. Соответственно, результат уменьшения потенциала выходного узла, основанного на изменении уровня синхросигнала возбуждения линии сигнала сканирования, получают в достаточной степени. Поэтому потенциал сигнала сканирования, который выводят из каждого выходного узла, быстро уменьшается до уровня «выключено», после того, как выбранный период соответствующей линии сигнала сканирования заканчивается. В результате можно предот