Интегрированная в сбис технологии кмоп/кни с n+ - и p+ - поликремниевыми затворами матрица памяти mram с магниторезистивными устройствами с передачей спинового вращения

Иллюстрации

Показать всеИзобретение относится к схемам матриц ячеек памяти MRAM (Magnetic Random Access Memory) с передачей спинового значения. Технический результат заключается в увеличении плотности размещения отдельных транзисторных структур технологии МОП и запоминающих ячеек матрицы, а также повышении стойкости к нестационарным переходным процессам от воздействия ионизирующих излучений. Устройство матричного типа содержит множество устройств на магнитных туннельных переходах («MTJ») с передачей спинового вращения, организованных в матрицу запоминающих ячеек; устройство организации записи/чтения информации для конкретного устройства «MTJ», соединенное с соответствующими устройствами «MTJ» для изменения полярности намагниченности свободного слоя каждого устройства «MTJ», блок усилителя чтения данных на выходе матрицы запоминающих ячеек, выполненный с возможностью обнаруживать уровень сигнала и формировать двоичный выходной сигнал на основе сравнения уровня сигнала в разряде матрицы запоминающих ячеек в компараторе. При формировании топологии устройство «MTJ» выполнено в виде эллипса с осью легкого намагничивания, направленной по его большой оси. 11 з.п. ф-лы, 37 ил., 11 табл.

Реферат

Предлагаемое изобретение относится к области вычислительной техники, в частности к схемам матриц ячеек памяти «MRAM» («Magnetic Random Access Memory»), использующей технологию магниторезистивной оперативной памяти с передачей спинового вращения («STT-MRAM») так называемым спин-вентильным запоминающим устройствам. «STT-MRAM» также известна как «RAM» («Random Access Memory») с передачей спинового вращательного момента («Spin Transfer Torque RAM», «STT-RAM»), «RAM» с переключением намагничивания и передачей спинового вращательного момента («Spin Torque Transfer Magnetization Switching RAM», или «Spin-RAM»), «RAM» с передачей спинового момента («SMT-RAM»).

Известна программируемая в жестких условиях эксплуатации вентильная матрица, которая является полупроводниковым устройством, включающая в себя компоненты программируемых логических схем (ПЛИС), называемых «логическими блоками», и программируемые межсоединения, или интерфейсы. Логические блоки могут быть запрограммированы для выполнения функции элементарных логических вентилей, например «AND» и «XOR» или более сложных комбинационных функций, например декодеров или простых математических функций. В большинстве матриц «FPGA» («Field Programmable Gate Arrey») логические блоки также включают в себя элементы памяти, которые могут быть простыми триггерами или более полными блоками памяти. Иерархия программируемых интерфейсов обеспечивает возможность соединения логических блоков так, как это необходимо разработчику систем. После того как матрица «FPGA» изготовлена, разработчик - схемотехник может использовать программирование для реализации многих различных логических функций, тем самым, конструируя «программируемое в условиях эксплуатации» устройство. Матрица «PLA» («Programmable Logic Arrey») аналогична «FPGA», за исключением того, что «PLA» модифицируется, или «программируется», на этапе изготовления интегральных микросхем (ИМС) посредством изменений в одной или двух масках. Так «PLA», имеющая элементы флэш-памяти «EPROM», как правило, формируется из двух логических матриц, матрицы ввода и матрицы вывода /1/. Каждая матрица имеет входы, которые присоединяются к выводам затвора транзисторов в пределах логической матрицы, и обеспечивает выходы в узлы вывода. Входы матрицы ввода являются входами программируемой логической матрицы. Выходы матрицы ввода являются промежуточными узлами. Входы матрицы вывода соединены с промежуточными узлами. Выходы матрицы вывода являются выходами «PLA». Матрица ввода может обеспечивать функцию «AND», а матрица вывода может обеспечивать функцию «OR». В качестве альтернативы, обе матрицы могут обеспечивать функцию «NOR». Эти функции определяются типом и возможностью подключения используемых транзисторов и сигналами, применяемыми к их затворам. Конфигурация «NOR-NOR» имеет конкретные преимущества за счет того, что ее проще всего реализовать в логической схеме технологии КМОП. При реализации функции «NOR» существует некоторое количество транзисторов, равное количеству входов, соединенных параллельно. Подключение дополнительных параллельных транзисторов для размещения дополнительных входов не влияет на скорость функционирования этапа.

Известна матрица «FPGA» с запоминающими магнитными элементами или ячейками памяти «MRAM» /2/. Информация о соединении записывается в запоминающие магнитные элементы. Информация о соединении последовательно вводится и сохраняется в сдвиговых регистрах, которые соответствуют запоминающим магнитным элементам. При включении электропитания информация о соединении, хранящаяся в запоминающих магнитных элементах, фиксируется посредством элементов-триггеров и выводится в переключающие схемы для соединения логических блоков «FPGA».

Магниторезистивная оперативная память («MRAM») является технологией энергонезависимой памяти, время отклика (чтение/запись) которой сопоставимо с энергозависимой памятью. В отличие от технологий общепринятой «RAM», в которой данные хранятся как электрические заряды или электрические токи, «MRAM» использует магнитные элементы.

Объединить магнитный элемент памяти и магниторезистивный элемент считывания удалось в памяти «CRAM» («Crosstie Random Access Memory»). При этом измерялись небольшие различия в сопротивлении ячеек в узловых точках, что позволяло различать «0» и «1». Разница сопротивлений не превышала 0,1%, что было достаточно для демонстрации эффекта, но крайне мало для его практического использования.

В 1982 году было предложено располагать ячейки магнитной памяти непосредственно на кремниевой пластине. Тогда же были предприняты попытки изготовить магнитную память в едином технологическом процессе с электронной схемой управления. Этот принцип сохранен в «MRAM» до сих пор, поскольку связи между матрицей ячеек памяти и схемой управления достаточно сложны.

Ячейки памяти располагаются на поверхности кремниевого кристалла и соединяются сверху и снизу системой проводников, через которые селективно управляют их состоянием (производят запись или считывание).

«MRAM» можно разместить непосредственно на кристалле процессора, при этом максимально сокращается длина соединительных проводников и повышается скорость ее работы. Считается, что по сравнению с существующими приборами памяти, при использовании «MRAM» может быть достигнуто 1000-кратное увеличения плотности записи /3/.

Физической основой «MRAM» являются субмикронные многослойные структуры из магнитных и немагнитных материалов, изменяющие свое магнитное состояние и электропроводность под действием внешнего магнитного поля. Два противоположных направления намагниченности одного из магнитных слоев соответствуют записи логических «1» и «0». На кристалле располагается множество ячеек, способных сохранять цифровую информацию без питания. Рабочие характеристики «MRAM» улучшаются при снижении размеров ячеек памяти.

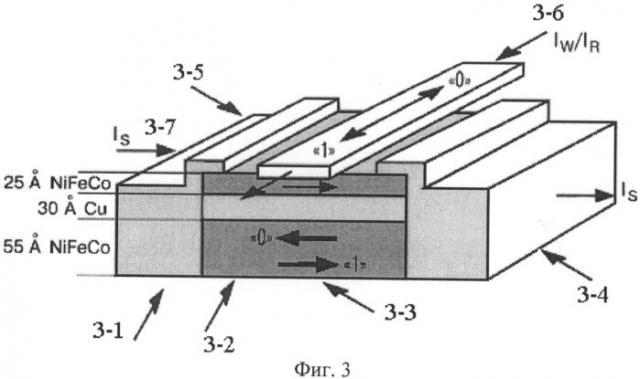

Ячейка состоит из двух сверхтонких ферромагнитных пленок, разделенных слоем материала с низкой проводимостью (например, TaN), а также пленок сложного состава, вытравленных в виде плоских проводников (полосок, шин) (Фиг.1).

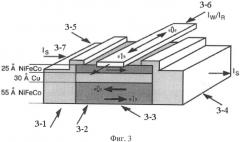

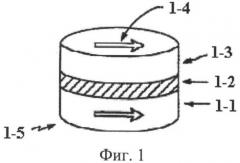

Запись информации производится пропусканием тока, который намагничивает верхний слой NiFeCo в прямом (параллельном) (Фиг.1) или обратном (антипараллельном) направлении (Фиг.2) одновременно по двум линиям - записи («word» - шина записи/считывания слов («ШЗС») и данных («sense» - шина данных «ШД»), на пересечении которых находится данная ячейка (Фиг.3). Величина токов подбирается таким образом, что изменение состояния ячейки происходит только при совместном их действии. Напряженность магнитного поля, создаваемого токами в других ячейках, недостаточна для изменения их состояния. При считывании состояние ячейки («0» или «1») определяют по изменению сопротивления ячейки при пропускании тока, постоянного по «ШД» через все включенные последовательно ячейки (Фиг.4), и тока считывания по «ШЗС». Ток считывания «iч» создает магнитное поле, совпадающее или противоположное полю магнитных слоев, при этом угол поворота магнитного вектора различен для «0» или «1».

Сплав «никель-пермаллой» имеет нормальное анизотропное магнитосопротивление (ARM) около 2%. При современных методах считывания максимальная разница в напряжениях для состояний «0» или «1» составляет 0,5%. В реальной ячейке для приемлемых токов считывания разность напряжений составляет 0,5…1 мВ. При таких уровнях сигнала работает 256 Кбайт «MRAM» фирмы «Honeywell», обеспечивая скорость считывания 250 нс. Время записи составляет 100 мс и может быть улучшено /4/.

Открытое в 1988 году при исследовании свойств сверхтонких многослойных структур, состоящих из чередующих слоев ферромагнитного (Fe, Co) и немагнитного (Cu, Ag) или антиферромагнитного (Cr, Mn) металлов гигантское магнитосопротивление (GMR) позволило значительно повысить скорость считывания и записи информации в запоминающих ячейках «MRAM». Толщина каждого слоя составляла несколько десятков ангстрем. Минимально возможное число слоев, при котором наблюдается эффект, это три - два ферромагнитных слоя, разделенных немагнитной прослойкой.

В 1991 году была разработана многослойная ячейка памяти с магнитосопротивлением 6%, состоящая из магнитных пленок и медного промежуточного слоя. В новую конструкцию были внесены некоторые изменения. Поскольку время считывания сокращается пропорционально квадрату амплитуды сигнала, трехкратное увеличение магнитосопротивления ведет к 9-кратному сокращению времени считывания. При использовании магнитных материалов для реализации GMR были разработаны «MRAM» со временем считывания до 50 нс.

В настоящее время наиболее перспективными считаются два основных элемента - псевдоспиновый вентиль («PSV» - «Psevdo Spin Valve») и ячейки на основе туннельного эффекта («SDT» - «Spin Depending Tunneling» или MTJ - «Magnetic Tunnel Junction»). Конструкция ячейки памяти в виде вентиля «PSV» позволила значительно повысить уровень сигналов считывания в «MRAM», в 8 раз сократить время считывания и по быстродействию поставить «MRAM» в один ряд с полупроводниковой памятью. В приборах магнитной памяти для хранения цифровой информации используется явление гистерезиса. На Фиг.3 показана упрощенная схема памяти на магнитных элементах. Малая величина полезного сигнала обуславливает требования, предъявляемые к процедуре записи и считывания в ячейку памяти.

Варианты структуры запоминающей ячейки «MRAM» приведены в Приложении «А».

В ПЛИС, использующей технологию «STT-MRAM», принятой за прототип /4/, вариант осуществления изобретения может включать в себя программируемую логическую матрицу, содержащую: множество устройств на «MTJ» с передачей спинового вращения, организованных в матрицу, и множество программируемых источников, соединенных с соответствующими устройствами «MTJ», для изменения полярности свободного слоя каждого устройства «MTJ», причем первая группа устройств «MTJ» организована в матрицу ввода, вторая группа устройств «MTJ» организована в матрицу вывода, и матрица ввода и матрица вывода объединены для формирования логической функции на основе относительных полярностей свободного слоя каждого устройства «MTJ».

Другой вариант осуществления может включать в себя способ реализации логической схемы в матрице, содержащий: программирование каждого из множества устройств «MTJ», организованных в матрицу, в состояние высокого или низкого сопротивления, причем каждое устройство «MTJ» программируется первым программируемым источником, соединенным со стороной свободного слоя (СС) выбранного устройства «MTJ», и программируемым источником, соединенным со стороной фиксированного слоя (ФС) выбранного устройства «MTJ», организацию первой группы устройств «MTJ» в столбцы и строки матрицы ввода, организацию второй группы устройств «MTJ», по меньшей мере, в один столбец в матрице вывода, причем выходы каждой строки соединены с устройствами «MTJ», по меньшей мере, в одном столбце, и определение логической функции на основе относительных сопротивлений каждого устройства «MTJ».

Недостатком такой схемы организации устройства «PLA» является демонстрация принципов программирования СС и ФС элементов «MTJ» для суперпозиции определенной заданной логической функции на выходе «PLA». Могут быть разработаны альтернативные варианты осуществления, не отступая от содержания и объема изобретения /4/. Кроме того, известные элементы изобретения не были подробно описаны или были опущены для исключения затруднения в понимании соответствующих деталей вариантов реализации изобретения. Слово «иллюстративный» там использовано в значении «служащий в качестве примера, образца или иллюстрации». Любой вариант реализации, приведенный в описании /4/ как «иллюстративный», не должен обязательно рассматриваться как предпочтительный или имеющий преимущества перед другими вариантами осуществления. Таким же образом, термин «варианты осуществления изобретения» не требует, чтобы все варианты осуществления изобретения включали в себя рассматриваемый признак, преимущество или режим функционирования.

Варианты осуществления изобретения используют элементы магниторезистивной оперативной памяти «STT-MRAM», составляющих часть матрицы запоминающего устройства. «STT-MRAM» использует электроны, которые становятся спин-поляризованными, так как электроны проходят через тонкую пленку (спиновый фильтр). Во время операции записи спин-поляризованные электроны влияют вращающим моментом на СС, который может переключать полярность намагниченности СС. Операция чтения аналогична общепринятой в «MRAM» в том смысле, что ток используется для идентификации сопротивления логического состояния запоминающего элемента «MTJ», как обсуждалось выше.

На Фиг.3 приведена одноразрядная ячейка памяти технологии «PSV-MRAM» для лучшего понимания процесса программирования элемента «PSV». Логическое состояние элемента «PSV» в «PSV-MRAM» записывается электрически, в противоположность магнитной записи в общепринятой «MRAM».

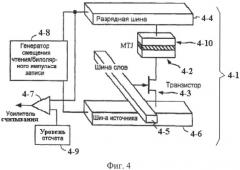

На Фиг.4 приведена более подробная схема ячейки «STT-MRAM» для дальнейшего обсуждения операций чтения/записи. В отличие от «MRAM», операция записи в «STT-MRAM» является электрической. Цепи чтения/записи формируют напряжение записи между разрядной шиной и шиной источника. В зависимости от полярности напряжения между разрядной шиной и шиной источника может быть изменена полярность магнитного СС элемента «MTJ», и, соответственно, в ячейку «STT-MRAM» может быть записано определенное логическое состояние. Таким же образом, во время операции чтения формируется ток чтения, который протекает между разрядной шиной и шиной источника через элемент «MTJ». Когда току дают возможность протекать через транзистор, сопротивление (логическое состояние) элемента «MTJ» может быть определено на основе разности напряжений между разрядной шиной и шиной источника, которое сравнивается с началом отсчета и затем усиливается усилителем считывания. Это функционирование и конструкция ячейки памяти известны в данной области техники. Дополнительные подробности представлены, например, в /5/ и в Приложении «А».

Практически отсутствуют публикации о патентоохраняемых технических решений устройств «STT-MRAM».

Техническим результатом заявляемого устройства является интегрированная в СБИС технологии КМОП/КНИ с n+- и p+-поликремниевыми затворами матрица памяти «STT-MRAM».

Технический результат достигается тем, что решением задачи создания матрицы памяти «STT-MRAM» является устройство матричного типа, управляемое внешними сигналами записи/чтения информации и ввода/вывода данных, содержащее:

множество устройств на магнитных туннельных переходах («MTJ») с передачей спинового вращения, организованных в матрицу запоминающих ячеек;

устройство организации записи/чтения информации для конкретного устройства «MTJ», включающее:

блок ввода/вывода данных,

блок дешифратора адресного кода,

блок управления ключами шин записи слова,

блок ключей шин записи слова,

блок управления ключами разрядных шин,

блок ключей разрядных шин,

блок управления записью/чтением данных,

блок формирователя тока записи/чтения,

источники тока записи слова, тока записи разряда, тока чтения в составе блока формирователя тока записи/чтения,

шины разрядные, шины записи слова, шины чтения слова, двунаправленную шину ввода/вывода данных,

соединенные с соответствующими устройствами «MTJ» для изменения полярности намагниченности свободного слоя каждого устройства «MTJ», причем блоки устройства организации записи/чтения информации объединены соответствующими шинами для формирования логического состояния на основе относительных полярностей свободного слоя и фиксированного слоя каждого устройства «MTJ»,

блок усилителя чтения данных на выходе матрицы запоминающих ячеек, соединенный с двунаправленной шиной ввода/вывода данных по цепям «UP:0-15, Э» и «DЧ:0-15», выполненный с возможностью обнаруживать уровень сигнала на конце «А» в шине разрядной и формировать двоичный выходной сигнал «DЧ:0-15» на основе сравнения уровня сигнала в разряде матрицы запоминающих ячеек в компараторе, включенным в состав блока усилителя чтения данных, с эталонным пороговым уровнем сигнала («UЭ»),

С целью придания исходной анизотропии намагниченности свободного и фиксированного ферромагнитного слоев каждой запоминающей ячейки матрицы памяти «STT-MRAM» при формировании топологи устройства «MTJ» оно выполнено в виде эллипса с осью легкого намагничивания, направленной по его большой оси,

С целью изменения полярности намагниченности верхнего свободного слоя устройства «MTJ» внешнее управляющее матрицей памяти «STT-MRAM» устройство соединено по цепям сигнала разрешения записи информации ( W E ¯ ), сигнала разрешения считывания информации ( O E ¯ ), сигнала разрешения выработки сигнала первого цикла работы ( C E ¯ 1 ), сигнала разрешения выработки сигнала второго цикла ( C E ¯ 2 ) с блоком управления записью/чтением данных, по цепям ввода/вывода данных внешнее управляющее устройство по двунаправленной 16-разрядной шине данных («DIO:0-15») соединено с блоком ввода/вывода данных, по 12-разрядной адресной шине («A:0-11») внешнее устройство соединено с блоком дешифратора адреса с возможностью реализации процедуры записи/чтения в два цикла путем последовательной подачи внешних разрешающих сигналов « C E ¯ 1 » и « C E ¯ 2 » на соответствующие входы блока управления записью/чтением данных (Фиг.16 и Фиг.17).

Для исключения статистического разброса величины магнитного момента нижнего закрепленного ферромагнитного слоя в каждом устройстве «MTJ», концы «А» разрядной шины «ШР-А:0-15, Э» этого устройства в режиме чтения данных соединены с одним из входов компаратора, а второй вход компаратора соединен с шиной записи/чтения, в которой генерируется выходной сигнал «UЭ» эталонного устройства «MTJ», расположенного в центре каждого слова матрицы запоминающих ячеек («МЗЯ») (Фиг.34).

Для организации постоянного запоминающего устройства (ПЗУ) емкостью 64 кбит с 16-и разрядной двунаправленной шиной ввода/вывода данных «DIO:0-15», она содержит множество запоминающих ячеек («ЗЯ») на основе устройств «MTJ», которые могут быть электрически приведены в состояние высокого сопротивления «RB» или низкого сопротивления « RH».

Для обеспечения обращения к выбранному слову «МЗЯ», выходы «C:i» блока дешифратора адреса («Дш.А»), где i=0…4095 равно численному значению кода адреса, соединены с входом блока управления ключами шины записи слова («БУК ШЗС») и одновременно, через блок ключей записи слова («БК ШЗС»), с шиной записи слова («ШЗС:i») «МЗЯ», где i=0…4095 равно численному значению кода адреса устройства «MTJ», с возможностью выработки на одном из выходов «C:i» сигнала с уровнем логической «1» при поступлении на вход «Дш.А» по шине «A:0-11» от внешнего устройства параллельного адресного кода (Фиг.16).

С целью обеспечения формирования сигналов 1-го и 2-го цикла записи (« З Т 1 ¯ », « З Т 2 ¯ »), 1-го и 2-го циклов чтения (« Ч Т 1 ¯ », « Ч Т 2 ¯ ») и сигналов записи «З» и чтения «Ч» внешнее управляющее устройство соединено с входом блока управления записью/чтением («БУЗЧ») по цепям: сигнала разрешения записи данных « W E ¯ » с возможностью, после его инвертирования, поступления в виде сигнала «З» на вход блока формирователя токов записи/чтения («ФТЗЧ»), сигнала разрешения чтения данных « O E ¯ » с возможностью, после его инвертирования, поступления в виде сигнала «Ч» на вход блока ключей шин разряда («БК ШР») и блока «ФТЗЧ», а в режиме записи выход « З Т 1 ¯ » «БУЗЧ» соединен с соответствующими входами «БУК ШЗС» и блока управления ключами шины разряда («БУК ШР») при выполнении условия З Т 1 ¯ = C E 1 ¯ ∨ W E ¯ выход «ЗТ2» «БУЗЧ» соединен с соответствующими входами «БУК ШЗС» и «БУК ШР» при выполнении условия З Т 2 ¯ = C E 2 ¯ ∨ W E ¯ , в режиме чтения выход « Ч Т 1 ¯ » «БУЗЧ» соединен с блоком усилителя чтения данных «БУЧ» при выполнении условия Ч Т 1 ¯ = C E 1 ¯ ∨ O E ¯ , выход « Ч Т 2 ¯ » «БУЗЧ» соединен с соответствующими входами «БУЧ» и блока ввода/вывода данных «БВВД» при выполнении условия Ч Т 2 ¯ = C E 2 ¯ ∨ O E ¯ (Фиг.16).

С целью генерации сигналов управления ключами «БУК ШЗС» в зависимости от состояния входных сигналов «C:i», где i=0…4095, « З Т 1 ¯ », « З Т 2 ¯ », выходы «a:i», «б:i» «БУК ШЗС» соединены с соответствующими входами «БК ШЗС» с возможностью обеспечения управлением состояния ключей: при уровне «1» сигналов « З Т 1 ¯ », « З Т 2 ¯ » выходы всех ключей «БК ШЗС» установлены в третье состояние (с выходным сопротивлением, близким к состоянию «холостого хода» (или «∞»)), т.е. концы «А» и «Б» всех шин «ШЗС» отсоединены от «БК ШЗС», при уровне сигнала «C:i», равном «1», и уровне «0» сигнала « З Т 2 ¯ », концы «А» и «Б» шины «ШЗС:i» подсоединены соответственно к источнику тока «IЗС» и общей шине («ШО») ключами «КА:i» и «КБ:i» с возможностью обеспечения записи «0» током « I З С 0 : i », при этом выходы остальных ключей установлены в третье состояние, при уровне сигнала «C:i», равном «0», и уровне «1» сигнала « З Т 2 ¯ », концы «А» и «Б» шины «ШЗС:i», где i=0…4095, присоединены соответственно к источнику тока «IЗС» и «ШО» ключами «КА:i» и «КБ:i» с возможностью обеспечения записи «1» током « I З С 1 : i »; при этом выходы «a:i», «б:i» «БУК ШЗС» соединены с входом «БК ШЗС» (Фиг.16).

С целью управления «БК ШР» выходы «б:0-15, Э» блока «БУК ШР» присоединены с одной стороны к «БК ШР» с логическим состоянием, определяемым состоянием входных сигналов внешнего устройства « D 3 : 0 − 15 ¯ », « З Т 1 ¯ », « З Т 2 ¯ », с другой стороны входы «Ч», «iч», «IЗР:0-15, Э» «БК ШР» соединены с соответствующими выходами «БУЗЧ» и «ФТЗЧ» с возможностью обеспечения: при уровне «1» сигналов « З Т 1 ¯ », « З Т 2 ¯ » установку выходов всех ключей «БК ШР» в третье состояние, т.е. концы «А» и «Б» разрядных шин «ШР» отсоединены от «БК ШР», при уровне «0» сигнала « З Т 1 ¯ » и высоком уровне сигналов « D 3 ¯ » (например, « D 3 : 1 ¯ », « D 3 : 5 ¯ », « D 3 : 10 ¯ ») концы «А» шин «ШР-А:1, 5, 10, Э» соответственно присоединены к источникам тока записи «IЗР:1, 5, 10, Э» ключами «КА:I, 5, 10, Э» и концы «Б» шин «ШР-Б:1, 5, 10, Э» присоединены к «ШО» ключами «КБ:1, 5, 10, Э» (запись «0» в разряды с кодом «0» в «DIO:i» выбранного слова i «МЗЯ» обеспечивается токами « I 0 з р : i , Э »), при этом выходы ключей, соединенных с шинами «ШР-Б:0, 2-4, 6-9, 11-15», установлены в третье состояние, при уровне «0» внешних сигналов « З Т 2 ¯ » и « D 3 ¯ : 0, 2 − 4, 6 − 9, 11 − 15 » (« D 3 ¯ : 1, 5, 10 » - имеют уровень «1») концы «А» шин «ШР-А:0, 2-4, 6-9, 11-15» присоединены к «ШО» и концы «Б» шин «ШР-Б:0, 2-4, 6-9, 1-15» соответственно присоединены к источникам тока « I 1 з р : 0, 2 − 4, 6 − 9, 11 − 15 » соответствующими ключами «БК ШР» (запись «1» в разряды с кодом «1» в «DIO:i» выбранного слова «C:i» «МЗЯ» обеспечивается токами « I 1 з р : i »), при этом выходы ключей, соединенных с шинами «ШР-А:1, 5, 10, Э», установлены в третье состояние с возможностью формирования на выходе «БК ШР» также сигналов чтения «UP:0-15, Э» и «UЭ», соединенных с соответствующими входами «БУЧ» (Фиг.16).

Для обеспечения соединения концов «ШЗС», выбранных для записи слова, к источнику тока «IЗС» и «ШО» в режиме записи и отключения шин «ШЗС», входы «a:i», «б:i» «БК ШЗС» соединены с соответствующими выходами «БУК ШЗС» с возможностью реализации алгоритма работы «БК ШЗС», а выходы «ШЗС-А:i» и «ШЗС-Б:i» (i=0…4095) «БК ШЗС» соединены с соответствующими шинами «МЗЯ» (Фиг.17).

Для формирования стабильных токов записи слова «IЗС» и разрядных токов записи «IЗР:0-15, Э», входы «З» и «Ч» блока «ФТЗЧ» соединены с соответствующими выходами «БУЗЧ», а выход «IЗС» «ФТЗЧ» при уровне «1» сигнала «З» соединен с входом «БК ШЗС», и « I З Р 1 : 0 − 15, Э » поступают на «БК ШР», а при уровне «1» сигнала «Ч» выход «iЧ:0-15, Э» блока «ФТЗЧ» соединен с соответствующим входом «БК ШР» (Фиг.16).

С целью частичной компенсации технологических отклонений сопротивлений «RH» и «RB» устройств «MTJ» в словах энергонезависимой «МЗЯ», она организована в виде 4096 шестнадцатиразрядных слов, каждая «ЗЯ» содержит «MTJ», транзистор МОП и систему шин для обеспечения записи и чтения данных по словам, а каждое слово содержит 17 «ЗЯ», одна из которых эталонная, исходно заранее установленная в состояние «0» с возможностью выработки эталонного напряжения «UЭ» при чтении информации из данного слова.

Для организации управления работой «МЗЯ» все шины записи/чтения «МЗЯ» соединены с соответствующими выходами «ШЗС-А:i», «ШЗС-Б:i» «БК ШЗС» (i=0…4095), шины «ШР-A:i, Э,», «ШР-Б:i, Э» (i=0-15) с соответствующими выходами «БК ШР», шина «ШЧС:i» с соответствующим выходом блока «Дш.А», а в режиме чтения шина «ШР-А:i, Э» соединена с входами «UP:0-15, Э» «БУЧ» и с выбранной «ЗЯ» (Фиг.18).

С целью обеспечения усиления считанных с шины «ШР-A:i, Э» «БК ШР» сигналов «UP:0-15, Э» и выработки нормированных сигналов «DЧ:0-15», в режиме чтения вход « Ч Т 1 ¯ » «БУЧ» соединен с соответствующим выходом «БУЗЧ» для подготовки «БУЧ» к чтению и вход « Ч Т 2 ¯ » соединен с уровнем «1» с соответствующим выходом «БУЗЧ» с возможностью формирования сигналов «DЧ:0-15» с уровнями «1» или «0» в соответствии с алгоритмом работы «БУЧ» при уровне «1» « Ч Т 2 ¯ » (Фиг.18).

Приведенное описание заявляемого устройства может быть дополнено следующими иллюстрациями, приведенными ниже.

На Фиг.1 показана процедура записи информации пропусканием тока, который намагничивает верхний свободный слой (СС) в прямом (параллельном) направлении: (1-1) - нижний фиксированный слой ФС; (1-2) - переход MTJ; (1-3) - СС; (1-4) - вектор намагниченности; (1-5) - элемент «MTJ».

На Фиг.2 показана процедура записи информации пропусканием тока, который намагничивает верхний СС в инверсном (антипараллельном) направлении: (2-1) - элемент «MTJ»; (2-1) - ФС; (2-2) - переход «MTJ»; (2-3) - СС; (2-4) - вектор намагниченности; (2-5) - элемент «MTJ».

На Фиг.3 приведена конструкция одноразрядной ячейки памяти (3-1) «PSV-MRAM», включающей в себя: элемент (3-2) «PSV», направление намагниченности (3-3) («1»∞→), («0»∞→) ФС, шину данных (3-4) («IS» «Sence») и шину записи/чтения (3-5) слов («Word»), ток записи/чтения (3-6) («IW/IR»), измерительный ток (3-7) IS.

На Фиг.4 показана ячейка памяти (4-1) «STT-MRAM», включающая в себя: элемент (4-2) «MTJ», транзистор МОП (4-3), шину разряда («ШР») (4-4), шину слов («ШС») (4-5), шину источника тока («ШИ») (4-6), усилитель считывания («УСч») (4-7), цепи записи/чтения (4-8), уровень отсчета (4-9) на «ШР», СС (4-10) элемента «MTJ».

На Фиг.5 показана организация шин записи/чтения матрицы «STT-MRAM»: а) поперечное сечение; б) вид сверху; (5-1) активная ячейка; (5-2) - шина записи/считывания (Word); (5-3) - линия данных (Sense); (5-4) - шина данных (Sense); (5-5) - ток измерительный IS; (5-6) - ток записи (IW)/считывания (IR); (5-7) - усилители считывания.

На Фиг.6 показана 3-D ячейка «MRAM» технического решения, принятого за прототип: (6-1) - ток записи; (6-2) - элемент «MTJ»; (6-3) - транзистор МОП; (6-4) - шина записи/разрядная (чтения); (6-5) - шина ввода данных.

На Фиг.7 показаны эпюры протекания токов записи/чтения в ячейке «STT-MRAM» для случая хранения а) логического «0» и б) логической «1»: (7-1) - IW - ток записи (word); (7-2) - RS - сопротивление шины данных (sense); (7-3) - US - напряжение на шине данных (sense); (7-4) - UD - напряжение на выходе данных.

На Фиг.8 показана структура ячейки памяти ИМС 1T1MTJ «MRAM»: (8-1) - шина записи/чтения (Word); (8-2) - шина данных (Sense); (8-3) - IS - ток чтения данных; (8-4) - «0»↔«1» - полярность тока записи/чтения; (8-5) - «0»∞←; →∞«1» - полярность вектора намагниченности.

На Фиг.9. показано поперечное сечение ячейки «STT-MRAM» со структурой «MTJ»: (9-1) - шина данных; (9-2) - СС; (9-3) туннельный барьер; (9-4) - ФС; (9-5) - шина разряда; (9-6) - изолирующий транзистор («ВКЛ» при чтении).

На Фиг.10 показана 3-D ячейка «STT-MRAM» конструкции Савченко: (10-1) - ячейка «MTJ»; (10-2) - шина разряда; (10-3) - магнитное поле; (10-4) шина слов; (10-5) - ток чтения; (10-6) - транзистор МОП («ВКЛ» при считывании, «ОТКЛ» при записи); (10-7) - компаратор; (10-8) - выходные данные; (10-9) - IREF - опорный источник.

На Фиг.11 показано поперечное сечение элемента «MTJ» с эффектом «пиннинга»: (11-1) - верхний электрод; (11-2) - составной магнитный слой; (11-3) - сенсорный слой; (11-4) - магнитный барьер; (11-5) - магнитный слой; (11-6) - эталонный слой; (11-7) - «Pinning»; (11-8) - базовый электрод.

На Фиг.12 показана временная диаграмма сигналов записи и соответствующие ей повороты магнитных осей в составном сенсорном слое ячейки «MRAM» («Freescale»): (12-1) - шина «1» записи; (12-2) - шина «2» записи; (12-3) ось трудного намагничивания; (12-4) - ось легкого намагничивания; (12-5) - расположение векторов поля H → и тока I → по линии «1»; (12-6) - расположение векторов поля H → и тока I → по линии «2».

На Фиг.13 показана эволюция архитектуры «MTJ», конструированная под «MRAM» (а) базисная структура «MTJ»; (b) структура «MTJ» с ферромагнитным слоем, запинингованным на антиферромагнетике;(с) структура «MTJ» с ферромагнитным слоем, запинингованным на искусственном антиферромагне