Устройство для моделирования процесса принятия решения в условиях неопределенности

Иллюстрации

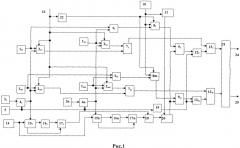

Показать всеИзобретение относится к автоматике и вычислительной технике. Техническим результатом является повышение точности при моделировании процесса принятия решения в условиях неопределенности. Устройство содержит матрицу m*n первых регистров lij (i=l,…,m, j=l,…,n), матрицу m*n первых блоков умножения 2ij (i=l,…,m, j=l,…,n), группу из n вторых 3j регистров, третий регистр 14, четвертый регистр 10, группу из m первых сумматоров 6i, группу из m вторых сумматоров 7i, группу из m третьих сумматоров 9i, группу из n четвертых сумматоров 15j, пятый сумматор 11, группу вторых блоков умножения 8i (i=l,…,m), третий блок умножения 20, шестой сумматор 18, группу из n первых элементов задержки 16j, группу из n элементов И 17j, второй элемент задержки 22, блок выбора максимального кода 21. 1 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является разработка устройства для моделирования процесса принятия решения в условиях неопределенности, обеспечивающего получение более точных вычислений.

Наиболее близким по технической сущности является устройство [1], содержащее вход 23, матрицу m*n первых регистров 1ij (i=l,…,m, j=l,…,n), матрицу m*n первых блоков умножения 2ij (i=l,…,m, j=l,…,n), группу из n вторых 3j регистров, третий регистр 14, четвертый регистр 10, группу из m первых сумматоров 6i; группу из m вторых сумматоров 7i, группу из m третьих сумматоров 9i, группу из n четвертых сумматоров 15j, пятый сумматор 11, группу вторых блоков умножения 8i (i=l,…,m), третий блок умножения 20, шестой сумматор 18, группу из n первых элементов задержки 16j, группу из n элементов И 17j, второй элемент задержки 22, блок выбора максимального кода 21, вход 23 подсоединен к входу второго элемента задержки 22 и к первым входам первых блоков умножения 2ij (i=l,…,m, j=l,…,n), второй вход каждого их которых подсоединен к выходу одноименного первого регистра 1ij, а выход - к одноименному входу второго сумматора 7i, входы первых сумматоров 6i подсоединены к выходам первых регистров 1ij, а выход - к первому входу второго блока умножения 8i (i=l,…,m), второй вход второго блока умножения 8i (i=l,…,m) подсоединен к выходу четвертого регистра 10, третий вход подсоединен к выходу второго элемента задержки 22, выход второго блока умножения 8i подсоединен к первому входу третьего сумматора 9i (i=l,…,m), выход третьего регистра 14 подсоединен к первым входам четвертых сумматоров 15j, первый выход которого через первый элемент задержки 16j подсоединен к первому входу группы элементов И 17j, второй вход которой подсоединен к второму выходу сумматора 15j, выход группы элементов И 17j подсоединен к одноименному входу шестого сумматора 18, выход которого подсоединен к первому входу третьего блока умножения 20, второй вход которого подсоединен к выходу пятого сумматора 11, вход которого подсоединен к выходу четвертого регистра 10, выход третьего блока умножения 20 подсоединен к второму входу третьего сумматора 9i (i=l,…,m).

Недостатком данного устройства является низкая точность из-за того, что не учитывался коэффициент α(0<=α<=1), отражающий соотношение субъективной ожидаемой полезности и риска при построении функции выбора [1].

Задача изобретения - создать устройство, обеспечивающее моделирование процесса принятия решения в условиях неопределенности с более высокой точностью.

Сущность изобретения состоит в том, что в устройство для моделирования процесса принятия решения, содержащее вход 23, матрицу m*n первых регистров 1ij(i=l,…,m, j=l,…,n), матрицу m*n первых блоков умножения 2ij (i=l,…,m, j=l,…,n), группу из n вторых 3i регистров, третий регистр 14, четвертый регистр 10, группу из m первых сумматоров 6i, группу из m вторых сумматоров 7i, группу из m третьих сумматоров 9i, группу из n четвертых сумматоров 15j, пятый сумматор 11, группу вторых блоков умножения 8i (i=l,…,m), третий блок умножения 20, шестой сумматор 18, группу из n первых элементов задержки 16j, группу из n элементов И 17j,второй элемент задержки 22, блок выбора максимального кода 21, вход 23 подсоединен к входу второго элемента задержки 22 и к первым входам первых блоков умножения 2ij (i=l,…,m, j=l,…,n), второй вход каждого их которых подсоединен к выходу одноименного первого регистра 1ij, а выход - к одноименному входу второго сумматора 7i, входы первых сумматоров 6i подсоединены к выходам первых регистров 1ij, а выход - к первому входу второго блока умножения 8i (i=l,…,m), второй вход второго блока умножения 8i (i=l,…,m) подсоединен к выходу четвертого регистра 10, третий вход подсоединен к выходу второго элемента задержки 22, выход второго блока умножения 8; подсоединен к первому входу третьего сумматора 9i (i=l,…,m), выход третьего регистра 14 подсоединен к первым входам четвертых сумматоров 15j, первый выход которого через первый элемент задержки 16j подсоединен к первому входу группы элементов И 17j, второй вход которой подсоединен к второму выходу сумматора 15j, выход группы элементов И 17j подсоединен к одноименному входу шестого сумматора 18, выход которого подсоединен к первому входу третьего блока умножения 20, второй вход которого подсоединен к выходу пятого сумматора 11, вход которого подсоединен к выходу четвертого регистра 10, выход третьего блока умножения 20 подсоединен к второму входу третьего сумматора 9i (i=l,…,m), в него введены пятый регистр 5, седьмой сумматор 19, группа восьмых сумматоров 13i (i=l,…,m), группа из четвертых блоков умножения 4j (j=l,…,n), группа из m пятых блоков умножения 12i (i=l,…,m), выход каждого из которых подсоединен к одноименным первым входам восьмых сумматоров 13i (i=l,…,m), вторые входы которых подсоединены к выходам одноименных вторых сумматоров 7i, а выход подсоединен к одноименному входу блока выбора максимального кода 21, выход пятого регистра 5 подсоединен к входу сумматора 19, выход которого подсоединен к первым входам пятых блоков умножения 12i (i=l,…,m), вторые входы которых подсоединены к выходам третьих сумматоров 9i, выход пятого регистра 5 подсоединен к первым входам четвертых блоков умножения 4j, вторые входы которых подсоединены к выходам вторых регистров 3j, а выход - к третьим входам первых блоков умножения 2ij и к второму входу четвертого сумматора 15i.

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от прототипа тем, что дополнительно в него введены пятый регистр 5, седьмой сумматор 19, группа восьмых сумматоров 13i (i=l,…,m), группа из четвертых блоков умножения 4j (j=l,…,n), группа из m пятых блоков умножения 12i (i=l,….,m), выход каждого из которых подсоединен к одноименным первым входам восьмых сумматоров 13i (i=l,…,m), вторые входы которых подсоединены к выходам одноименных вторых сумматоров 7i, а выход подсоединен к одноименному входу блока выбора максимального кода 21, выход пятого регистра 5 подсоединен к входу сумматора 19, выход которого подсоединен к первым входам пятых блоков умножения 12i (i=l,…,m), вторые входы которых подсоединены к выходам третьих сумматоров 9i, выход пятого регистра 5 подсоединен к первым входам четвертых блоков умножения 4j, вторые входы которых подсоединены к выходам вторых регистров 3j, а выход - к третьим входам первых блоков умножения 2ij и к второму входу четвертого сумматора 15i.

Изобретательский уровень достигается тем, что ввод соответствующих элементов в известный прототип вместе со связями позволяет решить новую техническую задачу, решение которой в известных технических решениях и в литературе в настоящее время не отражено.

Предлагаемое устройство позволяет быстро решить задачу моделирования процесса принятия решения в условиях неопределенности.

Сущность изобретения поясняется чертежом (фиг.1), на котором приведена структурная схема заявленного устройства.

Предполагается, что имеется m допустимых стратегий (управляющих воздействий A={ai} (i=l, 2…m) на систему). При этом вероятность наступления исхода Sj из множества возможных исходов S={sj}, (j=l, 2,…n) в результате применения стратегии ai (i=l, 2,…m) задается распределением вероятностей на множестве возможных исходов Psj/ai. Кроме того, каждому исходу Sj приписывается некоторая субъективная ценность исхода wj ∈ W, W={wj}, (j=l,2,…n).

Известен также некоторый уровень притязаний Qp, соответствующий наименьшему значению ожидаемой полезности, при котором исход события удовлетворяет лицо, принимающее решение (ЛПР). Известны также коэффициент β(0<=β<=1), характеризующий отношение ЛПР к риску, и коэффициент α (0<=α<=1), отражающий соотношение субъективной ожидаемой полезности и риска при построении функции выбора. Вводится в рассмотрение величина Qj=(Qp - α*wj) (j=l, 2,…n) для случая, при котором Qp>(α * wj), и Qj=0 для случая, при Qp=<(α *wj).

Устройство позволяет в результате анализа всех возможных вариантов выбрать наилучшую альтернативу αi ∈ A (i=l, 2,…m), для которой выполняется максимум целевой функции:

max ( ∑ j = 1 m ( α * P s j / a i * w j − ( 1 − α ) * ( β * P s j / a i + ( 1 − β ) * Q j ) ) ) ,

Устройство для решения задачи моделирования процесса принятия решения в условиях неопределенности показано на фиг.1. Устройство содержит: регистры lij (i=l, 2,…m, j=l, 2,…n), блоки умножения 2ij (i=l, 2,…m, j=l, 2,...n), регистры 3ij (j=l, 2,…n), блоки умножения 4j (j=l, 2,…n), регистр 5, сумматоры 6i (i=l, 2,…m), сумматоры 7i (i=l, 2,…m), блоки умножения 8i (i=l, 2,…m), сумматоры 9i (i=l, 2,…m), регистр 10, сумматор 11, блоки умножения 12i (i=l, 2,…m), сумматоры 13i (i=l, 2,…m), регистр 14, сумматоры 15j (j=l, 2,…n), элементы задержки 16j, группы элементов И 17j (j=l, 2,…n), сумматор 18, сумматор 19, блок умножения 20, схему выбора максимального кода 21, элементы задержки 22, вход 23, выходы 24 и 25.

Устройство работает следующим образом.

В исходном состоянии (см. рис.1) на регистрах 1ij (i=l, 2,…m, j=l, 2,…n) находятся коды значений Psj/ai, на регистрах 3j (j=l, 2,…n) коды значений wj (j=l, 2,…n), на регистре 5 - код значения α, на регистре 10 - код значения β, на регистре 14 - код значения Qp (установочные входы на регистрах 1, 3, 5, 10 и 14 на рис.1 не показаны).

После занесения исходных данных на регистры 3j (j=l, 2,…n) значений wj и на регистр 5 - код значения α, на выходах блоков умножения 4j (j=l, 2,…n) будут находиться результаты умножения содержимого регистрах 3j и содержимого регистра 5 - значения α * wj. На выходе сумматора 11 будет находиться значение (1-β), а на выходе сумматора 19 будет находиться значение (- (1- α)).

Работа устройства начинается после подачи пускового сигнала на его вход 23, после чего этот сигнал поступает на управляющие входы блоков умножения 2ij (i=l, 2,…m, j=l, 2,…n). На выходе каждого блока умножения 2ij появляется код значения (Psj/ai*а*wj), как результат умножения значения Psj/ai на регистре lij со значением α*wj. на регистре 4j. Коды с выходов блоков 2ij (i=l, 2,…m, j=l, 2,…n) поступают на одноименные входы сумматоров 7i (i=l, 2,…m). С выхода сумматора 7i значение суммы поступает на первый вход сумматора 13i (i=l, 2,…m).

Одновременно значение Psj/ai на регистре 1ij поступает на одноименный вход сумматора 6i (i=l, 2,…m), с выхода которого значение суммы поступает на первый вход блока умножения 8i.

Элемент задержки 22 обеспечивает задержку входного сигнала на суммарное время надежного срабатывания блока умножения 2ij и сумматора 7i. С появлением сигнала задержки на выходе элемента 22 в блоке умножения 8i происходит умножение значения коэффициента β с выхода регистра 10 на значение кода с выхода сумматора 6i (i=l, 2,…m).

Также одновременно значение Qp с выхода регистра 14 поступает на первые входы сумматоров 15j (j=l, 2,…n), на второй вход которого поступает код с выхода блока умножения 4j. На сумматоре 15j вычисляется значение (Qp-α*wj), которое поступает на вход группы элементов задержки 16j. Элемент 16j задерживает сигнал на время надежного срабатывания сумматора 15j. На втором выходе сумматора 15j (j=1, 2,…n) появляется единичный сигнал в случае, если значение (Qp - a*wj), (j=l, 2,…,n) будет положительным, и нулевой сигнал в случае, если значение (Qp - a*wj) будет нулевым или отрицательным. Сигнал со второго выхода сумматора 15j поступает на управляющий вход группы элементов И 17j, на второй вход которого поступает код с выхода элемента задержки 16j. Код с выхода элемента И 17j поступает на одноименный вход сумматора 18, с выхода которого код поступает на первый вход блока умножения 20.

Значение коэффициента β с выхода регистра 10 поступает также на вход сумматора 11, с выхода которого полученное значение (1-β) поступает на второй вход блока умножения 20, с выхода которого код поступает на вторые входы сумматоров 9i, выход каждого из которых подсоединен к первому входу блока умножения 12i (i=l, 2,…m), второй вход которого подсоединен к выходу сумматора 19. Код с выхода блока умножения 12i поступает на первый вход сумматора 13i, на второй вход которого поступает код с выхода сумматора 7i. На выходе сумматора 13i (i=l, 2,…m) появляется значение

( ∑ j = 1 m ( P s j / a i * α * w j − ( 1 − α ) * ( β * P s j / a i + ( 1 − β ) * Q j ) ) ) , и

вполученные коды с выходов сумматора 13i поступают на одноименные входы схемы выбора максимального кода 21.

На выходе 24 схемы выбора максимального кода 21 появляется значение максимального кода

max ( ∑ j = 1 m ( P s j / a i * α * w j − ( 1 − α ) * ( β * P s j / a i + ( 1 − β ) * Q j ) ) ) ,

а на выходе 25 появляется его порядковый номер i (i=l,…,m).

Схема выбора максимального кода широко известна и может быть выполнена так, как описано в [2].

Литература

1. Положительное решение от 2012.07.02 по заявке №2011125493. Дата подачи заявки: 22.06.2011.

2. Авторское свидетельство 1128249. Устройство для выделения экстремального кода. Опубликовано: 08.08.1984.

Устройство для моделирования процесса принятия решения, содержащее вход 23, матрицу m*n первых регистров 1ij (i=l,…,m,j=l,…,n), матрицу m*n первых блоков умножения 2ij (i=l,…,m, j=l,…,n), группу из n вторых 3j регистров, третий регистр 14, четвертый регистр 10, группу из m первых сумматоров 6i, группу из m вторых сумматоров 7i, группу из m третьих сумматоров 9i, группу из n четвертых сумматоров 15j, пятый сумматор 11, группу вторых блоков умножения 8i (i=1,…,m), третий блок умножения 20, шестой сумматор 18, группу из n первых элементов задержки 16j, группу из n элементов И 17j, второй элемент задержки 22, блок выбора максимального кода 21, вход 23 подсоединен к входу второго элемента задержки 22 и к первым входам первых блоков умножения 2ij (i=1,…,m, j=1,…n), второй вход каждого их которых подсоединен к выходу одноименного первого регистра 1ij, а выход - к одноименному входу второго сумматора 7i, входы первых сумматоров 6i подсоединены к выходам первых регистров 1ij, а выход - к первому входу второго блока умножения 8i (i=1,…,m), второй вход второго блока умножения 8i (i=1,…,m) подсоединен к выходу четвертого регистра 10, третий вход подсоединен к выходу второго элемента задержки 22, выход второго блока умножения 8i подсоединен к первому входу третьего сумматора 9i (i=1,…,m), выход третьего регистра 14 подсоединен к первым входам четвертых сумматоров 15j, первый выход которого через первый элемент задержки 16j подсоединен к первому входу группы элементов И 17j, второй вход которой подсоединен к второму выходу сумматора 15j, выход группы элементов И 17j подсоединен к одноименному входу шестого сумматора 18, выход которого подсоединен к первому входу третьего блока умножения 20, второй вход которого подсоединен к выходу пятого сумматора 11, вход которого подсоединен к выходу четвертого регистра 10, выход третьего блока умножения 20 подсоединен к второму входу третьего сумматора 9i (i=1,…,m), отличающееся тем, что в него введены пятый регистр 5, седьмой сумматор 19, группа восьмых сумматоров 13i (i=1,…,m), группа из четвертых блоков умножения 4j (j=1,…,n), группа из m пятых блоков умножения 12i (i=1,…,m), выход каждого из которых подсоединен к одноименным первым входам восьмых сумматоров 13i (i=1,…,m), вторые входы которых подсоединены к выходам одноименных вторых сумматоров 7i, а выход подсоединен к одноименному входу блока выбора максимального кода 21, выход пятого регистра 5 подсоединен к входу сумматора 19, выход которого подсоединен к первым входам пятых блоков умножения 12i (i=1,…,m), вторые входы которых подсоединены к выходам третьих сумматоров 9i, выход пятого регистра 5 подсоединен к первым входам четвертых блоков умножения 4j, вторые входы которых подсоединены к выходам вторых регистров 3j, а выход - к третьим входам первых блоков умножения 2ij и к второму входу четвертого сумматора 15i.