Цифровой измеритель частоты

Иллюстрации

Показать всеИзобретение относится к области измерительной техники и приборостроения, предназначено для измерения частоты следования импульсных сигналов. Цифровой измеритель частоты включает блок логический, блок реверсивного счета, блок логический формирования временного интервала измерения, блок определения временного интервала, счетчик периодов интервала измерения, автомат управления точностью измерения частоты, буфер количества импульсов, буфер начальной установки блока реверсивного счета, буфер временного интервала, буфер минимального временного интервала, буфер нормирующего коэффициента, буфер периода дискретизации, шинный интерфейс, генератор импульсов эталонной частоты. Технический результат заключается в расширении диапазона измерений частоты и снижении относительной погрешности измерений. 2 ил.

Реферат

Изобретение относится к области измерительной техники и приборостроения, предназначено для измерения частоты следования импульсных сигналов.

Из уровня техники известно устройство для измерения частоты, содержащее импульсный датчик, два счетчика, коммутатор, регистр памяти, генератор импульсов, дешифратор, элемент И и элемент ИЛИ, измеряющее частоту только на интервалах времени, кратных 2К посредством сдвига кода расстояния К раз (см. авт. св. СССР № 1053007, кл. G01P 3/489, 1983).

Недостатками устройства являются значительная приборная погрешность, обусловленная большой дискретностью измерения, и невозможность измерения на произвольных интервалах времени.

Из уровня техники известен цифровой измеритель частоты, содержащий генератор импульсов эталонной частоты, управляемый делитель частоты, первый двоичный счетчик, программируемую память и регистр памяти, причем установочный вход управляемого делителя частоты соединен со сбросовым входом первого двоичного счетчика и входом записи информации регистра памяти и является входом устройства, выход генератора импульсов эталонной частоты через управляемый делитель частоты включен на суммирующий вход первого двоичного счетчика, выходными разрядами, кроме старшего, соединенного с адресными разрядами программируемой памяти, а выходом переполнения - с управляющим входом управляемого делителя частоты, отличающийся тем, что в него введены второй двоичный счетчик, переключатель и триггер, причем вход устройства соединен с входами разрядов второго двоичного счетчика и сбросовым входом триггера, выходы разрядов программируемой памяти включены на входы разрядов регистра памяти, выход переполнения первого двоичного счетчика связан с информационным входом переключателя, управляющий вход которого соединен с выходом триггера, а первый и второй выходы - с вычитающим и суммирующим соответственно входами второго двоичного счетчика, выход обнуления которого включен на установочный вход триггера, а выходы разрядов второго двоичного счетчика и выход триггера заведены на входы разрядов регистра памяти (см. Патент РФ № 2118827, кл. G01R 23/02, 1998).

Недостатком цифрового измерителя частоты является низкая точность и невозможность применения измерителя в измерительных системах и комплексах, а также цифровых системах управления, работающих в реальном времени.

Технический результат заключается в расширении диапазона измерений частоты и снижении относительной погрешности измерений.

Технический результат достигается совокупностью существенных признаков, а именно: цифровой измеритель частоты содержит генератор импульсов эталонной частоты, блок логический, блок реверсивного счета, блок логический формирования временного интервала измерения, блок определения временного интервала, счетчик периодов интервала измерения, автомат управления точностью измерения частоты, буфер количества импульсов, буфер начальной установки блока реверсивного счета, буфер временного интервала, буфер минимального временного интервала, буфер нормирующего коэффициента, буфер периода дискретизации, шинный интерфейс, при этом блок логический имеет два входа для подключения источника дискретных импульсных сигналов, первый выход блока логического соединен с первым входом блока реверсивного счета, второй выход блока логического соединен с первым входом автомата управления точностью измерения частоты, третий выход блока логического соединен с входом блока логического формирования временного интервала, выход которого соединен с входом счетчика периодов интервала измерения, вход-выход которого соединен с третьим входом-выходом автомата управления точностью измерения частоты, первый и второй входы-выходы которого соединены с входами-выходами блока определения временного интервала и блока логического формирования временного интервала измерения соответственно, выход генератора импульсов эталонной частоты соединен с входом блока определения временного интервала, выход блока реверсивного счета соединен с входом буфера количества импульсов, выход которого соединен с первым входом шинного интерфейса, первый выход которого соединен с входом буфера начальной установки блока реверсивного счета, выход которого соединен с вторым входом блока реверсивного счета, первый и второй выходы автомата управления точностью измерения частоты соединены с входами буфера временного интервала и буфера нормирующего коэффициента соответственно, выходы которых соответственно соединены с вторым и третьим входами шинного интерфейса, второй и третий выходы которого соответственно соединены с входами буфера минимального временного интервала и буфера периода дискретизации, выходы которых соответственно соединены с вторым и третьим входами автомата управления точностью измерения частоты, при этом автомат управления точностью измерения частоты выполнен с функцией минимизации относительной погрешности измерения, на схеме сравнения и регистре сдвига, и дополнительно содержит таймер, выполненный с возможностью прекращения цикла измерения при пропадании или резком понижении частоты следования входного сигнала.

Признаки и сущность заявленного изобретения поясняются в последующем детальном описании, иллюстрируемом чертежами, где показано следующее:

На фиг.1 - Структурная схема заявленного цифрового измерителя частоты, где:

1 - источник дискретных импульсных сигналов или инкрементный/ импульсный датчик;

2 - блок логический;

3 - блок реверсивного счета;

4 - блок логический формирования временного интервала измерения;

5 - блок определения временного интервала;

6 - счетчик периодов интервала измерения;

7 - автомат управления точностью измерения частоты;

8 - буфер количества импульсов;

9 - буфер начальной установки блока реверсивного счета;

10 - буфер временного интервала;

11 - буфер минимального временного интервала;

12 - буфер нормирующего коэффициента;

13 - буфер периода дискретизации;

14 - шинный интерфейс;

15 - генератор импульсов эталонной частоты;

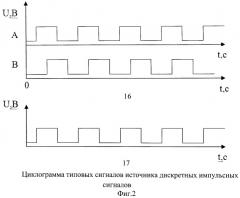

На фиг.2 - Циклограмма типовых сигналов источника дискретных импульсных сигналов, где:

16 - типовые формы выходных сигналов инкрементных импульсных датчиков;

17 - типовая форма дискретных импульсных сигналов.

Принцип действия устройства основан на подсчете целого количества периодов входных импульсов за назначенный измерительный временной интервал и отнесении его к количеству периодов импульсов эталонной частоты за тот же интервал.

Устройство работает следующим образом. Входной сигнал (см. фиг.1) поступает на вход блока логического 2 из источника дискретных импульсных сигналов 1, блок логический производит логическую обработку входных сигналов и его коммутацию. В частности для сигналов 16 (см. фиг.2) производится извлечение угловых импульсов и направления движения, при этом частота следования угловых импульсов будет в 2 раза выше чем у канала А или В, количество импульсов на выходе схемы увеличится в 4 раза. Направление движения определяется по фазовым соотношениям каналов А и В. Входной сигнал 17 проходит на выход блока логического без изменения по выходу коммутируемому с угловыми импульсами. Выход блока логического 2 соединен с входами блока реверсивного счета 3 и блока логического формирования временного интервала измерения 4. Блок реверсивного счета 3 производит подсчет угловых импульсов. Направление счета задается сигналом направления движения блока логического 2. Данные, накопленные в блоке реверсивного счета 3, поступают в буфер количества импульсов 8, где хранятся до прихода новых данных. Начальные значения для установки блока реверсивного счета 3 через шинный интерфейс 14 поступают в буфер начальной установки блока реверсивного счета 9 и с его выхода поступают на вход блока реверсивного счета 3. Начальная установка производится по служебным сигналам, поступающим от источника дискретных импульсных сигналов 1. Блок логический формирования временного интервала измерения 4 производит формирование логического сигнала определяющего временной интервал измерения из целого количества угловых импульсов, полученных из блока логического 2, при этом подсчет угловых импульсов производится счетчиком периодов интервала измерения 6. Для оптимизации относительной погрешности блок логический формирования временного интервала измерения 4 имеет связь с автоматом управления точностью измерения частоты 7. Автомат управления точностью измерения частоты 7 рассчитывает желаемое количество периодов входного сигнала, составляющее временной интервал измерения и обеспечивающее оптимизацию. Автомат управления точностью измерения частоты 7 формирует сигнал разрешения начала измерения; блок логический формирования временного интервала измерения 4 на основе сигнала разрешения измерения и переднего фронта углового импульса переводит в активный уровень сигнал, определяющий временной интервал измерения; на основе сигнала разрешения начала измерения счетчик периодов интервала измерения 6 переходит в начальное состояние; по переднему фронту углового импульса и наличию активного уровня сигнала определяющего временной интервал измерения производится инкремент содержимого счетчика периодов интервала измерения; текущее состояние счетчика периодов интервала измерения сравнивается с желаемым количеством периодов входного сигнала в автомате управления точностью измерения частоты 7 и при их совпадении формируется сигнал окончания измерения; блок логический формирования временного интервала измерения 4 на основе сигнала окончания измерения и заднего фронта углового импульса переводит в неактивный уровень сигнал, определяющий временной интервал измерения, при этом измерение прекращается, автомат управления точностью измерения частоты 7 производит перерасчет желаемого количества периодов входного сигнала и цикл измерения повторяется.

Автомат управления точностью измерения частоты 7 снабжен таймером, перезапускаемым передним или задним фронтом углового импульса, предназначенным для обнаружения пропадания движения временного интервала отмеряемого таймером. По сигналу таймера происходит окончание измерения и обнуляется измеряемая частота/скорость. Блок определения временного интервала 5 производит прямой подсчет синхроимпульсов генератора импульсов эталонной частоты 15 за временной интервал измерения с последующим запоминанием результата. Результат поступает в автомат управления точностью измерения частоты 7, где производится оценка полученного результата в соответствии с выбранным параметром оптимизации. Результаты измерения частоты проступают в буфер временного интервала 10 и буфер нормирующего коэффициента 12, где сохраняются до появления данных новых измерений.

Параметры оптимизации задаются через шинный интерфейс 14 и хранятся в буфере минимального временного интервала 11 и буфере периода дискретизации 13. Шинный интерфейс 14 содержит арифметический делитель плавающей точки одинарной/двойной точности, предназначенный для перерасчета значения периода следования импульсов. Период представляется дробью, составленной из значений, заносимых в буфер нормирующего коэффициента в качестве числителя, и значений буфера временного интервала в качестве знаменателя. В результате значения периода из формата правильной дроби переводится в формат плавающей точки одинарной/ двойной точности и производится расчет частоты следования импульсов как величины обратной периоду.

Частота следования импульсов (скорость движения) на выходе устройства определяется по следующим формулам:

f и з м = P N ⋅ 1 T 0 ; ( 1 )

ω и з м = P N ⋅ Δ ϕ T 0 ; ( 2 )

где:

fизм - измеренная частота;

ωизм - измеренная скорость;

Р - числовой код, характеризующий количество периодов входного сигнала за временной интервал измерения;

N - числовой код, характеризующий количество периодов тактовой частоты T0 за временной интервал измерения;

Т0 - период тактовой частоты, в секундах,

Δφ - линейное разрешение датчика положения - источника сигнала, в единицах измерения линейных или угловых перемещений.

При этом численные значения временных параметров, заносимые в буферы устройства и считываемые из них, определяются по формуле:

N = T T 0 ; ( 3 )

где:

N - числовой код, характеризующий количество периодов тактовой частоты за временной интервал Т,

T0 - период тактовой частоты в секундах,

Т - временной интервал или параметр в секундах.

Количество периодов входного сигнала определяется автоматом управления точностью измерения скорости. Автомат производит расчет входного сигнала по двум алгоритмам.

В первом случае для работы автомата задается либо минимальный

временной интервал (максимальная относительная погрешность) или период дискретизации, связанные между собой соотношениями

T д и с к р = 4 ⋅ Т min ; ( 4 )

C д и с к р = 4 ⋅ C min ; ( 5 )

где:

Тдискр, Сдискр - период дискретизации в секундах и его числовой код, полученный подстановкой (3) в (4),

Tmin, Cmin - минимальный временной интервал и его числовой код, полученный аналогично.

Далее автомат производит расчет граничных коэффициентов, необходимых для работы

C в е р х = 3 ⋅ С min ; ( 6 )

С н и ж н = С min ; ( 7 )

где:

Cверх - числовой код, характеризующий максимальное количество периодов тактовой частоты за временной интервал измерения, не вызывающий перерасчет параметров оптимизации,

Снижн - числовой код, характеризующий минимальное количество периодов тактовой частоты за временной интервал измерения.

Числовой код, характеризующий количество периодов входного сигнала, связан соотношением (8):

P = 2 K ; ( 8 )

где:

К - итерационный коэффициент, в первый момент равный 0, К - может принимать значения 0, 1, 2…n, где n - количество разрядов в коде Р. Алгоритм оптимизации описывается выражением

P i + 1 = { P i / 2, п р и N i > C в е р х н P i , п р и C н и ж н < N i < C в е р х н 2 ⋅ P i , п р и N i < C н и ж н , или с учетом (8)

P i + 1 = { 2 K i − 1 , п р и N i > C в е р х н и K i > 0 ; 2 K i , п р и C н и ж н < N i < C в е р х н ; 2 K i + 1 , п р и N i < C н и ж н и K i < n ; ( 9 )

где:

нижний индекс i - означает, что код получен на i-том шаге итерации, индекс i+1 - означает, что код будет использован на следующем шаге итерации.

В случае отсутствия угловых импульсов в течение периода дискретизации, сторожевой таймер автомата уменьшает заданное количество угловых импульсов в 2 раза.

Pi+1=Pi/2 или

P i + 1 = 2 K − 1 , ( 10 )

Во втором случае задается только нижний предел временного интервала, при этом автомат подсчитывает количество угловых импульсов, и в случае, если временной интервал становится больше нижнего предела, автомат выдает результат по пришествии следующего углового импульса.

Таким образом, использование заявленного устройства позволяет обеспечить решение поставленной задачи с достижением неожиданного технического результата.

Заявленное устройство было применено в системе управления модуля на основе микроприводов, в качестве схемы вторичной обработки полупроводникового преобразователя неэлектрической величины в электрическую с частотным выходом. Устройство позволило получить относительную погрешность измерения частоты 0,003% в диапазоне частот от 200 Гц до 20 МГц при частоте тактового сигнала 40 МГц, измерение производилась при оптимизации по периоду дискретизации, назначенному 0,005 с (200 Гц). Таким образом, заявленное устройство позволяет производить измерения в широком диапазоне частот, с повышенной точностью на коротком временном интервале измерения.

Цифровой измеритель частоты, содержащий: генератор импульсов эталонной частоты, блок логический, блок реверсивного счета, блок логический формирования временного интервала измерения, блок определения временного интервала, счетчик периодов интервала измерения, автомат управления точностью измерения частоты, буфер количества импульсов, буфер начальной установки блока реверсивного счета, буфер временного интервала, буфер минимального временного интервала, буфер нормирующего коэффициента, буфер периода дискретизации, шинный интерфейс, при этом блок логический имеет два входа для подключения источника дискретных импульсных сигналов, первый выход блока логического соединен с первым входом блока реверсивного счета, второй выход блока логического соединен с первым входом автомата управления точностью измерения частоты, третий выход блока логического соединен с входом блока логического формирования временного интервала, выход которого соединен с входом счетчика периодов интервала измерения, вход-выход которого соединен с третьим входом-выходом автомата управления точностью измерения частоты, первый и второй входы-выходы которого соединены с входами-выходами блока определения временного интервала и блока логического формирования временного интервала измерения соответственно, выход генератора импульсов эталонной частоты соединен с входом блока определения временного интервала, выход блока реверсивного счета соединен с входом буфера количества импульсов, выход которого соединен с первым входом шинного интерфейса, первый выход которого соединен с входом буфера начальной установки блока реверсивного счета, выход которого соединен с вторым входом блока реверсивного счета, первый и второй выходы автомата управления точностью измерения частоты соединены с входами буфера временного интервала и буфера нормирующего коэффициента соответственно, выходы которых соответственно соединены с вторым и третьим входами шинного интерфейса, второй и третий выходы которого соответственно соединены с входами буфера минимального временного интервала и буфера периода дискретизации, выходы которых соответственно соединены с вторым и третьим входами автомата управления точностью измерения частоты, при этом автомат управления точностью измерения частоты выполнен с функцией минимизации относительной погрешности измерения и выполнен на схеме сравнения и регистре сдвига и дополнительно содержит таймер, выполненный с возможностью прекращения цикла измерения при пропадании или резком понижении частоты следования входного сигнала.