Ранговый фильтр

Иллюстрации

Показать всеИзобретение относится к автоматике и аналоговой вычислительное технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом является повышение быстродействия рангового фильтра. Ранговый фильтр содержит девять реляторов, каждый из которых содержит компаратор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, замыкающий и размыкающий ключи. 2 ил., 1 табл.

Реферат

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны ранговые фильтры (см., например, фиг.1 в описании изобретения к патенту РФ 2192045, кл. G06G 7/52, 2002 г.), которые содержат реляторы и с помощью двух управляющих сигналов реализуют выбор минимального, супраминимального, субмаксимального или максимального из четырех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных ранговых фильтров, относится низкое быстродействие, обусловленное тем, что максимальное время задержки распространения сигнала в них определяется выражением τ≥4τp, где τp есть время задержки релятора.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип ранговый фильтр (фиг.1 в описании изобретения к патенту РФ 2284652, кл. G06G 7/52, 2006 г.), который содержит реляторы и с помощью двух управляющих сигналов реализует выбор минимального, супраминимального, субмаксимального или максимального из четырех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится низкое быстродействие, обусловленное тем, что максимальное время задержки распространения сигнала в прототипе определяется выражением τ=3τp, где τp есть время задержки релятора.

Техническим результатом изобретения является повышение быстродействия при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в ранговом фильтре, содержащем семь реляторов, каждый из которых содержит компаратор, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первый и второй входы которого соединены соответственно с неинвертирующим и инвертирующим входами компаратора, особенность заключается в том, что в него дополнительно введены два аналогичных упомянутым релятора, в каждом из девяти реляторов третий и четвертый входы соединены соответственно с входами замыкающего и размыкающего ключей, первый и второй информационные входы рангового фильтра соединены соответственно с объединенными первым, четвертым входами второго, первым, третьим входами четвертого реляторов и объединенными вторым, третьим входами второго, вторым, четвертым входами четвертого реляторов, третий и четвертый информационные входы рангового фильтра подключены соответственно к объединенным первому, третьему входам первого, первому, четвертому входам третьего реляторов и объединенным второму, четвертому входам первого, второму, третьему входам третьего реляторов, выходы первого и второго реляторов соединены соответственно с объединенными первым, третьим входами шестого, вторым, третьим входами седьмого, вторым входом восьмого реляторов и объединенными первым, третьим входами пятого, первыми входами седьмого, восьмого реляторов, выходы третьего и четвертого реляторов подключены соответственно к объединенным второму, четвертому входам пятого, второму входу девятого реляторов и объединенным второму, четвертому входам шестого, четвертому входу восьмого, первому входу девятого реляторов, а выходы пятого, шестого, седьмого, восьмого и девятого реляторов соединены соответственно с четвертым входом седьмого, третьим входом восьмого, третьим, четвертым входами девятого реляторов и выходом рангового фильтра, первый и второй управляющие входы которого подключены соответственно к объединенным входам управления третьего, девятого реляторов и объединенным входам управления остальных реляторов.

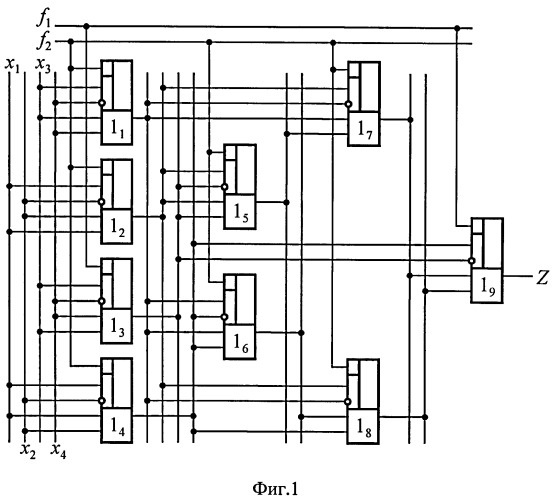

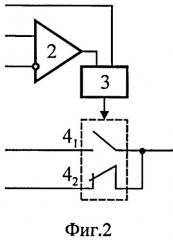

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого рангового фильтра и схема релятора, использованного при построении указанного фильтра.

Ранговый фильтр содержит реляторы 11, …, 19. Каждый релятор содержит компаратор 2, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей 41 и 42, входы которых являются соответственно третьим и четвертым входами релятора, первый, второй входы и выход которого образованы соответственно неинвертирующим, инвертирующим входами компаратора 2 и объединенными выходами ключей 41, 42. Первый и второй информационные входы рангового фильтра соединены соответственно с объединенными первым, четвертым входами релятора 12, первым, третьим входами релятора 14 и объединенными вторым, третьим входами релятора 12, вторым, четвертым входами релятора 14, третий и четвертый информационные входы рангового фильтра подключены соответственно к объединенным первому, третьему входам релятора 11, первому, четвертому входам релятора 13 и объединенным второму, четвертому входам релятора 11, второму, третьему входам релятора 13, выходы реляторов 11 и 12 соединены соответственно с объединенными первым, третьим входами релятора 16, вторым, третьим входами релятора 17, вторым входом релятора 18 и объединенными первым, третьим входами релятора 15, первыми входами реляторов 17, 18, выходы реляторов 13 и 14 подключены соответственно к объединенным второму, четвертому входам релятора 15, второму входу релятора 19 и объединенным второму, четвертому входам релятора 16, четвертому входу релятора 18, первому входу релятора 19, а выходы реляторов 15, 16, 17, 18 и 19 соединены соответственно с четвертым входом релятора 17, третьим входом релятора 18, третьим, четвертым входами релятора 19 и выходом рангового фильтра, первый и второй управляющие входы которого подключены соответственно к объединенным входам управления реляторов 13, 19 и объединенным входам управления остальных реляторов.

Работа предлагаемого рангового фильтра осуществляется следующим образом. На его первый, …, четвертый информационные входы подаются соответственно подлежащие обработке аналоговые сигналы (напряжения) x1, …, x4; на его первом и втором управляющих входах фиксируются соответственно необходимые управляющие сигналы f1 и f2, f1, f2∈{0,1}. Если на входе управления релятора присутствует логический «0» (логическая «1») и сигнал на его первом входе больше либо меньше сигнала на его втором входе, то ключ 41 соответственно замкнут (разомкнут) либо разомкнут (замкнут), а ключ 42 соответственно разомкнут (замкнут) либо замкнут (разомкнут). Таким образом, сигнал Z на выходе предлагаемого рангового фильтра при всех возможных вариантах упорядочения сигналов х1, …, x4 и всех возможных комбинациях значений сигналов f1, f2 будет принимать значения, указанные в представленной ниже таблице.

| Варианты упорядочения | Z | |||

| f1=1, f2=0 | f1=0, f2=1 | f1=f2=1 | f1=f2=0 | |

| x1<x2<x3<x4 | x4 | x1 | x3 | x2 |

| x1<x2<x4<x3 | x3 | x1 | x4 | x2 |

| x1<x3<x2<x4 | x4 | x1 | x2 | x3 |

| x1<x4<x2<x3 | x3 | x1 | x2 | x4 |

| x1<x3<x4<x2 | x2 | x1 | x4 | x3 |

| x1<x4<x3<x2 | x2 | x1 | x3 | x4 |

| x3<x1<x2<x4 | x4 | x3 | x2 | x1 |

| x4<x1<x2<x3 | x3 | x4 | x2 | x1 |

| x3<x1<x4<x2 | x2 | x3 | x4 | x1 |

| x4<x1<x3<x2 | x2 | x4 | x3 | x1 |

| x2<x1<x3<x4 | x4 | x2 | x3 | x1 |

| x2<x1<x4<x3 | x3 | x2 | x4 | x1 |

| x2<x3<x1<x4 | x4 | x2 | x1 | x3 |

| x2<x4<x1<x3 | x3 | x2 | x1 | x4 |

| x3<x2<x1<x4 | x4 | x3 | x1 | x2 |

| x4<x2<x1<x3 | x3 | x4 | x1 | x2 |

| x3<x4<x1<x2 | x2 | x3 | x1 | x4 |

| x4<x3<x1<x2 | x2 | x4 | x1 | x3 |

| x2<x3<x4<x1 | x1 | x2 | х4 | x3 |

| x2<x4<x3<x1 | x1 | x2 | x3 | x4 |

| x3<x2<x4<x1 | x1 | x2 | х4 | x2 |

| x4<x2<x3<x1 | x1 | x4 | х3 | x2 |

| x3<x4<x2<x1 | x1 | x3 | x2 | x4 |

| x4<x3<x2<x1 | x1 | x4 | х2 | x3 |

С учетом данных, приведенных в таблице, имеем

Z = { min ( x 1 , … , x 4 ) п р и f 1 = 0, f 2 = 1 sup r a min ( x 1 , … , x 4 ) п р и f 1 = f 2 = 0 s u b max ( x 1 , … , x 4 ) п р и f 1 = f 2 = 1 max ( x 1 , … , x 4 ) п р и f 1 = 1, f 2 = 0

Поскольку время задержки релятора определяется выражением τp=τк+τИСК.ИЛИ+τкл, где τк, τИСК.ИЛИ и τкл есть соответственно время срабатывания компаратора, время срабатывания элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и время замыкания (размыкания) ключей, то максимальное время задержки распространения сигнала в предлагаемом ранговом фильтре равно 2 τp.

Вышеизложенные сведения позволяют сделать вывод, что ранговый фильтр (фиг.1) с помощью двух управляющих сигналов реализует выбор минимального, супраминимального, субмаксимального или максимального из четырех входных аналоговых сигналов и обладает более высоким по сравнению с прототипом быстродействием.

Ранговый фильтр, содержащий семь реляторов, каждый из которых содержит компаратор, подключенный выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первый и второй входы которого соединены соответственно с неинвертирующим и инвертирующим входами компаратора, отличающийся тем, что в него дополнительно введены два аналогичных упомянутым релятора, в каждом из девяти реляторов третий и четвертый входы соединены соответственно с входами замыкающего и размыкающего ключей, первый и второй информационные входы рангового фильтра соединены соответственно с объединенными первым, четвертым входами второго, первым, третьим входами четвертого реляторов и объединенными вторым, третьим входами второго, вторым, четвертым входами четвертого реляторов, третий и четвертый информационные входы рангового фильтра подключены соответственно к объединенным первому, третьему входам первого, первому, четвертому входам третьего реляторов и объединенным второму, четвертому входам первого, второму, третьему входам третьего реляторов, выходы первого и второго реляторов соединены соответственно с объединенными первым, третьим входами шестого, вторым, третьим входами седьмого, вторым входом восьмого реляторов и объединенными первым, третьим входами пятого, первыми входами седьмого, восьмого реляторов, выходы третьего и четвертого реляторов подключены соответственно к объединенным второму, четвертому входам пятого, второму входу девятого реляторов и объединенным второму, четвертому входам шестого, четвертому входу восьмого, первому входу девятого реляторов, а выходы пятого, шестого, седьмого, восьмого и девятого реляторов соединены соответственно с четвертым входом седьмого, третьим входом восьмого, третьим, четвертым входами девятого реляторов и выходом рангового фильтра, первый и второй управляющие входы которого подключены соответственно к объединенным входам управления третьего, девятого реляторов и объединенным входам управления остальных реляторов.