Составной транзистор

Иллюстрации

Показать всеИзобретение относится к составному транзистору, который может быть использован в качестве устройства усиления аналоговых сигналов и в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в повышении в 8÷10 раз верхней граничной частоты различных усилителей за счет уменьшение входной и выходной емкостей используемого в них составного транзистора. Составной транзистор содержит входной транзистор (1), база которого является базой (2), а эмиттер - эмиттером (3) составного транзистора, выходной транзистор (4), коллектор которого является коллектором (5) составного транзистора, а эмиттер соединен с коллектором входного транзистора (1), при этом в схему введен дополнительный транзистор (6), статический режим которого по току эмиттера устанавливается дополнительным источником опорного тока (7), включенным между первой (8) шиной источника питания и эмиттером дополнительного транзистора (6), причем база дополнительного транзистора (6) соединена с базой входного транзистора (1), его коллектор связан с эмиттером входного транзистора (1), а эмиттер подключен к базе выходного транзистора (4). 1 з.п. ф-лы, 10 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных и избирательных усилителях ВЧ и СВЧ диапазонов).

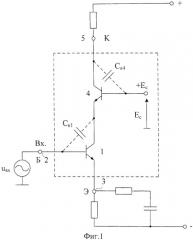

В современной микроэлектронике находят широкое применение классические каскодные усилители (КУ) с резистивной нагрузкой (фиг.1), включенной в коллекторную цепь входного транзистора - каскада с общим эмиттером [1-15]. Активную часть КУ, содержащую входной 1 и выходной 4 транзисторы, можно рассматривать как составной транзистор (СТ), который может включаться в различные электронные схемы.

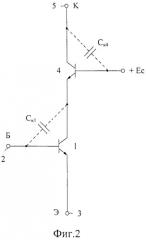

Наиболее близким по технической сущности к заявляемому устройству является составной транзистор в схеме КУ (фиг.1) по патенту US 5.304.946, fig. 14, который показан также на чертеже фиг.2. Он содержит входной транзистор 1, база которого является базой 2, а эмиттер - эмиттером 3 составного транзистора, выходной транзистор 4, коллектор которого является коллектором 5 составного транзистора.

Существенный недостаток известного СТ, архитектура которого присутствует также во многих других каскодных усилителях [1-15], состоит в том, что он обладает сравнительно большими выходной Свых и входной Свх паразитными емкостями, что отрицательно сказывается на диапазоне его рабочих частот в структуре различных усилителей.

Основная задача предполагаемого изобретения состоит в уменьшении входной и выходной емкостей составного транзистора и, как следствие, повышение в 8-10 раз верхней граничной частоты различных усилителей на базе заявляемого СТ.

Поставленная задача решается тем, что в составном транзисторе фиг.1, содержащем входной транзистор 1, база которого является базой 2, а эмиттер - эмиттером 3 составного транзистора, выходной транзистор 4, коллектор которого является коллектором 5 составного транзистора, а эмиттер соединен с коллектором входного транзистора 1, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 6, статический режим которого по току эмиттера устанавливается дополнительным источником опорного тока 7, включенным между первой 8 шиной источника питания и эмиттером дополнительного транзистора 6, причем база дополнительного транзистора 6 соединена с базой входного транзистора 1, его коллектор связан с эмиттером входного транзистора 1, а эмиттер подключен к базе выходного транзистора 4.

Схема каскодного усилителя на основе составного транзистора-прототипа показана на чертеже фиг.1. На чертеже фиг.2 представлена отдельно схема СТ-прототипа.

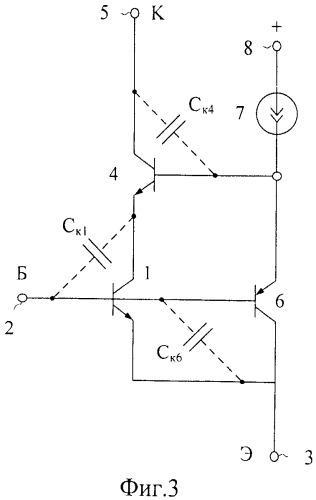

На чертеже фиг.3 показан заявляемый СТ в соответствии с п.1 формулы изобретения.

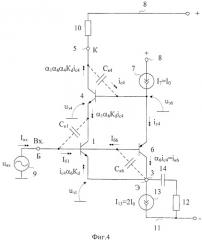

На чертеже фиг.4 представлена схема каскодного усилителя на основе СТ фиг.3, соответствующая п.2 формулы изобретения.

На чертеже фиг.5 представлена схема каскодного усилителя на базе СТ-прототипа фиг.2 (напряжение питания Еп=±5 В, транзисторы TN50S ФГУП НПП «Пульсар»).

На чертеже фиг.6 приведена схема каскодного усилителя на базе предлагаемого СТ фиг.3 (Еп=±5 В, транзисторы TN50S, TP50S ФГУП НПП «Пульсар»).

На чертеже фиг.7 показана зависимость коэффициента усиления по напряжению от частоты для схемы каскодного усилителя на базе СТ-прототипа фиг.5 и КУ с предлагаемым СТ фиг.3 (транзисторы TN50S, TP50S ФГУП НПП «Пульсар). Данный график показывает, что заявляемое устройство имеет в 7-8 раз лучшее значение верхней граничной частоты fB.

На чертеже фиг.8 представлена зависимость комплексного входного сопротивления от частоты для схем каскодного усилителя на базе СТ-прототипа фиг.2 и усилителя с предлагаемым СТ фиг.3 (транзисторы TN50S, ТР508 ФГУП НПП «Пульсар). Данный график показывает, что входная емкость предлагаемого устройства в 3-4 раза меньше, чем в известном СТ.

На чертеже фиг.9 показана схема каскодного усилителя на основе заявляемого СТ, которая имеет близкий к нулю входной статический ток.

На чертеже фиг.10 приведена зависимость входного статического тока сравниваемых схем фиг.5 и фиг.9 от температуры.

Данные графики показывают, что предлагаемая схема имеет значительно меньший входной статический ток, что приближает ее свойства по этому параметру к полевым транзисторам.

Составной транзистор фиг.3 содержит входной транзистор 1, база которого является базой 2, а эмиттер - эмиттером 3 составного транзистора, выходной транзистор 4, коллектор которого является коллектором 5 составного транзистора, а эмиттер соединен с коллектором входного транзистора 1. В схему введен дополнительный транзистор 6, статический режим которого по току эмиттера устанавливается дополнительным источником опорного тока 7, включенным между первой 8 шиной источника питания и эмиттером дополнительного транзистора 6, причем база дополнительного транзистора 6 соединена с базой входного транзистора 1, его коллектор связан с эмиттером входного транзистора 1, а эмиттер подключен к базе выходного транзистора 4.

На чертеже фиг.4, в соответствии с п.2 формулы изобретения, база входного транзистора 1 соединена с источником входного напряжения 9, между первой 8 шиной источника питания и коллектором выходного транзистора 4 включен резистор коллекторной нагрузки 10, а эмиттер входного транзистора 1 соединен по переменному току со второй 11 шиной источника питания через резистор местной обратной связи 12, а также соединен со второй 11 шиной источника питания через токостабилизирующий двухполюсник 13. Конденсатор 14 выполняет классическую роль разделительной емкости.

Рассмотрим работу ДУ фиг.3 в схеме фиг.4.

Приращение напряжения на коллекторе «К» (узел 5) составного транзистора в схеме фиг.4 вызывает изменение тока ic4 через емкость коллектор-база Ск4 выходного транзистора 4. Данный ток поступает в эмиттер, а затем в коллектор транзистора 6:

i к 6 = α 6 i c 4 , ( 1 )

где αi≈1 - коэффициент усиления по току эмиттера i-гo транзистора.

В эмиттерной цепи транзистора 1 при сопротивлении конденсатора 14 значительно меньшем, чем R12, происходит перераспределение тока α6ic4 между эмиттером транзистора 1 и резистором местной обратной связи 12:

i э l = R 12 R 12 + r э l i к 6 = α 6 К d i c 4 , ( 2 )

где K d = R 12 R 12 + r э l - коэффициент деления тока iк6 между rэl и R12;

rэl≈20÷30 Ом - сопротивление эмиттерного р-n перехода транзистора 1.

Таким образом, коллекторный ток транзистора 4 и, следовательно, суммарный ток коллектора составного транзистора

iк4=α6α1α4Kdic4, (3)

iкΣ=ic4-iк4=ic4(1-α6α1α4Kd). (4)

Из (4) следует, что эффективная выходная емкость предлагаемого СТ уменьшается

Cэф.к4=(1-α6α1α4Kd)=Cк4(1-Ti), (5)

где Ti=α6α1α4Kd≈1.

Как следствие, уменьшается эквивалентная постоянная времени коллекторной цепи нагрузки СТ (τэкв) и увеличивается верхняя граничная частота КУ фиг.4 fв:

τэкв=Cк4R10·(1-Ti), (6)

f в = f в ∗ 1 − T i > > f в ∗ , ( 7 )

где f в ∗ - верхняя граничная частота в КУ с составным транзистором-прототипом фиг.1.

Данные теоретические выводы подтверждают результаты моделирования, показанные на чертеже фиг.7, - верхняя граничная частота fв увеличивается в 7-8 раз (для техпроцесса ФГУП НПП «Пульсар»).

Вторая замечательная особенность заявляемого СТ - компенсация влияния паразитных емкостей коллектор-база Cкl и Ск6 транзисторов 1 и 6 на входную комплексную проводимость схемы. Действительно эквивалентная входная емкость КУ в схеме фиг.4:

Свх=Ск1(1-Ку1)+Ск6(1-Ку2)<<Ск1, (8)

где К у l = u э 4 u в х ≈ 1 - коэффициент передачи напряжения uвх в эмиттер транзистора 4;

К = у 2 u э l u в х ≈ 1 - коэффициент передачи напряжения uвх в эмиттер транзистора 1.

Третья замечательная особенность заявляемого СТ - малый входной статический ток, который может быть близок к аналогичному параметру полевых транзисторов:

I в х = I б 1 − I б 6 = I э l β l − I 7 β 6 , ( 9 )

где Iбl, Iб6 - статические токи базы транзисторов 1 и 6;

βl,β6 - коэффициенты усиления по току базы транзисторов 1 и 6.

Из (9) следует, что за счет соответствующего выбора статического тока источника опорного тока 7 можно получить нулевой входной ток в схеме фиг.4 и его относительно слабую температурную зависимость (см. фиг.10).

Данные теоретические выводы подтверждают графики фиг.10, из которых следует, что температурные приращения входного тока заявляемого СТ в диапазоне температур 60÷80°С в 9-10 раз меньше, чем в схеме СТ-прототипа.

Таким образом, заявляемое схемотехническое решение СТ характеризуется более высокими значениями верхней граничной частоты, меньшей величиной входной емкости, меньшим уровнем входного статического тока и его температурного дрейфа.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6.825.723 fig.3

2. Патент США №4.151.483 fig.2

3. Патент США №4.151.484

4. Патент США №3.882.410 fig.3

5. Патентная заявка WO 2004/030207

6. Патент США №4.021.749 fig.2

7. Патент США №3.693.108 fig.9

8. Патент США №6.278.329

9. Патентная заявка США 2005/0225397

10. Патент США №5.451.906

11. Патент Англии GB №1431481 fig.2

12. Патент US №3.693.108 fig. 9

13. Патент US №4.021.749 fig. 2

14. Патентная заявка US 2005/0225397

15. Патент US №6.278.329.

1. Составной транзистор, содержащий входной транзистор (1), база которого является базой (2), а эмиттер - эмиттером (3) составного транзистора, выходной транзистор (4), коллектор которого является коллектором (5) составного транзистора, а эмиттер соединен с коллектором входного транзистора (1), отличающийся тем, что в схему введен дополнительный транзистор (6), статический режим которого по току эмиттера устанавливается дополнительным источником опорного тока (7), включенным между первой (8) шиной источника питания и эмиттером дополнительного транзистора (6), причем база дополнительного транзистора (6) соединена с базой входного транзистора (1), его коллектор связан с эмиттером входного транзистора (1), а эмиттер подключен к базе выходного транзистора (4).

2. Составной транзистор по п.1, отличающийся тем, что база входного транзистора (1) соединена с источником входного напряжения (9), между первой (8) шиной источника питания и коллектором выходного транзистора (4) включен резистор коллекторной нагрузки (10), а эмиттер входного транзистора (1) соединен по переменному току со второй (11) шиной источника питания через резистор местной обратной связи (12), а также соединен со второй (11) шиной источника питания через токостабилизирующий двухполюсник (13).