Устройство обработки данных и способ переключения рабочей нагрузки между первой и второй компоновкой схем обработки

Иллюстрации

Показать всеИзобретение относится к устройству обработки данных и способу переключения рабочей нагрузки между первой и второй компоновкой схем обработки. Техническим результатом является повышение эффективности использования энергии устройством обработки данных. Устройство обработки данных содержит первую компоновку схем обработки, которая является архитектурно совместимой со второй компоновкой схем обработки, но при этом первая компоновка схем обработки отличается с точки зрения микроархитектуры от второй компоновки схем обработки. Во время операции передачи обслуживания, контроллер переключения обеспечивает предоставление исходной компоновкой схем обработки своего текущего состояния архитектуры целевой компоновке схем обработки, причем текущим состоянием архитектуры является то состояние, которое не доступно из совместно используемой памяти в момент инициирования операции передачи обслуживания, и которое является необходимым целевой компоновке схем обработки, чтобы успешно принять на себя выполнение рабочей нагрузки из исходной компоновки схем обработки. 3 н. и 17 з.п. ф-лы, 19 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству обработки данных и способу переключения рабочей нагрузки между первой и второй компоновкой схем обработки, и в частности к способу выполнения указанного переключения для повышения эффективности использования энергии устройством обработки данных.

Предшествующий уровень техники

В современных системах обработки данных, различие в требовании к производительности между задачами, требующими большой производительности, например функционирование игр, и задачами, требующими малой производительности, например воспроизведение MP3-файлов, может превышать отношение 100:1. В случае использования одного процессора для всех задач, этот процессор должен иметь высокую производительность, но для микроархитектуры процессоров существует аксиома, что высокопроизводительные процессоры менее эффективно используют энергию, чем малопроизводительные процессоры. Известно, что для увеличения эффективности использования энергии на уровне процессора с использованием таких способов, как Динамическое масштабирование напряжения и частоты (Dynamic Voltage and Frequency Scaling, DVFS) или выборочная подача питания для обеспечения процессора диапазоном уровней производительности и соответствующими характеристиками потребления энергии. Однако обычно указанных способов становится недостаточно для обеспечения возможности одному процессору брать на себя задачи с указанным расхождением в требованиях к производительности.

Соответственно, предложено использование многоядерной архитектуры для обеспечения системы с эффективным использованием энергии для выполнения таких различных задач. В то время как, с обеспечением возможности разным ядрам параллельно выполнять разные задачи для увеличения пропускной способности, многоядерные системы уже в течение некоторого времени используются для увеличения производительности, исследование того, как такие системы могут использоваться для повышения эффективности использования энергии, является последним достижением техники.

В статье "Towards Better Performance Per Watt in Virtual Environments on Asymmetric Single-ISA Multi-Core Systems", V Kumar и др., ACM SIGOPS Operating Systems Review, Volume 43, Issue 3 (July 2009) обсуждаются многоядерные системы с Асимметричной единой архитектурой набора команд (Asymmetric Single Instruction Set Architecture, ASISA), состоящие из нескольких ядер, предоставляющих идентичную архитектуру набора команд (ISA), но отличающихся особенностями, сложностью, потреблением энергии и производительностью. В этой статье исследуются свойства виртуализированных рабочих нагрузок для понимания того, как эти рабочие нагрузки должны планироваться в системах ASISA, чтобы улучшить производительность и потребление энергии. В этой статье указывается, что определенные задачи больше подходят для микроархитектур с высокой частотой/производительностью (обычно задачи, требующие большой вычислительной мощности), в то время как другие больше подходят для микроархитектур с меньшей частотой/производительностью, и как побочный эффект потребляют меньше энергии (обычно задачи, требующие производительности ввода/вывода). Несмотря на то что эти исследования показывают то, как можно использовать системы ASISA для выполнения различных задач при эффективном использовании энергии, по-прежнему существует потребность в обеспечении механизма для планирования отдельных задач для более подходящих процессоров, и такое управление планированием обычно является существенной нагрузкой на операционную систему.

В статье "Single-ISA Heterogeneous Multi-Core Architectures: The Potential for Processor Power Reduction", R Kumar и др., Proceedings of the 36th International Symposium of Microarchitecture (MICRO-36'03) обсуждается многоядерная архитектура, в которой все ядра исполняют идентичный набор команд, но имеют разные возможности и уровни производительности. Во время выполнения, системное программное обеспечение оценивает требования к ресурсам приложения и выбирает ядро, которое лучше других удовлетворяет этим требованиям наряду с тем, что минимизирует потребление энергии. Как обсуждается в разделе 2 этой статьи, во время исполнения приложения, программное обеспечение операционной системы сопоставляет это приложение с разными ядрами, чтобы подобрать ядро, удовлетворяющее определенному критерию выбора, например конкретному требованию к производительности. В разделе 2.3 отмечается, что существуют затраты на переключение ядер, которые неизбежно влекут за собой ограничение степени разбиения переключения. Далее обсуждается конкретный пример, в котором, если операционная система на основе логики принимает решение о переключении, то она включает питание нового ядра, запускает сброс кэша и сохраняет все измененные данные кэша в совместно используемой структуре памяти, и после этого подает сигнал в новое ядро для запуска в предопределенной точке входа в операционной системе. Питание старого ядра может после этого быть выключено, в то время как новое ядро осуществляет выборку данных из памяти. Такой подход описывается в разделе 2.3 как обеспечивающий возможность переключения приложения между ядрами операционной системой. В остальной части статьи обсуждается то, как динамически можно выполнять указанное переключение в условиях многоядерной окружающей среды с целью сокращения потребления энергии.

Несмотря на то что в вышеупомянутой статье обсуждается потенциальная возможность обеспечения сокращения потребления энергии посредством неоднородных многоядерных архитектур с единой ISA, по-прежнему требуется обеспечить операционную систему достаточной функциональностью для обеспечения возможности принятия решений по планированию отдельных приложений. При переключении между экземплярами процессоров с разными архитектурными особенностями, Функция операционной системы в этом отношении становится более сложной. В связи с этим следует отметить, что ядра Alpha EV4-EV8 рассматриваются в этой статье как не полностью совместимые с ISA, как обсуждается, например, в пятом параграфе раздела 2.2.

Кроме того, в этой статье не решается проблема существования значительных затрат, связанных с переключением приложений между ядрами, которые могут значительно уменьшить преимущества, которые получают от указанного переключения.

Сущность изобретения

С точки зрения первого аспекта, настоящее изобретение обеспечивает устройство обработки данных, содержащее: первую компоновку схем обработки для выполнения операций обработки данных, вторую компоновку схем обработки для выполнения операций обработки данных, причем первая компоновка схем обработки является архитектурно совместимой со второй компоновкой схем обработки, так что рабочая нагрузка, выполняемая устройством обработки данных, может выполняться или на первой компоновке схем обработки, или на второй компоновке схем обработки, причем упомянутая рабочая нагрузка содержит, по меньшей мере, одно приложение и, по меньшей мере, одну операционную систему для выполнения упомянутого, по меньшей мере, одного приложения, причем первая компоновка схем обработки отличается с точки зрения микроархитектуры от второй компоновки схем обработки, так что производительность первой компоновки схем обработки отличается от производительности второй компоновки схем обработки, причем первая и вторая компоновка схем обработки сконфигурированы так, что рабочая нагрузка выполняется одной из первой компоновки схем обработки и второй компоновки схем обработки в любой момент времени, контроллер переключения, реагирующий на управляющее воздействие для переноса, для выполнения операции передачи обслуживания для переноса выполнения рабочей нагрузки из исходной компоновки схем обработки на целевую компоновку схем обработки, причем исходной компоновкой схем обработки является одна из первой компоновки схем обработки и второй компоновки схем обработки, а целевой компоновкой схем обработки является другая из первой компоновки схем обработки и второй компоновки схем обработки, причем контроллер переключения выполнен с возможностью, во время операции передачи обслуживания: (i) вызова предоставления исходной компоновкой схем обработки своего текущего состояния архитектуры целевой компоновке схем обработки, причем текущим состоянием архитектуры является то состояние, которое не доступно из совместно используемой памяти, разделяемой между первой и второй компоновкой схем обработки, в момент инициирования операции передачи обслуживания, и которое является необходимым целевой компоновке схем обработки, чтобы успешно принять на себя выполнение рабочей нагрузки из исходной компоновки схем обработки, и (ii) маскирования предопределенной конкретной для процессора информации о конфигурации от упомянутой, по меньшей мере, одной операционной системы, так что перенос рабочей нагрузки является прозрачным для упомянутой, по меньшей мере, одной операционной системы.

Согласно настоящему изобретению, устройство обработки данных обеспечено с первой и второй компоновкой схем обработки, которые являются архитектурно совместимыми друг с другом, но разными с точки зрения микроархитектуры. Вследствие архитектурной совместимости первой и второй компоновки схем обработки, рабочая нагрузка, состоящая не только из одного или нескольких приложений, но также включающая в себя, по меньшей мере, одну операционную систему для выполнения этих одного или нескольких приложений, может перемещаться между первой и второй компоновкой схем обработки. Кроме того, так как первая и вторая компоновки схем обработки являются разными с точки зрения микроархитектуры, то характеристики производительности (а следовательно, характеристики потребления энергии) первой и второй компоновки схем обработки отличаются.

Согласно настоящему изобретению, в любой момент времени рабочая нагрузка выполняется одной из первой или второй схем обработки, и контроллер переключения реагирует на управляющее воздействие для переноса для выполнения операции передачи обслуживания для переноса выполнения рабочей нагрузки между упомянутыми схемами обработки. При приеме управляющего воздействия для переноса, та из двух схем обработки, которая в настоящее время выполняет рабочую нагрузку, рассматривается как исходная компоновка схем обработки, а другая рассматривается как целевая компоновка схем обработки. Контроллер переключения, отвечающий за выполнение операции передачи обслуживания, вызывает предоставление текущего состояния архитектуры исходной компоновки схем обработки целевой компоновке схем обработки, а также маскирует предопределенную конкретную для процессора информацию о конфигурации от, по меньшей мере, одной операционной системы, формирующей часть рабочей нагрузки, так что перенос рабочей нагрузки является прозрачным для этой операционной системы.

С использованием настоящего изобретения можно переносить всю рабочую нагрузку с одной компоновки схем обработки на другую при маскировании этого переноса от операционной системы и при обеспечении того, что необходимое состояние архитектуры, которое не доступно в совместно используемой памяти в момент инициирования операции передачи обслуживания, предоставляется целевой компоновке схем обработки, так что она успешно может принять на себя выполнение рабочей нагрузки.

При рассмотрении всей рабочей нагрузки как макроскопического объекта, который выполняется только на одной из первой и второй схем обработки в любой конкретный момент времени, способ настоящего изобретения обеспечивает возможность быстрого переключения рабочей нагрузки между первой и второй схемами обработки прозрачно для операционной системы, и в то же время обеспечивает то, что целевая схема обработки имеет всю информацию, необходимую для обеспечения ей возможности принимать на себя выполнение рабочей нагрузки. Такой подход решает ранее упомянутые проблемы, которые возникают в результате использования операционной системы для управления планированием приложений для конкретных схем обработки, и, как обнаружено, обеспечивает возможность получения значительной экономии потребления энергии.

В одном варианте осуществления, устройство обработки данных также содержит: компоновку схем управления питанием для независимого управления питанием, обеспечиваемого первой компоновке схем обработки и второй компоновке схем обработки, причем до осуществления управляющего воздействия для переноса целевая компоновка схем обработки находится в режиме экономии энергии, а во время операции передачи обслуживания компоновка схем управления питанием вызывает выход целевой компоновки схем обработки из режима экономии энергии до того, как целевая компоновка для обработки примет на себя выполнение рабочей нагрузки. С использованием указанной компоновки схем управления питанием можно сократить энергию, потребляемую компоновкой схем обработки, которая в настоящее время не выполняет рабочую нагрузку.

В одном варианте осуществления, после операции передачи обслуживания, компоновка схем управления питанием вызывает переход компоновки схем обработки в режим экономии энергии. Это может происходить немедленно после операции передачи обслуживания, или в альтернативных вариантах осуществления исходная компоновка схем обработки может быть выполнена с возможностью перехода в режим экономии энергии только после истечения некоторого предопределенного периода времени, что может обеспечивать возможность предоставления данных, все еще хранящихся в памяти исходной компоновки схем обработки, целевой компоновке схем обработки с большей эффективностью использования энергии и более высокой производительностью.

Следующей проблемой, которая существует в известном уровне техники, независимо от способа, которым выполняется переключение между разными схемами обработки, является то, как быстро и при эффективном использовании энергии перенести информацию, требуемую для того, чтобы этот перенос был успешным. В частности, необходимо предоставлять вышеупомянутое текущее состояние архитектуры целевой компоновке схем обработки. Одним способом для достижения этого является переписывание всего этого текущего состояния архитектуры в совместно используемую память как часть операции передачи обслуживания, так что целевая компоновка схем обработки может его впоследствии считать из совместно используемой памяти. Как используется в этом описании, термин "совместно используемая память" относится к памяти, к которой может осуществить прямой доступ как первая компоновка схем обработки, так и вторая компоновка схем обработки, например основной памяти, соединенной как с первой, так и со второй компоновкой схем обработки через межсоединение.

Однако проблема, которая возникает при переписывании всего текущего состояния архитектуры в совместно используемую память, заключается в том, что указанный процесс не только занимает значительное количество времени, но также потребляет значительную энергию, что может существенно нейтрализовать потенциально возможные преимущества, которые могут быть получены с выполнением переключения.

Согласно одному варианту осуществления, во время операции переноса, контроллер переключения вызывает применение исходной компоновкой схем обработки ускоренного механизма для предоставления своего текущего состояния архитектуры целевой компоновке схем обработки без обращения целевой компоновки схем обработки к совместно используемой памяти для получения текущего состояния архитектуры. Следовательно, согласно указанным вариантам осуществления, обеспечен механизм, посредством которого избегают потребности в передаче состояния архитектуры через совместно используемую память для того, чтобы предоставить его целевой компоновке схем обработки. В результате не только повышается производительность во время операции переноса, но также сокращается потребление энергии, связанное с операцией переноса.

В одном варианте осуществления, по меньшей мере, упомянутая исходная компоновка схем имеет ассоциированный кэш, устройство обработки данных также содержит компоновку схем управления просмотром, и ускоренный механизм содержит перенос текущего состояния архитектуры в целевую компоновку схем обработки с использованием упомянутого ассоциированного кэша и упомянутой компоновки схем управления просмотром.

Согласно этому способу, локальный кэш исходной компоновки схем обработки используется для сохранения текущего состояния архитектуры, которое должно предоставляться целевому процессору. Это состояние далее помечается как совместно используемое, что обеспечивает возможность просмотра этого состояния целевой компоновкой схем обработки с использованием компоновки схем управления просмотром. Следовательно, в указанном варианте осуществления, первая и вторая компоновка схем обработки выполняются с когерентными друг другу аппаратными кэшами, это сокращает количество времени, энергию и сложность аппаратного обеспечения, связанные с переключением с исходной компоновки схем обработки на целевую компоновку схем обработки.

В одном конкретном варианте осуществления, ускоренный механизм является механизмом сохранения и восстановления, который вызывает сохранение исходной компоновкой схем обработки своего текущего состояния архитектуры в ассоциированном с ней кэше, и вызывает выполнение целевой компоновкой схем обработки операции восстановления, посредством которой компоновка схем управления просмотром извлекает текущее состояние архитектуры из ассоциированного кэша исходной компоновки схем обработки и обеспечивает это извлеченное текущее состояние архитектуры в целевую компоновку схем обработки. Механизм сохранения/восстановления обеспечивает особенно эффективный способ сохранения состояния архитектуры в локальном кэше исходной компоновки схем обработки и впоследствии извлечения этого состояния для целевой компоновки схем обработки.

Такой подход может быть использован вне зависимости от того, имеет ли целевая компоновка схем обработки свой собственный ассоциированный с ней локальный кэш или нет. Каждый раз, когда компоновка схем управления просмотром принимает запрос на элемент состояния архитектуры, либо непосредственно из целевой компоновки схем обработки или из ассоциированного локального кэша целевой компоновки схем обработки в случае промаха кэша, она устанавливает то, что этот требуемый элемент состояния архитектуры хранится в локальном кэше, ассоциированном с исходной компоновкой схем, и извлекает эти данные из локального кэша исходной компоновки схем для возвращения в целевую компоновку схем обработки (либо непосредственно или через ассоциированный кэш целевой компоновки схем обработки, если он существует).

В одном конкретном варианте осуществления, целевая компоновка схем обработки имеет ассоциированный кэш, в котором переносимое состояние архитектуры, полученное компоновкой схем управления просмотром, сохраняется для обращения (к нему) целевой компоновки схем обработки.

Однако подход когерентности аппаратного кэша, описанный выше, не является единственным способом, который можно использовать для обеспечения ранее упомянутого ускоренного механизма. Например, в альтернативном варианте осуществления, ускоренный механизм содержит выделенную шину между исходной компоновкой схем обработки и целевой компоновкой схем обработки, по которой исходная компоновка схем обработки обеспечивает свое текущее состояние архитектуры в целевую компоновку схем обработки. Несмотря на то что при таком подходе обычно существуют большие затраты на аппаратное обеспечение, чем при подходе когерентности кэша, он обеспечивает еще более быстрый способ выполнения переноса, от которого можно получить преимущества в определенных реализациях.

Контроллер переключения может принимать множество форм. Однако в одном варианте осуществления контроллер переключения содержит, по меньшей мере, программное обеспечение виртуализации, логически отделяющее, по меньшей мере, одну операционную систему от первой компоновки схем обработки и второй компоновки схем обработки. Известно использование виртуальных машин для обеспечения возможности исполнения приложений, написанных с использованием конкретного набора собственных команд, на аппаратном обеспечении, имеющем отличный набор собственных команд. Приложения исполняются в среде виртуальной машины, причем команды приложений являются собственными для виртуальной машины, но виртуальная машина реализуется программным обеспечением, исполняющимся на аппаратном обеспечении, имеющем отличный набор собственных команд. Программное обеспечение виртуализации, обеспечиваемое контроллером переключения вышеупомянутого варианта осуществления, может рассматриваться как функционирующее аналогично гипервизору в среде виртуальной машины, так как оно обеспечивает разделение между рабочей нагрузкой и лежащей в основе аппаратной платформой. В контексте настоящего изобретения, программное обеспечение виртуализации обеспечивает эффективный механизм для переноса рабочей нагрузки с одной компоновки схем обработки на другую компоновку схем обработки при маскировании конкретной для процессора информации о конфигурации от операционных(ой) систем(ы), формирующих(ей) эту рабочую нагрузку.

Управляющее воздействие для переноса может генерироваться по множеству причин. Однако, в одном варианте осуществления, тайминг управляющего воздействия для переноса выбирается так, чтобы улучшить эффективность использования энергии устройством обработки данных. Это может достигаться множеством способов. Например, могут быть установлены счетчики производительности для подсчета событий, чувствительных к производительности (например, количество исполнимых команд или количество операций загрузки/сохранения). По сравнению со счетчиком циклов или системным таймером, это обеспечивает возможность идентификации того, что исполняется приложение, требующее очень большой вычислительной мощности, которое может лучше обслуживаться при переключении на компоновку схем обработки с большей производительностью, идентификации большого количества операций загрузки/сохранения, указывающие на приложение, требующее производительности IO (ввода/вывода), которые могут лучше обслуживаться на компоновке схем обработки с эффективным использованием энергии, и т.д. Альтернативным подходом является задание профиля приложений и пометка их как "большой", "маленький" или "большой/маленький", в результате чего операционная система может служить интерфейсом с контроллером переключения для перемещения рабочей нагрузки соответственно (здесь термин "большой" относится к компоновке схем обработки с большей производительностью, а термин "маленький" относится к компоновке схем обработки с эффективным использованием энергии).

Состояние архитектуры, которое требуется для целевой компоновки схем обработки, чтобы успешно принять на себя выполнение рабочей нагрузки от исходной компоновки схем обработки, может принимать множество форм. Однако, в одном варианте осуществления, состояние архитектуры содержит, по меньшей мере, текущее значение одного или нескольких специальных регистров исходной компоновки схем обработки, в том числе значение счетчика команд. Наряду со значением счетчика команд, различную другую информацию, которая может храниться в специальных регистрах. Например, другие специальные регистры включают в себя регистры состояния процессора (например, CPSR и SPSR в архитектуре ARM), которые содержат в себе управляющие биты для режима процессора, маскирования прерываний, рабочего состояния и флагов. Другие специальные регистры включают в себя архитектурный надзор (регистр управления системой CP15 в архитектуре ARM), который содержит биты для изменения порядка следования байтов данных, включения или выключения MMU, включения или выключения кэшей данных/команд и т.д. В других специальных регистрах в CP15 хранится информация о состоянии и адресе исключения.

В одном варианте осуществления, состояние архитектуры также содержит текущие значения, хранящиеся в архитектурном регистровом файле исходной компоновки схем обработки. Специалистам в данной области техники очевидно, что архитектурный регистровый файл содержит регистры, к которым обращаются команды, исполняемые во время выполнения приложения, причем эти регистры содержат исходные операнды для вычислений и обеспечивают адреса ячеек памяти, в которых сохраняются результаты этих вычислений.

В одном варианте осуществления, по меньшей мере, одна из первой компоновки схем обработки и второй компоновки схем обработки содержит один блок обработки. Кроме того, в одном варианте осуществления, по меньшей мере, одна из первой компоновки схем обработки и второй компоновки схем обработки содержит группу блоков обработки с идентичной микроархитектурой. В одном конкретном варианте осуществления, первая компоновка схем обработки может содержать группу блоков обработки с идентичной микроархитектурой, в то время как вторая компоновка схем обработки содержит один блок обработки (с отличной микроархитектурой по сравнению с микроархитектурой блоков обработки в пределах группы, формирующей первую компоновку схем обработки).

Режим экономии энергии, в который компоновка схем управления питанием может выборочно переводить первую и вторую схемы обработки, может принимать множество форм. В одном варианте осуществления, режим экономии энергии является одним из: режима с отключенным питанием, режима частичного/полного сохранения данных или режима ожидания. Для специалиста в данной области техники такие режимы являются очевидными, и, соответственно, в данном описании более подробно не обсуждаются.

Существует несколько способов выполнения первой и второй схем обработки с разной микроархитектурой. В одном варианте осуществления, первая компоновка схем обработки и вторая компоновка схем обработки отличаются с точки зрения микроархитектуры наличием, по меньшей мере, одного из: разных длин исполнительного конвейера и разных исполнительных ресурсов. Различия в длине конвейера обычно в результате приводят к различиям в рабочей частоте, которые, в свою очередь, оказывают влияние на производительность. Аналогично, различия в исполнительных ресурсах оказывают влияние на пропускную способность и, следовательно, на производительность. Например, схема обработки, имеющая более значительные исполнительные ресурсы, обеспечивает возможность обработки большей информации в любой конкретный момент времени, при этом повышает пропускную способность. Дополнительно, или в качестве альтернативы, одна схема обработки может иметь больше исполнительных ресурсов, чем другая, например, большее количество арифметико-логических устройств (АЛУ, ALU), которые также повышают пропускную способность. В качестве другого примера разных исполнительных ресурсов, схема обработки с эффективным использованием энергии может быть обеспечена простым конвейером с последовательностью исполнения команд по порядку, в то время как схема обработки с более высокой производительностью может быть обеспечена суперскалярным конвейером с переупорядочением последовательности команд.

Следующей проблемой, которая может возникнуть при использовании высокопроизводительных схем обработки, например, функционирующих с частотами, измеряемыми в гигагерцах (ГГц), является то, что такие процессоры приближаются к пределам по нагреву, для функционирования в которых они предназначены, а иногда превышают их. Известные способы поиска решения этих проблем могут включать в себя перевод схемы обработки в режим с малым энергопотреблением для сокращения тепловыделения, что может включать в себя пропуск отдельных тактовых импульсов и/или снижение напряжения, а возможно даже полное отключение схемы обработки на некоторый период времени. Однако при внедрении способа вариантов осуществления настоящего изобретения возможна реализация альтернативного подхода для устранения превышения пределов по нагреву. В частности, в одном варианте осуществления, исходная компоновка схем обработки имеет более высокую производительность, чем целевая компоновка схем обработки, и устройство обработки данных также содержит компоновку схем текущего контроля нагрева для текущего контроля теплоотдачи исходной компоновки схем обработки и для запуска упомянутого управляющего воздействия для переноса, когда упомянутая теплоотдача достигнет предопределенного уровня. В соответствии с указанными способами, вся рабочая нагрузка может быть перемещена с компоновки схем обработки с более высокой производительностью на компоновку схем обработки с меньшей производительностью, после чего будет выделяться меньше тепла, что обеспечит возможность охлаждения исходной компоновки схем обработки. Следовательно, комплект, содержащий две схемы обработки, может охлаждаться наряду с продолжением исполнения программ, хотя и с меньшей пропускной способностью.

Устройство обработки данных может быть выполнено множеством способов. Однако в одном варианте осуществления первая компоновка схем обработки и вторая компоновка схем обработки находятся на одной интегральной схеме.

С точки зрения второго аспекта, настоящее изобретение обеспечивает устройство обработки данных, содержащее: первое средство обработки для выполнения операций обработки данных, второе средство обработки для выполнения операций обработки данных, причем первое средство обработки является архитектурно совместимым со вторым средством обработки, так что рабочая нагрузка, выполняемая устройством обработки данных, может выполняться на любом из первого средства обработки и второго средства обработки, причем упомянутая рабочая нагрузка содержит, по меньшей мере, одно приложение и, по меньшей мере, одну операционную систему для выполнения упомянутого одного приложения, причем первое средство обработки отличается с точки зрения микроархитектуры от второго средства обработки, так что производительность первого средства обработки отличается от производительности второго средства обработки, причем первое и второе средство обработки сконфигурированы так, что рабочая нагрузка выполняется одним из первого средства обработки и второго средства обработки в любой момент времени, средство управления переносом, реагирующее на управляющее воздействие для переноса, для выполнения операции передачи обслуживания для переноса выполнения рабочей нагрузки с исходного средства обработки на целевое средство обработки, причем исходным средством обработки является одно из первого средства обработки и второго средства обработки, а целевым средством обработки является другое из первого средства обработки и второго средства обработки, причем это средство управления переносом (выполнено с возможностью), во время операции передачи обслуживания: (i) вызова предоставления исходным средством обработки своего текущего состояния архитектуры целевому средству обработки, причем текущим состоянием архитектуры является то состояние, которое не доступно из совместно используемого средства памяти, разделяемого между первым и вторым средством обработки, в момент инициирования операции передачи обслуживания, и которое является необходимым целевому средству обработки, чтобы успешно принять на себя выполнение рабочей нагрузки из исходного средства обработки, и (ii) маскирования предопределенной конкретной для процессора информации о конфигурации от упомянутой, по меньшей мере, одной операционной системы, так что передача рабочей нагрузки является прозрачной для упомянутой, по меньшей мере, одной операционной системы.

С точки зрения третьего аспекта, настоящее изобретение обеспечивает способ функционирования устройства обработки данных, содержащего первую компоновку схем обработки для выполнения операций обработки данных и вторую компоновку схем обработки для выполнения операций обработки данных, причем первая компоновка схем обработки является архитектурно совместимой со второй компоновкой схем обработки, так что рабочая нагрузка, выполняемая устройством обработки данных, может выполняться или на первой компоновке схем обработки, или на второй компоновке схем обработки, причем упомянутая рабочая нагрузка содержит, по меньшей мере, одно приложение и, по меньшей мере, одну операционную систему для выполнения упомянутого, по меньшей мере, одного приложения, и причем первая компоновка схем обработки отличается с точки зрения микроархитектуры от второй компоновки схем обработки, так что производительность первой компоновки схем обработки отличается от производительности второй компоновки схем обработки, причем этот способ содержит шаги: выполнения, в любой момент времени, рабочей нагрузки на одной из первой компоновки схем обработки и второй компоновки схем обработки, выполнения, в ответ на управляющее воздействие для переноса, операции передачи обслуживания для переноса выполнения рабочей нагрузки с исходной компоновки схем обработки на целевую компоновку схем обработки, причем исходной компоновкой схем обработки является одна из первой компоновки схем обработки и второй компоновки схем обработки, а целевой компоновкой схем обработки является другая из первой компоновки схем обработки и второй компоновки схем обработки, во время операции передачи обслуживания: (i) вызова предоставления исходной компоновкой схем обработки своего текущего состояния архитектуры целевой компоновке схем обработки, причем текущим состоянием архитектуры является то состояние, которое не доступно из совместно используемой памяти, разделяемой между первой и второй компоновкой схем обработки, в момент инициирования операции передачи обслуживания, и которое является необходимым целевой компоновке схем обработки, чтобы успешно принять на себя выполнение рабочей нагрузки из исходной компоновки схем обработки, и (ii) маскирования предопределенной конкретной для процессора информации о конфигурации от упомянутой, по меньшей мере, одной операционной системы, так что передача рабочей нагрузки является прозрачной для упомянутой, по меньшей мере, одной операционной системы.

Краткое описание чертежей

Далее настоящее изобретение описывается, только для примера, со ссылкой на его варианты осуществления, иллюстрированные на прилагаемых чертежах, в которых:

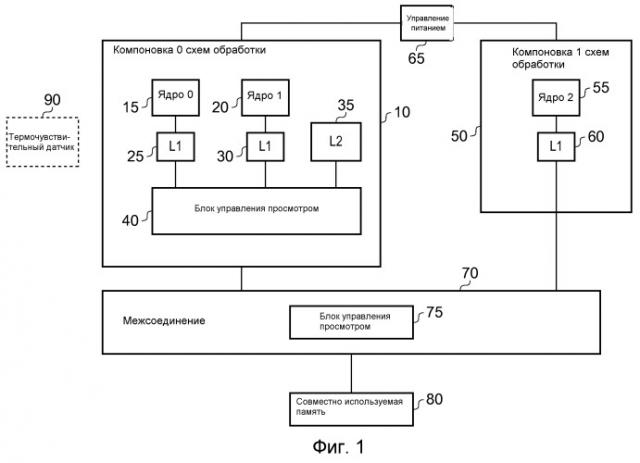

Фиг.1 - блок-схема системы обработки данных в соответствии с одним вариантом осуществления.

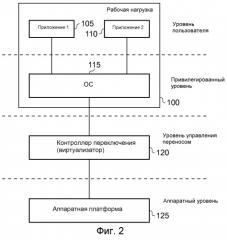

На фиг.2 схематически изображено обеспечение контроллера переключения (в этом описании также называемого контроллером переноса рабочей нагрузки) в соответствии с одним вариантом осуществления для логического отделения рабочей нагрузки, выполняемой устройством обработки данных, от конкретной аппаратной платформы внутри устройства обработки данных, используемого для выполнения этой рабочей нагрузки.

Фиг.3 - схема, на которой схематически изображены шаги, выполняемые как исходным процессором, так и целевым процессором в ответ на управляющее воздействие для переключения для переноса рабочей нагрузки с исходного процессора на целевой процессор, в соответствии с одним вариантом осуществления.

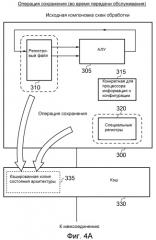

На фиг.4A схематически изображено сохранение текущего состояния архитектуры исходной компоновки схем обработки в ассоциированном с ней кэше в течение операции сохранения по фиг.3.

На фиг.4B схематически изображено использование блока управления просмотром для управления переносом текущего состояния архитектуры исходной схемы обработки в целевую схему обработки во время операции восстановления по фиг.3.

На фиг.5 изображена альтернативная структура для обеспечения ускоренного механизма для переноса текущего состояния архитектуры исходной компоновки схем обработки на целевую компоновку схем обработки во время операции переноса, в соответствии с одним вариантом осуществления.

На фиг.6A-6I схематически изображены шаги в