Способ и устройство двухтактного интегрирования

Иллюстрации

Показать всеГруппа изобретений относится к автоматике и аналоговой вычислительной технике и предназначено для построения прецизионных аналоговых устройств управления в аэрокосмической технике, функциональных узлов аналоговых вычислительных машин, аналоговых процессоров. Техническим результатом является повышение точности вычисления интегральной функции входного напряжения. Устройство содержит интегратор, коммутатор, два замыкающих ключа, два блока аналоговой памяти, два сумматора. 2 н.п. ф-лы, 2 ил.

Реферат

Область техники

Изобретение относится к автоматике и аналоговой вычислительной технике и предназначено для построения функциональных узлов аналоговых вычислительных машин, прецизионных аналоговых устройств управления в аэрокосмической технике, аналоговых процессоров и др.

Уровень техники

Известны способы снижения погрешностей от входных токов и напряжения смещения, применяемые для уменьшения погрешности интеграторов на основе операционных усилителей (Дж. Рутковский. Интегральные операционные усилители. М.: «Мир», 1978 г. с.71-82), в которых выполняются компенсационные мероприятия путем введения дополнительных резисторов в цепи операционного усилителя. Недостатком способа является необходимость индивидуального подбора резисторов для каждого операционного усилителя и учета в процессе проектирования влияния дополнительных элементов на функционирование устройства.

Известен способ выборочного интервального интегрирования напряжения (см. патент 2218599, Россия), в котором снижение погрешностей от интегрирования входных токов и напряжения смещения активного элемента без увеличения методической погрешности интегрирования напряжения достигается тем, что процесс интегрирования разбивается на циклы, состоящие из интервалов, в течение одного из которых производится интегрирование входного напряжения, а остальные интервалы составляют паузу, в которой изменяется структура активного интегратора для предотвращения интегрирования входных токов и напряжения смещения, после завершения процесса интегрирования результат умножают на количество интервалов. К причинам, препятствующим достижению указанного ниже технического результата, относятся проведение интегрирования в течение ряда циклов, что значительно снижает быстродействие, ограничение формы сигнала только периодическими функциями, усложняется аппаратная реализация способа, в способ не встроены мероприятия по измерению и коррекции ошибок.

Наиболее близким к предлагаемому является способ интегрирования периодического напряжения (см. патент 2247428, Россия), в котором снижение погрешностей от интегрирования входных токов и напряжения смещения активного элемента достигается тем, что процесс интегрирования разбивается на N тактов, включающих рабочие такты и такты коррекции смещения нулевого уровня, и дополнительно разбивается на два равных по длительности цикла, кратных периоду входного напряжения так, что количество тактов в каждом цикле равно N/2, при этом в течение первого цикла рабочими являются нечетные такты, а тактами коррекции - четные, в течение второго цикла рабочими являются четные такты, а тактами коррекции - нечетные. К причинам, препятствующим достижению указанного ниже технического результата при использовании прототипа, относятся ограничение формы сигнала только периодическими функциями, необходимость введения дополнительных, в способ не встроены мероприятия по измерению и коррекции ошибок.

Известен интегратор тока (см. патент 2442177, Россия), в котором снижение погрешностей интегрирования достигается за счет того, что устройство содержит основной и вспомогательный интеграторы тока, каждый из которых содержит истоковый повторитель на полевом транзисторе с изолированным затвором, выход которого подключен к инвертирующему входу операционного усилителя, а конденсатор включен между выходом операционного усилителя и затвором транзистора, причем вход первого интегратора через ключ и резистор соединен с землей, а выход через другой ключ соединен со входом второго интегратора. Выход последнего через резистор соединен с тем контактом балансировки первого усилителя, подключение к которому обеспечивает отрицательную обратную связь при замыкании указанного другого ключа. Недостатком устройства является необходимость предварительной (до интегрирования) балансировки интегратора и ограничение применения устройства малыми значениями токов.

Наиболее близким к предлагаемому является устройство для интегрирования (см. патент 2222827, Россия), в котором увеличение точности интегрирования обеспечивается применением схемы, содержащей два блока интегрирования, источник образцового напряжения, формирователь импульсов, формирователь образцового временного интервала и блок сравнения длительностей импульсов. Выходной сигнал блока поступает на второй информационный вход блока интегрирования, который компенсирует влияние дестабилизирующих факторов на выходной сигнал интегрирующего устройства. Влияние дестабилизирующих факторов на выходной сигнал интегрирующего устройства уменьшается путем подачи напряжения, компенсирующего погрешности, на инверсный вход второго блока интегрирования.

К причинам, препятствующим достижению указанного ниже технического результата, относятся ограничение применимостью только для интегрирования постоянных напряжений, необходимость проведения измерений величины ошибки с помощью дополнительных блоков, влияние стабильности и точности дополнительных блоков на коррекцию ошибок интегрирования, последнее значительно усложняет достижение требуемого технического результата.

Технический результат заключается в повышении точности вычисления интегральной функции входного напряжения без предварительного подбора элементов интегратора.

Поставленная цель в способе достигается тем, что на входе интегратора за два равных временных интервала формируется сигнал, значение напряжения которого равно входному напряжению на первом временном интервале и нулю на втором, выходной сигнал находится как сумма двух составляющих, первая составляющая получается интегрированием интегратором входного сигнала на первом интервале, вторая - как разность первой составляющей и напряжения полученного интегрированием интегратором входного сигнала за весь период интегрирования, вторая составляющая в конце второго интервала равна ошибке интегрирования входного тока смещения и напряжения сдвига на первом временном интервале с обратным знаком, суммирование двух составляющих приводит к полной компенсации накопленной ошибки в конце второго интервала.

Поставленная цель достигается тем, что устройство содержит интегратор, коммутатор, два замыкающих ключа, два блока аналоговой памяти, первый сумматор, второй сумматор, информационный вход устройства подключен к первому контакту коммутатора, второй контакт коммутатора подключен к нулевому потенциалу, информационный вход интегратора подключен к третьему контакту коммутатора, замкнутому при отсутствии управляющего сигнала на управляющем входе коммутатора на землю и подключающему вход интегратора к информационному входу устройства при наличии управляющего сигнала, первый управляющий вход устройства подключен к управляющему контакту коммутатора и к управляющему контакту первого замыкающего ключа, второй управляющий вход устройства подключен к управляющему контакту второго замыкающего ключа, вход обнуления подключен к входу сброса интегратора, выход интегратора подключен к входным контактам первого и второго замыкающих ключей, выход первого замыкающего ключа подключен к входу первого блока аналоговой памяти, выход второго замыкающего ключа подключен к входу второго блока аналоговой памяти, выход первого блока аналоговой памяти подключен к первому входу сумматоров и к первому входу второго сумматора, выход второго блока аналоговой памяти подключен к инверсному входу первого сумматора, выход первого сумматора подключен к второму входу второго сумматора, выход второго сумматора подключен к выходу устройства.

Перечисленные отличительные признаки заявляемых изобретений позволяют повысить точность устройств интегрирования входных напряжений за счет компенсации воздействия паразитных токов и напряжений на входе интегратора за один период, не прибегая к повторным вычислениям.

Способ двухтактного интегрирования осуществляется следующим образом.

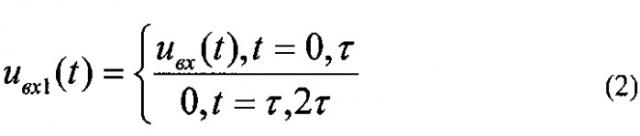

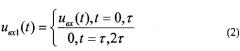

Для вычисления интеграла входного напряжения за временной интервал τ на вход устройства подается напряжение

Определение точного значения интегральной функции выполняется за два последовательных временных интервала длительностью τ каждый. На выходе устройства суммируются 2 функции напряжений

которые получаются путем интегрирования входного сигнала и паразитных составляющих, вносимых интегрированием входных токов смещения и напряжения сдвига на входе интеграторов, tи - время с момента начала интегрирования.

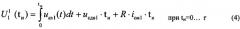

Напряжение получается интегрированием входного сигнала uвх1(t) интегратором. На первом интервале интегрирования:

На втором интервале это напряжение остается неизменным:

Напряжение получается как разность двух составляющих и

где - напряжение, полученное интегрированием uвх1(t) на интервале 2τ:

Вычитая из (4) (7) и из (5) (8), выделим значение ошибки интегратора за один интервал:

Подставляя формулы (4), (5), (9), (10) в (3), получим:

Из формулы (12) следует, что при tи=2τ результат интегрирования U∑(2τ) точно совпадает с математическим значением интеграла: , так как в устройстве, реализующем представленный способ интегрирования, полностью компенсируются погрешность интегратора, вносимая интегрированием входных токов смещения и напряжений сдвига.

На фиг.1 представлена структурная схема устройства, реализующего способ по изобретению.

На фиг.2 представлены эпюры напряжения двухтактного интегратора.

Устройство содержит интегратор (6), коммутатор (5), два замыкающих ключа (7), (8), два блока аналоговой памяти (9), (10), схему вычитания на сумматоре (11), второй сумматор (12), информационный вход (1) устройства подключен к первому контакту коммутатора (5), второй контакт коммутатора подключен к нулевому потенциалу, информационный вход интегратора (6) подключен к третьему контакту коммутатора (5), замкнутому при отсутствии управляющего сигнала на управляющем входе коммутатора на землю и подключающему вход интегратора к информационному входу (1) устройства при наличии управляющего сигнала, первый управляющий вход (3) устройства подключен к управляющему контакту коммутатора (5) и к управляющему контакту первого замыкающего ключа (7), второй управляющий вход (4) устройства подключен к управляющему контакту второго замыкающего ключа (8), вход обнуления (2) подключен к входу сброса интегратора (6), выход интегратора (6) подключен к входным контактам первого (7) и второго (8) замыкающих ключей, выход первого замыкающего ключа (7) подключен к входу первого блока аналоговой памяти (9), выход второго замыкающего (8) ключа подключен к входу второго блока аналоговой памяти (10), выход первого блока аналоговой памяти подключен к первому входу сумматоров (11) и к первому входу второго сумматора (12), выход второго блока аналоговой памяти подключен к инверсному входу первого сумматора (11), выход первого сумматора (11) подключен к второму входу второго сумматора (12), выход второго сумматора подключен к выходу устройства.

Рассмотрим работу устройства для случая, когда входной сигнал uвх(t) имеет форму прямоугольных импульсов длительностью τ (фиг.2). Интегрирование входного сигнала начинается с прекращением подачи напряжения сброса U2 на вход (2), подачи на вход (3) прямоугольного импульса периода интегрирования длительностью τ и на вход (4) прямоугольного импульса периода работы устройства U4 длительностью 2τ.

В первом временном интервале t1-t2 на управляющие контакты первого замыкающего ключа (7) и коммутатора (5) подается прямоугольный импульс периода интегрирования U3 длительностью τ, на управляющий контакт второго замыкающего ключа (8) подается прямоугольный импульс периода работы устройства U4 длительностью 2τ, при этом оба ключа замкнуты, коммутатор пропускает входной сигнал uвх(t) на вход интегратора (6), на выходе интегратора формируется сигнал интегральной функции входного напряжения за первый временной интервал t1-t2, содержащий ошибку, наведенную током смещения и напряжением сдвига. Этот сигнал через первый ключ (7) поступает в первый блок аналоговой памяти (9), и из него Uвых9 подается на первые входы сумматоров (11) и (12), через замкнутый ключ (8) сигнал интегратора поступает во второй блок аналоговой памяти (10), в котором формируется напряжение Uвых10, повторяющее в первом полупериоде Uвых9, и далее это напряжение поступает на инверсный вход первого сумматора (1). Таким образом, на выходе сумматора (11) и на втором входе сумматора (12) в первом временном интервале t1-t2 напряжение Uвых11 (t) будет нулевым.

В момент времени t2, через промежуток времени τ после начала интегрирования, импульс первого периода интегрирования U3 заканчивается, при этом ключ (7) размыкается, коммутатор подключает вход интегратора к нулевому потенциалу, и продолжает интегрироваться только наведенная ошибка, которая вместе с накопленной интегральной составляющей периода интегрирования τ передается через ключ (10) во второй блок аналоговой памяти (10). В первом блоке памяти (9) в интервале t2-t3 сохраняется накопленное за предыдущий интервал t1-t2 напряжение Uвых9(t1), равное интегралу входного напряжения плюс ошибка интегрирования за период τ. Оно подается на первые входы сумматоров (11) и (12). В процессе интегрирования во втором блоке памяти (10) формируется сигнал Uвых10, который накапливает ошибку интегрирования за весь период и суммирует ее с интегральной функцией входного напряжения первого интервала интегрирования. Этот сигнал подается на инверсный вход сумматора (11), вычитается из напряжения Uвых9(t2), формируя сигнал ошибки интегратора Uвых11(t) в течение всего интервала t2-t3 с обратным знаком. На выходе сумматора (7) происходит постепенная компенсация накопленной ошибки.

Начиная с момента времени t3 напряжение U4(t)=0, ключ (8) размыкается, во втором блоке памяти (10) фиксируются значения напряжений Uвых10(t3). В первом блоке памяти (9) значение напряжения равно интегральной функции вместе с ошибкой интегрирования за первый интервал t1-t2 Uвых9(t2), в блоке памяти (10) фиксируется значение Uвых10(t3), равное сумме интегральной функции за интервал t1-t2 и значения ошибки интегрирования, накопленной интегратором за интервал t1-t3. Uвых9(t2) подается на вход сумматора (11), а на его инверсный вход подается Uвых10(t3). Таким образом, на выходе первого интегратора получается разность Uвых11(t3)=Uвых9(t2)-Uвых10(t3), которая является выделенной во втором интервале ошибкой интегрирования интегратора с обратным знаком. Подавая Uвых9(t3)=Uвых9(t2) и Uвых11(t3) на входы второго сумматора (12), начиная с момента времени t3 получим напряжение Uвых(t) - точное значение интеграла функции входного напряжения Uвых(t) за период τ (показано пунктирной линией).

Аналогичным образом устройство будет функционировать при других формах входных сигналов.

Применение компенсации ошибок интегрирования в способе и устройстве двухтактного интегрирования не требует юстировки интеграторов, проведения дополнительных процедур и схем для измерения паразитных составляющих интегрирования, позволяет полностью скомпенсировать влияние напряжений сдвига и токов смещения, что выгодно отличает предлагаемое техническое решение от прототипов.

Предлагаемые технические решения являются новыми, поскольку из общедоступных сведений не известны предлагаемые способ и устройство интервального интегрирования.

Предлагаемые технические решения имеют изобретательский уровень, поскольку из опубликованных научных данных и известных технических решений явным образом не следует, что заявленная последовательность операций способа и построение устройства приводят к повышению точности способа и устройства интегрирования.

Предлагаемые технические решения промышленно применимы, так как основаны на схемотехнических решениях и элементной базе, широко применяющихся в аналоговых и цифровых устройствах.

1. Способ двухтактного интегрирования, отличающийся тем, что в процессе интегрирования на входе интегратора за два равных временных интервала формируется сигнал, значение напряжения которого равно входному напряжению на первом временном интервале и нулю на втором, выходной сигнал находится как сумма двух составляющих, первая составляющая получается интегрированием интегратором входного сигнала на первом интервале, вторая - как разность первой составляющей и напряжения полученного интегрированием интегратором входного сигнала за весь период интегрирования, вторая составляющая в конце второго интервала равна ошибке интегрирования входного тока смещения и напряжения сдвига на первом временном интервале с обратным знаком, суммирование двух составляющих приводит к полной компенсации накопленной ошибки в конце второго интервала.

2. Устройство двухтактного интегрирования, отличающееся тем, что содержит интегратор, коммутатор, два замыкающих ключа, два блока аналоговой памяти, первый сумматор, второй сумматор, информационный вход устройства подключен к первому контакту коммутатора, второй контакт коммутатора подключен к нулевому потенциалу, информационный вход интегратора подключен к третьему контакту коммутатора, замкнутому при отсутствии управляющего сигнала на управляющем входе коммутатора на землю и подключающему вход интегратора к информационному входу устройства при наличии управляющего сигнала, первый управляющий вход устройства подключен к управляющему контакту коммутатора и к управляющему контакту первого замыкающего ключа, второй управляющий вход устройства подключен к управляющему контакту второго замыкающего ключа, вход обнуления подключен к входу сброса интегратора, выход интегратора подключен к входным контактам первого и второго замыкающих ключей, выход первого замыкающего ключа подключен к входу первого блока аналоговой памяти, выход второго замыкающего ключа подключен к входу второго блока аналоговой памяти, выход первого блока аналоговой памяти подключен к первому входу сумматоров и к первому входу второго сумматора, выход второго блока аналоговой памяти подключен к инверсному входу первого сумматора, выход первого сумматора подключен к второму входу второго сумматора, выход второго сумматора подключен к выходу устройства.