Бортовой спецвычислитель

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники, в частности к устройствам, выполняющим операцию быстрого преобразования Хартли массива действительных чисел, и может быть использовано в системах и устройствах цифровой обработки сигналов. Технический результат заключается в повышении помехоустойчивости. Бортовой спецвычислитель содержит процессор, четыре АЦП, ОЗУ, двухпортовое ОЗУ, контроллер мультиплексного канала, два приемопередатчика мультиплексного канала, ПЗУ, системный контроллер, четыре приемопередатчика RS-485 и узел сброса. 6 з.п. ф-лы, 35 ил.

Реферат

Изобретение относится к области вычислительной техники, в частности к устройствам, выполняющим операцию быстрого преобразования Хартли (БПХ) массива действительных чисел. Изобретение может быть использовано в системах и устройствах цифровой обработки сигналов.

Известно устройство для быстрого действительного преобразования Хартли - Фурье [1].

Недостатком устройства является сложность аппаратной реализации недостаточное быстродействие из-за временных затрат на проведение операции двоично-инверсной перестановки входной информации.

Наиболее близким по технической сущности к изобретению является устройство цифровой обработки радиолокационных сигналов на основе процессора Л1879 ВМ1 [2], содержащее первый процессор DSP, второй процессор DSP, третий процессор DSP, четвертый процессор DSP, первое локальное ОЗУ, второе локальное ОЗУ, третье локальное ОЗУ, четвертое локальное ОЗУ, первое разделяемое ОЗУ, второе разделяемое ОЗУ, генератор, а ячейка контроллера мультиплексного канала состоит из процессора DSP, локальное ОЗУ, первый контроллер мультиплексного канала, второй контроллер мультиплексного канала, третий контроллер мультиплексного канала, четвертый контроллер мультиплексного канала, генератор, первый усилитель, второй усилитель, третий усилитель, четвертый усилитель, первый трансформатор, второй трансформатор, третий трансформатор, четвертый трансформатор.

Описанное устройство как наиболее близкое к предлагаемому принято за прототип и представлено на фиг.11.

Недостатком устройства является сложность аппаратной реализации, высокий уровень шума.

Задачей изобретения является сокращение аппаратуры, снижение уровня шума и расширение функциональных возможностей.

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.1…фиг.10, фиг.12…фиг.23, где:

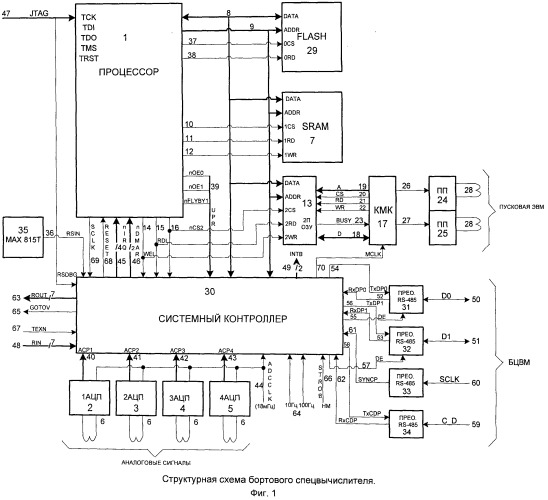

- на фиг.1 представлена структурная схема бортового спецвычислителя;

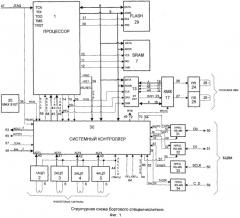

- на фиг.2 представлена функциональная схема системного контроллера;

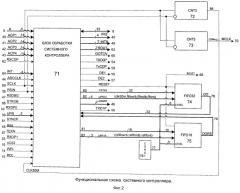

- на фиг.3 представлена функциональная схема блока обработки системного контроллера;

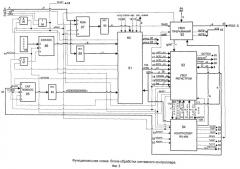

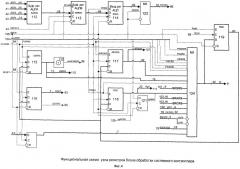

- на фиг.4 представлена функциональная схема узла регистров блока обработки системного контроллера;

- на фиг.5 представлена функциональная схема узла прерываний;

- на фиг.6 представлена функциональная схема контроллера RS-485;

- на фиг.7 представлена функциональная схема узла регистров RS-485;

- на фиг.8, 8а, 8б, 8в, 8г представлен алгоритм работы МС блока обработки системного контроллера;

- на фиг.9, 9а, 9б представлен алгоритм работы узла прерываний;

- на фиг.10, 10а, 10б, 10в, 10г, 10д, 10е представлен алгоритм работы МС контроллера RS-485;

- на фиг.12а представлено расположение отсчетов во времени относительно импульса MM (STROB) 66 в полуактивном режиме;

- на фиг.12б представлено расположение отсчетов во времени относительно импульса НМ (STROB) 66 в активном режиме;

- на фиг.13 представлена адресация и назначение программируемых регистров;

- на фиг.14 представлена запись в асинхронную память с n дополнительными тактами ожидания;

- на фиг.15 представлено назначение разрядов регистра управления и состояния RgU;

- на фиг.16 представлено чтение асинхронной памяти с n дополнительными тактами ожидания;

- на фиг.17 представлен порядок передачи команд;

- на фиг.18 представлены допустимые команды;

- на фиг.19 представлен формат команды;

- на фиг.20 представлен формат слова данных;

- на фиг.21 представлена кодировка ответного слова;

- на фиг.22 представлено измерение угла а направления на цель;

- на фиг.23 представлена векторная диаграмма напряжений.

Указанные преимущества заявляемого устройства перед прототипом достигаются за счет того, что в бортовой спецвычислитель (БСВ), содержащий процессор 1, первый 2, второй 3, третий 4 и четвертый 5 АЦП, соединенные с первым, вторым, третьим и четвертым трансформаторными входами 6, ОЗУ 7, соединенное с процессором 1 шиной данных 8, адресной шиной 9 и первым 10, вторым 11 и третьим 12 управляющими сигналами, двухпортовое ОЗУ 13, соединенное с процессором 1 шиной данных 8, адресной шиной 9 и четвертым 14, пятым 15 и шестым 16 управляющими сигналами, контроллер мультиплексного канала 17, соединенный с двухпортовым ОЗУ 13 шиной данных 18, адресной шиной 19 и первым 20, вторым 21, третьим 22 и четвертым 23 управляющими сигналами, первый 24 и второй 25 приемопередатчики мультиплексого канала, соединенные с выходами 26, 27 контроллера мультиплексого канала17 и с пятым и шестым трансформаторными входами 28, дополнительно введены ПЗУ 29, системный контроллер 30, первый 31, второй 32, третий 33 и четвертый 34 приемопередатчики RS-485 и узел сброса 35, выход 36 которого соединен с первым входом системного контроллера 30, шина данных 8 которого соединена с шиной данных процессора 1 и ПЗУ 29, адресная шина 9 которого соединена с адресной шиной процессора 1 и системного контроллера 30, второй, третий и четвертый входы которого соединены с четвертым 14, пятым 15 и шестым 16 управляющими сигналами процессора 1, первый 37 и второй 38 выходы которого соединены с первым и вторым входами ПЗУ 29, причем первая 39 группа выходов процессора 1 соединена с первой группой входов системного контроллера 30, вторая 40, третья 41, четвертая 42 и пятая 43 группы входов которого соединены с первым 2, вторым 3, третьим 4 и четвертым 5 АЦП, первые входы которых соединены с первым 44 входом бортового спецвычислителя и пятым входом системного контроллера 30, первая 45 и вторая 46 группы выходов которого соединены с первой и второй группами входов процессора 1, третья 47 группа входов процессора 1 и шестой вход системного контроллера 30 являются первой группой входов бортового спецвычислителя, вторая 48 группа входов которого соединена с шестой группой входов системного контроллера 30, третья группа выходов которого является первой 49 группой выходов бортового спецвычислителя, первый 50 и второй 51 двунаправленные входы-выходы которого соединены с первым 31 и вторым 32 приемопередатчиками RS-485, выходы 52,53 которых соединены с седьмым и восьмым входами системного контроллера 30, первый 54 и второй 55 выходы которого соединены с первым и вторым входами первого 31 приемопередатчика RS-485, первый и второй входы второго 32 приемопередатчика RS-485 соединены с третьим 56 и четвертым 57 выходами системного контроллера 30, пятый 58 выход которого соединен с первым входом четвертого 34 приемопередатчика RS-485, второй вход которого соединен со вторым 59 входом бортового спецвычислителя, третий 60 вход которого соединен со входом третьего 33 приемопередатчика RS-485, выход 61 которого соединен с девятым входом системного контроллера 30, десятый вход которого соединен с выходом 62 четвертого 34 приемопередатчика RS-485, причем четвертая 63 группа выходов системного контроллера 30 соединена со второй группой выходов бортового спецвычислителя, третья 64 группа входов которого соединена с седьмой группой входов системного контроллера 30, шестой 65 выход которого соединен с первым выходом бортового спецвычислителя, четвертый 66 вход которого соединен с одиннадцатым входом системного контроллера 30, двенадцатый вход которого соединен с пятым 67 входом бортового спецвычислителя, причем седьмой 68 выход системного контроллера 30 соединен с первым входом процессора 1, третий выход 69 которого соединен с тринадцатым входом системного контроллера 30, восьмой 70 выход которого соединен со вторым входом контроллера мультиплексного канала 17.

Системный контроллер 30 состоит из блока обработки системного контроллера 71, первого 72 счетчика, второго 73 счетчика, первого 74 FIFO, второго 75 FIFO, константы 76, группа выходов 77 которой соединена с первыми группами входов первого 74 и второго 75 FIFO, группы выходов 78,79 которых соединены с первой и второй группами входов блока обработки системного контроллера 71, первая 80 и вторая 81 группы выходов которого соединены со вторыми группами входов первого 74 и второго 75 FIFO, третьи 82,83 группы входов которых соединены с третьей и четвертой группами выходов блока обработки системного контроллера 71, первый выход которого соединен с первыми входами первого 74 и второго 75 FIFO и является седьмым 68 выходом системного контроллера 30, шина данных 8 которого соединена с шиной данных блока обработки системного контроллера 71, адресная шина которого является адресной шиной 9 системного контроллера 30, первая 45, вторая 46, третья 49 и четвертая 63 группы выходов которого соединены с пятой, шестой, седьмой и восьмой группами выходов блока обработки системного контроллера 71, второй, третий, четвертый, пятый, шестой и седьмой выходы которого соединены с первым 54, вторым 55, третьим 56, четвертым 57, пятым 58 и шестым 65 выходами системного контроллера 30, первая 39, вторая 40, третья 41, четвертая 42, пятая 43, шестая 48 и седьмая 64 группы входов которого соединены с третьей, четвертой, пятой, шестой, седьмой, восьмой и девятой группами входов блока обработки системного контроллера 71, первый вход которого является первым 36 входом системного контроллера 30 и соединен с инверсными входами первого 72 и второго 73 счетчика, прямые входы которых соединены со вторым входом блока обработки системного контроллера 71 и тринадцатым 69 входом системного контроллера 30, второй 14, третий 15, четвертый 16, пятый 44, шестой 47, седьмой 52, восьмой 53, девятый 61, десятый 62, одиннадцатый 66 и двенадцатый 67 входы которого соединены с третьим, четвертым, пятым, одиннадцатым, шестым, седьмым, восьмым, девятым, десятым, двенадцатым и тринадцатым входами блока обработки системного контроллера 71, причем выход 84 первого 72 счетчика соединен с четырнадцатым входом блока обработки системного контроллер 71, а выход второго 73 счетчика соединен с восьмым 70 выходом системного контроллера 30.

Блок обработки системного контроллера 71 состоит из первого 85 и второго 86 счетчиков, регистра 87, первого 88, второго 89 и третьего 90 дешифраторов, машины состояния 91 (МС), узла прерываний 92, узла регистров 93, контроллера RS-485 94, константы 95, первого 96 и второго 97 элементов И, элемента ИЛИ 98, выход которого соединен с первыми входами первого 96 элемента И, узла регистров 93, контроллера RS-485 94 и является первым 68 выходом блока обработки системного контроллера 71, второй 54, третий 55, четвертый 56, пятый 57 и шестой 58 выходы которого соединены с первым, вторым, третьим, четвертым и пятым выходами контроллера RS-485 94, шина данных 8 которого соединена с шиной данных узла регистров 93 и является шиной данных 8 блока обработки системного контроллера 71, адресная шина 9 которого соединена с адресной шиной регистра 87 и второго 89 дешифратора, группа выходов которого соединена с первой группой входов МС 91, вторая группа входов которого и первый вход узла прерываний 92 соединены с группой выходов третьего 90 дешифратора, группа входов которого соединена с группой выходов регистра 87, тактовый вход 69 которого соединен со вторыми входами узла регистров 93 и блока обработки системного контроллера 71, первый 36 вход которого соединен с первым входом элемента ИЛИ 98, второй вход которого соединен с шестым 47 входом блока обработки системного контроллера 71, седьмой 65 выход которого соединен с первым выходом узла регистров 93, второй 99 выход которого соединен со вторым входом контроллера RS-485 94, шестой выход которого является первым сигналом пятой 45 группы выходов блока обработки системного контроллера 71, остальные сигналы соединены с первой группой выходов узла прерываний 92, вторая 100 группа выходов которого соединена с первой группой входов узла регистров 93, первая группа выходов которого является первой 80 группой выходов блока обработки системного контроллера 71, вторая 81 группа выходов которого соединена с первой группой выходов контроллера RS-485 94, вторая 101, третья 102, четвертая 103 группы выходов которого соединены со второй, третьей и четвертой группами входов узла регистров 93, вторая группа выходов которого является восьмой 63 группой выходов блока обработки системного контроллера 71, третья 82 и четвертая 83 группы выходов которого соединены с первой и второй группами выходов МС 91, третья группа выходов которой является шестой 46 группой выходов блока обработки системного контроллера 71, седьмая 49 группа выходов которого соединена с первым и вторым выходами узла прерываний 92, первая группа входов которого является девятой 64 группой входов блока обработки системного контроллера 71, первая 78 и вторая 79 группы входов которого соединены с пятой и шестой группами входов узла регистров 93, седьмая группа входов которого соединена с первой группой входов контроллера RS-485 94, третьей группой входов МС 91 и является третьей 39 группой входов блока обработки системного контроллера 71, четвертая 40, пятая 41, шестая 42 и седьмая 43 группы входов которого соединены с восьмой, девятой, десятой и одиннадцатой группами входов узла регистров 93, двенадцатая 104 группа входов которого соединена с четвертой группой выходов МС 91, четвертая группа входов которой соединена с группой выходов 105 второго счетчика 86, группа входов которого соединена с группой выходов константы 95, причем тактовый вход второго 86 счетчика соединен с четвертым входом блока регистров 93 и с одиннадцатым 44 входом блока обработки системного контроллера 71, третий 14, четвертый 15 и пятый 16 входы которого соединены с первым, вторыми третьим входами МС 91, первый выход которой соединен с инверсным входом первого 96 элемента И, выход 106 которого соединен со вторым входом узла прерываний 92, со сбросовыми входами регистра 87 и первого 85 счетчика, с третьими входами контроллера RS-485 94 и узла регистров 93 и инверсным входом второго 97 элемента И, выход которого соединен со сбросовым входом второго 86 счетчика, причем восьмая 48 группа входов блока обработки системного контроллера 71 соединена с тринадцатой группой входов узла регистров 93, третья 107 группа выходов которого соединена с группой входов первого 85 счетчика, группа выходов которого соединена с группой входов первого 88 дешифратора, группа выходов которого соединена с пятой группой входов МС 91, второй и третий выходы которой соединены с разрешающим входом регистра 87 и с прямым входом второго 97 элемента И, четвертый и пятый выходы МС 91 соединены с разрешающим и установочным входами первого 85 счетчика, тактовый вход которого соединен с пятым, третьим и четвертым входами узла регистров 93, узла прерываний 92 и контроллера RS-485 94 соответственно и является четырнадцатым 84 входом блока обработки системного контроллера 71, двенадцатый 66 вход которого соединен с четвертым входом МС 91, шестой 108 выход которой соединен с четвертым входом узла прерываний 92, шестой вход узла регистров 93 соединен с седьмым 109 выходом контроллера RS-485 94, пятый, шестой и седьмой входы которого соединены с девятым 61, седьмым 52и восьмым 53 входами блока обработки системного контроллер71, причем четвертая 110 и пятая 111 группы выходов узла регистров 93 соединены со второй и третьей группами входов контроллера RS-485 94 и второй группой входов узла прерываний 92 соответственно.

Узел регистров блока обработки системного контроллера 93 состоит из первого 112 регистра, второго 113 регистра, третьего 114 регистра, четвертого 115 регистра, пятого 116 регистра, шестого 117 регистра, седьмого 118 регистра, восьмого 119 регистра, первой 120 группы триггеров, второго 121 триггера, группы элементов исключающее ИЛИ 122, первого 123 мультиплексора, второго 124 мультиплексора, группа выходов которого соединена с информационной группой входов восьмого 119 регистра и является шиной данных 8 узла регистров блока обработки системного контроллера 93, первая 80 группа выходов которого соединена с группой выходов первого 123 мультиплексора, группа входов которого соединена с группой выходов третьего 114 регистра, информационная группа входов которого соединена с группой выходов второго 113 регистра, информационная группа входов которого соединена с группой выходов первого 112 регистра, первая, вторая, третья и четвертая группы входов которого являются восьмой 40, девятой 41, десятой 42 и одиннадцатой 43 группами входов узла регистров блока обработки системного контроллера 93, вторая 63 группа выходов которого соединена с группой выходов пятого 116 регистра, выход которого является первым 65 выходом узла регистров блока обработки системного контроллера 93, третья 107 группа выходов которого соединена с первой группой входов второго 124 мультиплексора и группой выходов шестого 117 регистра, информационная группа входов которого соединена с информационными группами входов четвертого 115, пятого 116, седьмого 118 регистров и группой выходов восьмого 119 регистра, тактовый вход которого является вторым 69 входом узла регистров блока обработки системного контроллера 93, четвертая 110 группа выходов которого соединена со второй группой входов второго 124 мультиплексора, группой входов группы элементов исключающее ИЛИ 122 и группой выходов четвертого 115 регистра, тактовый вход которого является пятым 84 входом узла регистров блока обработки системного контроллера 93 и соединен с тактовыми входами третьего 114, пятого 116, шестого 117 и седьмого 118 регистров, первой 120 группы триггеров и второго 121 триггера, информационный вход которого является первым сигналом двенадцатой 104 группы входов, второй, третий, четвертый, пятый и шестой сигналы которой соединены с первым, вторым, третьим, четвертым и пятым входами второго 124 мультиплексора, седьмой вход которого соединен с разрешающим входом шестого 117 регистра и седьмым сигналом двенадцатой 104 группы входов узла регистров блока обработки системного контроллера 93, тринадцатый и четырнадцатый сигналы двенадцатой 104 группы входов которого соединены с разрешающим входом пятого 116 регистра и с разрешающим входом четвертого 115 регистра и восьмым входом второго 124 мультиплексора, девятый вход которого соединен с разрешающим входом седьмого 118 регистра и пятнадцатым сигналом двенадцатой 104 группы входов узла регистров блока обработки системного контроллера 93, шестнадцатый и семнадцатый сигналы двенадцатой 104 группы входов которого соединены с разрешающими входами третьего 114 и второго 113 регистров, тактовый вход которого является четвертым 44 входом узла регистров блока обработки системного контроллера 93, пятая 111 группа выходов состоит из группы выходов седьмого 118 регистра, выхода второго 121 триггера и шестого 109 входа узла регистров блока обработки системного контроллера 93 и соединена с третьей группой входов второго 124 мультиплексора, четвертая группа входов которого является второй 101 группой входов узла регистров блока обработки системного контроллера 93, второй 99 выход которого соединен с выходом группы элементов исключающее ИЛИ 122, причем первая 100, третья 102, четвертая 103, пятая 78 и шестая 79 группы входов узла регистров блока обработки системного контроллера 93 соединены с пятой, шестой, седьмой, восьмой и девятой группами входов второго 124 мультиплексора, первый и второй инверсные входы которого являются седьмой 39 группой входов узла регистров блока обработки системного контроллера 93, тринадцатая 48 группа входов которого соединена с первой 120 группой триггеров, группа выходов которой соединена с десятой группой входов второго 124 мультиплексора, причем первый 68 вход узла регистров блока обработки системного контроллера 93 соединен с инверсным входом четвертого 115 регистра, третий 106 вход узла регистров блока обработки системного контроллера 93 соединен с инверсными входами второго 113, третьего 114, пятого 116, шестого 117, седьмого 118 и восьмого 119 регистров, первой 120 группы триггеров и второго 121 триггера, восемнадцатый сигнал двенадцатой 104 группы входов соединен с прямым и инверсным входами первого 123 мультиплексора, девятнадцатый сигнал двенадцатой 104 группы входов соединен с разрешающим входом восьмого 119 регистра.

Узел прерываний 92 блока обработки системного контроллера 71 состоит первого 125 счетчика, второго 126 счетчика, третьего 127 счетчика, четвертого 128 счетчика, первого 129 дешифратора, второго 130 дешифратора, третьего 131 дешифратора, четвертого 132 дешифратора, формирователя сдвигов и одиночных импульсов 133, первого 134 триггера, второго 135 триггера, третьего 136 триггера, четвертого 137 триггера, пятого 138 триггера, шестого 139 триггера, седьмого 140 триггера, восьмого 141 триггера, девятого 142 триггера, десятого 143 триггера, одиннадцатого 144 триггера, двенадцатого 145 триггера, первого 146 элемента И, второго 147 элемента И, третьего 148 элемента И, четвертого 149 элемента И, элемента 150 ИЛИ, инверсный выход которого является третьим сигналом первой 45 группы выходов узла прерываний 92, первый и второй сигналы которой соединены с инверсными выходами десятого 143 и восьмого 141 триггеров, прямой выход которого является вторым сигналом второй 100 группы выходов узла прерываний 92, первый, третий и четвертый сигналы которой соединены с выходами шестого 139, десятого 143 и двенадцатого 145 триггеров соответственно, тактовые входы которых соединены с тактовыми входами первого 134, второго 135, третьего 136, четвертого 137, пятого 138, седьмого 140, восьмого 141, девятого 142 и одиннадцатого 144 триггеров, первого 125, второго 126, третьего 127 и четвертого 128 счетчиков и являются третьим 84 входом узла прерываний 92, первый выход INTB1 49-1 которого соединен с информационным входом третьего 127 счетчика и выходом четвертого 137 триггера, информационный вход которого соединен с первым выходом формирователя сдвигов и одиночных импульсов 133, второй выход которого соединен с информационным входом третьего 136 триггера, выход которого является первым сигналом первой группы входов формирователя сдвигов и одиночных импульсов 133, второй, третий и четвертый сигналы которой соединены с выходами седьмого 140, девятого 142 и одиннадцатого 144 триггеров, информационные входы которых являются вторым, четвертым и шестым сигналами группы выходов формирователя сдвигов и одиночных импульсов133, а информационные входы шестого 139, восьмого 141, десятого 143 и двенадцатого 145 триггеров являются первым, третьим, пятым и седьмым сигналами группы выходов формирователя сдвигов и одиночных импульсов 133 соответственно, третий выход которого соединен с информационным входом пятого 138 триггера, выход которого соединен с информационным входом четвертого 128 счетчика и является вторым INTB2 49-2 выходом узла прерываний 92, первая 64 группа входов которого соединена с информационным входом первого 125 счетчика и первым инверсным входом первого 146 элемента И и с информационным входом второго 126 счетчика и первым инверсным входом второго 147 элемента И, выход которого соединен со сбросовым входом второго 126 счетчика, группа выходов которого соединена с группой входов второго 130 дешифратора, выход которого соединен с информационным входом второго 135 триггера, выход которого соединен с первым входом формирователя сдвигов и одиночных импульсов 133, второй вход которого соединен с выходом первого 134 триггера, информационный вход которого соединен с выходом первого 129 дешифратора, группа входов которого соединена с группой выходов первого 125 счетчика, сбросовый вход которого соединен с выходом первого 146 элемента И, второй вход которого соединен со вторыми входами второго 147, третьего 148 и четвертого 149 элементов И, со сбросовыми входами первого 134, второго 135, третьего 136, шестого 139, седьмого 140, восьмого 141, девятого 142, десятого 143, одиннадцатого 144, двенадцатого 145 триггеров и является вторым 106 входом узла прерываний 92, первый SA(0) и четвертый 108 входы которого соединены с третьим и четвертым входами формирователя сдвигов и одиночных импульсов 133, причем группа выходов третьего 127 счетчика соединена с группой входов третьего 131 дешифратора, выход которого соединен с первым входом третьего 148 элемента И, выход которого соединен со сбросовыми входами третьего 127 счетчика и четвертого 137 триггера, группа выходов четвертого 128 счетчика соединена с группой входов четвертого 132 дешифратора, выход которого соединен с первым входом четвертого 149 элемента И, выход которого соединен со сбросовыми входами четвертого 128 счетчика и пятого 138 триггера, причем вторая группа входов формирователя сдвигов и одиночных импульсов 133 соединена со второй 111 группой входов узла прерываний 92, причем выходы шестого 139 и двенадцатого 145 триггеров соединены с первым и вторым входами элемента ИЛИ 150.

Контроллер RS-485 94 состоит из первого 151 счетчика, второго 152 счетчика, третьего 153 счетчика, четвертого 154 счетчика, первого 155 мультиплексора, второго 156 мультиплексора, третьего 157 мультиплексора, узла регистров 158 RS-485, MCRS 159, первой 160 константы, второй 161 константы, первого 162 триггера, второго 163 триггера, третьего 164 триггера, четвертого 165 триггера и дешифратора 166, первый выход которого соединен с установочным и сбросовым входами четвертого 165 триггера, выход 169 которого соединен с первыми входами узла регистров 158 RS-485 и MCRS 159, первый выход которой соединен с информационным входом первого 162 триггера, инверсный и прямой выходы которого соединены с шестым 58 и седьмым 109 выходами контроллера RS-485 94, первый 54 и третий 56 выходы которого соединены с первым и вторым выходами узла регистров 158 RS-485, второй вход которого соединен с выходом второго 163 триггера, вторым 55 и четвертым 57 выходами контроллера RS-485 94, пятый 57 выход которого соединен с «корпусом», первая 81, вторая 101, третья 102 и четвертая 103 группы выходов контроллера RS-485 94 соединены с первой, второй, третьей и четвертой группами входов узла регистров 158 RS-485, пятая 167 группа выходов которого соединена с первыми группами входов первого 155 и второго 156 мультиплексоров и машиной состояний MCRS 159, второй выход которой соединен со сбросовым входом первого 162 триггера, тактовый вход которого соединен с третьим входом узла регистров 158 RS-485 и является четвертым 84 входом контроллера RS-485 94, шина данных 8 которого соединена с первой группой входов узла регистров 158 RS-485, вторая группа входов которого соединена с первой 39 группой входов контроллера RS-485 94, вторая 110 группа входов которого соединена с третьей группой входов узла регистров 158 RS-485, четвертая группа входов которого соединена с первой 168 группой выходов машины состояний MCRS 159, вторая группа входов которой соединена с группой выходов первого 151 счетчика, тактовый вход которого соединен с тактовыми входами второго 152, третьего 153 и четвертого 154 счетчиков, второго 163 триггера, с четвертым входом узла регистров 158 RS-485 и является пятым 61 входом контроллера RS-485 94, первый 68 вход которого соединен с пятым входом узла регистров 158 RS-485, со сбросовыми входами первого 151 и четвертого 154 счетчиков и второго 163 триггера, с установочными входами второго 152 и третьего 153 счетчиков, группа выходов которого соединена с третьей группой входов машины состояний MCRS 159, третий и четвертый выходы которой соединены с информационным входом второго 163 триггера и установочным входом четвертого 154 счетчика, группа выходов которого соединена с группой входов дешифратора 166, второй выход которого соединен с установочным и инверсным сбросовым входами третьего 164 триггера, выход которого соединен с третьим входом машины состояний MCRS 159, причем третья 111 группа входов контроллера RS-485 94 соединена с четвертой группой входов машины состояний MCRS 159, пятый и шестой выходы которой соединены с первым и вторым входами третьего 157 мультиплексора, группа выходов которого соединена с информационной группой четвертого 154 счетчика, разрешающий вход которого соединен с седьмым выходом машины состояний MCRS 159, восьмой выход которой соединен с инверсным разрешающим входом первого 151 счетчика, девятый и десятый выходы машины состояний MCRS 159 соединены с первым и вторым входами второго 156 мультиплексора, группа выходов которого соединена с информационной группой третьего 153 счетчика, инверсный разрешающий вход которого соединен с одиннадцатым выходом машины состояний MCRS 159, двенадцатый выход которой соединен с инверсным разрешающим входом второго 152 счетчика и первым входом первого 155 мультиплексора, группа выходов которого соединена с информационной группой входов второго 152 счетчика, выход которого соединен со вторым входом машины состояний MCRS 159, тринадцатый выход которой соединен со вторым входом первого 155 мультиплексора, вторая группа входов которого соединена с группой выходов первой 160 константы и со второй группой входов второго 156 мультиплексора, причем первая и вторая группы выходов второй 161 константы соединены с первой и второй группами входов третьего 157 мультиплексора, второй 99 и третий 106 входы контроллера RS-485 94 соединены с шестым и седьмым входами узла регистров 158 RS-485, восьмой и девятый входы которого соединены с шестым 52 и седьмым 53 входами контроллера RS-485 94.

Узел регистров 158 RS-485 состоит из первого 170 регистра, второго 171 регистра, третьего 172 регистра, четвертого 173 регистра, пятого 174 регистра, шестого 175 регистра, седьмого 176 регистра, первого 177 сдвигового регистра, второго 178 сдвигового регистра, третьего 179 сдвигового регистра, четвертого 180 сдвигового регистра, первого 181 мультиплексора, второго 182 мультиплексора, первой 183 группы элементов исключающее ИЛИ, второй 184 группы элементов исключающее ИЛИ, третьей 185 группы элементов исключающее ИЛИ, четвертой 186 группы элементов исключающее ИЛИ, сумматора 187, элемента И 188, выход которого соединен со сбросовым входом первого 170 регистра, информационная группа входов которого соединена с первой 8 группой входов узла регистров 158 RS-485, первая 81 группа выходов которого соединена с группой выходов четвертого 173 регистра, информационная группа входов которого соединена с информационными группами входов второго 171 и седьмого 176 регистров и выходами первого 177 и второго 178 сдвиговых регистров и является пятой 167 группой выходов узла регистров 158 RS-485, вторая 101 группа выходов которого соединена с группой выходов шестого 175 регистра, информационная группа входов которого соединена с группой выходов сумматора 187, первая группа входов которого соединена с группой выходов пятого 174 регистра, информационная группа входов которого является четвертой 103 группой выходов узла регистров 158 RS-485 и соединена с группой выходов второго 171 регистра, информационной группой входов третьего 172 регистра и группой входов второй 184 группы элементов исключающее ИЛИ, выход которой соединен с первым инверсным входом второго 182 мультиплексора, группа выходов которого соединена с информационными группами входов третьего 179 и четвертого 180 сдвиговых регистров, выходы которых являются первым 54 и вторым 56 выходами узла регистров 158 RS-485, третья 102 группа выходов которого соединена с группой выходов седьмого 176 регистра, первой группой входов второго 182 мультиплексора и группой входов четвертой 186 группы элементов исключающее ИЛИ, выход которой соединен со вторым инверсным входом второго 182 мультиплексора, вторая группа входов которого соединена с группой выходов первого 181 мультиплексора, группа входов которого соединена с группой выходов первого 170 регистра и группой входов первой 183 группы элементов исключающее ИЛИ, выход которой соединен с третьим инверсным входом второго 182 мультиплексора, третья группа входов которого соединена с группой выходов третьего 172 регистра и группой входов третьей 185 группы элементов исключающее ИЛИ, выход которой соединен с четвертым инверсным входом второго 182 мультиплексора, четвертая группа входов которого соединена с третьей 110 группой входов узла регистров 158 RS-485, вторая 39 группа входов которого соединена с разрешающим и тактовым входами первого 170 регистра, причем первый сигнал четвертой168 группы входов соединен с разрешающим входом второго 171 регистра, второй сигнал соединен с разрешающим входом третьего 172 регистра, третий сигнал соединен с разрешающими входами первого 177 и второго 178 сдвиговых регистров, четвертый сигнал соединено разрешающим входом четвертого 173 регистра, пятый сигнал соединен с прямым и инверсным входами первого 181 мультиплексора, шестой, седьмой, восьмой и девятый сигналы соединены с первым, вторым, третьим и четвертым входами второго 182 мультиплексора, пятый вход которого соединен со вторым 55 входом узла регистров 158 RS-485, первый 169 вход которого соединен с первым инверсным входом элемента И 188, второй инверсный вход которого соединен со сбросовыми входами пятого 174 и шестого 175 регистров, сумматора 187 и является седьмым 106 входом узла регистров 158 RS-485, третий 84 вход которого соединен с тактовыми входами пятого 174, шестого 175 регистров и сумматора 187, первый вход которого соединен с питанием (3.3в), причем четвертый 61 вход узла регистров 158 RS-485 соединен с тактовыми входами второго171, третьего 172, четвертого 173 и седьмого 176 регистров, первого 177, второго 178, третьего 179 и четвертого 180 сдвиговых регистров, сбросовые входы которых соединены между собой и являются пятым 68 входом узла регистров 158 RS-485, шестой 99 вход которого соединен с пятым инверсным входом второго 182 мультиплексора, причем восьмой 52 и девятый 53 входы узла регистров 158 RS-485 соединены с информационными входами первого 177 и второго 178 сдвиговых регистров.

Бортовой спецвычислитель работает следующим образом.

Специализированная цифровая обработка сигналов (ЦОС) - мощное средство повышения эффективности функционирования современных радиолокационных станций (РЛС). К числу основных преимуществ ЦОС можно отнести получение стабильных характеристик РЛС в широком диапазоне условий эксплуатации; возможности реализации сложных, адаптивных алгоритмов обработки без ущерба для точности и других показателей эффективности; возможность модернизации аппаратуры за счет модификации программного обеспечения (ПО). Переход к программируемым цифровым устройствам принципиально изменил подход при разработке и проектировании специализированной аппаратуры ЦОС. Существенно возросла роль алгоритмов обработки, которые практически полностью определяют эффективность аппаратуры ЦОС.

Цифровой Процессор Обработки Сигналов бортового спецвычислителя спроектирован как однокристальная трехпроцессорная "система на кристалле" на базе IP-ядерной платформы «МУЛЬТИКОР» [3] (далее по тексту Процессор 1).

Процессор 1 сочетает в себе лучшие качества двух классов приборов микроконтроллеров и цифровых процессоров обработки сигналов, что особенно важно для микроминиатюрных встраиваемых применений, когда одновременно приходится решать в рамках ограниченных габаритов задачи управления и высокоточной обработки информации, включая сигналы и изображение.

Архитектура аппаратной части близка к архитектуре универсальной ЭВМ и за счет рационального распределения вычислительных ресурсов и объема памяти ее можно оптимизировать, что не исключает возможности в готовой аппаратуре изменять рабочие программы. Эти свойства позволяют получить гибкую аппаратуру, которая в процессе эксплуатации может быть перестроена под решение различных задач.

Анализ технических параметров доплеровской радиолокационной станции (РЛС) показывает, что базой при обработке радиолокационных сигналов в частотной области является быстрое преобразование Хартли. Быстрое преобразование Хартли оптимальнее в количестве операций и времени их выполнения (20%), чем преобразование Фурье [4].

Структурная схема бортового спецвычислителя представлена на фиг.1.

Бортовой спецвычислитель обеспечивает:

- программное быстрое преобразование Хартли;

- прием четырех аналоговых сигналов 6 на 14-разрядный АЦП (2, 3, 4, 5) с защитой от переполнения разрядной сетки с преобразованием сигналов в цифровой код 40, 41, 42, 43;

- прием и исполнение двух 64-радиальных векторных прерываний:

- первое - 10 Гц;

- второе - 100 Гц (начало работы);

- выдачу двух радиальных прерываний 49 по инициативе программы вычислителя;

- исполнение программ пользователя;

- проведение тестового самоконтроля при начальном включении и по внешней команде с выдачей сигнала GOTOV 65 при положительном результате самоконтроля.

Бортовой спецвычислитель (БСВ) состоит из:

Процессора 1, ПЗУ 29 (4 Мбайта), ОЗУ 7 (4 Мбайта), двухпортового ОЗУ 13 (8-132Кх18бит), мультиплексного канала обмена 17 по ГОСТ 26765.52-87, первого 24 приемопередатчика мультиплексного канал обмена, второго 25 приемопередатчика мультиплексного канал обмена, системного контроллера 30, первого 2 АЦП, второго 3 АЦП, третьего 4 АЦП и четвертого 5 АЦП, первого 31, второго 32, третьего 33 и четвертого 34 приемопередатчика RS-485 и узла сброса 35.

Процессор 1 реализован на основе ядер из библиот