Способ преобразования фазоманипулированного кода в бинарный

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации. Техническим результатом является повышение достоверности. Способ содержит этапы, на которых в каждом такте в области возможного появления информационного перепада формируют временной интервал, в течение которого разрешают запись информации или в первый счетчик импульсов по факту поступления информационного перепада и его изменения из положительной полярности в отрицательную, или во второй счетчик в случае изменения информационного перепада из отрицательной полярности в положительную, в момент окончания временного интервала анализируют состояния счетчиков и, если в первом счетчике записана логическая единица, а во втором - логический ноль, формируют бинарный сигнал положительной полярности, если в первом счетчике записан логический ноль, а во втором - логическая единица, формируют бинарный сигнал отрицательной полярности, в случае записи в любой из счетчиков более одного информационного перепада или отсутствия перепада формируют сигнал об ошибке информационного бита. 10 ил., 1 табл.

Реферат

Предлагаемое изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известны цифровые устройства преобразования фазоманипулированного кода, реализуемые на логических элементах [1] и используемые в бортовых вычислительных системах. В цифровых устройствах анализируются логические уровни информационного бита. Для этого в определенные моменты времени фиксируются логические уровни положительного и отрицательного полутактов фазоманипулированного сигнала. При изменении уровня полутакта из логической единицы в логический ноль формируется декодированный сигнал в бинарном коде в виде логической единицы, а при изменении уровня полутакта из логического нуля в логическую единицу - в виде логического нуля.

Технически анализ логических уровней полутактов фазоманипулированного сигнала осуществляется путем установки в каждом полутакте опорных стробов.

Одним из недостатков устройств цифровой обработки фазоманипулированного кода является повышенная вероятность признания бита ошибочным из-за попадания помехи в любой из стробов, выставляемых во всей области информационного бита. Попадание помехи в информационный бит квалифицируется как ошибка в информационном слове.

Кроме того, в условиях сильных помех существует вероятность попадания помехи противоположной полярности во все стробы полубитов. В этом случае ошибочный бит будет признан за достоверный.

Известен способ (прототип) преобразования сигнала в манчестерском коде [2], основанный на том, что биполярный информационный сигнал интегрируют и сравнивают по амплитуде проинтегрированный информационный сигнал с сигналами заданного уровня положительной и отрицательной полярностей и формируют при этом высокий или низкий уровни выходного бинарного сигнала.

Недостатком способа является ошибочное преобразование информации, поступающей в манчестерском коде, в условиях возможных помех в магистральной линии (электрические и магнитные наводки). Из-за помех в линии проинтегрированный информационный сигнал может не достигнуть порогового уровня, и в этом случае декодированный сигнал в бинарном коде будет ошибочным. Кроме того, недостатком способа является сложность реализации на логических элементах.

Результаты моделирования схемы, реализующей известный способ (фиг.1), подтверждают наличие ошибки при декодировании в условиях воздействия помех.

На фиг.1.b показана ситуация, когда на вход модели устройства, реализующего прототип, подается информация 11001 в коде Манчестер 2 с помехой в начале третьего бита. Информация на выходе модели устройства (первые два бита), снимаемая по тактовым импульсам (фиг.1.j) с информационного выхода (фиг.1.k), соответствует принятой. После воздействия помехи происходит неправильное определение третьего бита ("1" вместо передаваемого "0") и четвертого передаваемого бита ("1" вместо передаваемого "0") и потеря пятого бита (отсутствие тактового импульса).

Техническим результатом предполагаемого изобретения является исключение признания декодированного ошибочного бита за достоверный и возможность реализации способа на логических элементах.

Технический результат достигается тем, что в каждом такте в области возможного появления информационного перепада формируют временной интервал, в течение которого разрешают запись информации или в первый счетчик импульсов по факту поступления информационного перепада и его изменения из положительной полярности в отрицательную, или во второй счетчик в случае изменения информационного перепада из отрицательной полярности в положительную, в момент окончания временного интервала анализируют состояния счетчиков и, если в первом счетчике записана логическая единица, а во втором - логический ноль, формируют бинарный сигнал положительной полярности, если в первом счетчике записан логический ноль, а во втором - логическая единица, формируют бинарный сигнал отрицательной полярности, в случае записи в любой из счетчиков более одного информационного перепада или отсутствия перепада формируют сигнал об ошибке информационного бита.

В предлагаемом способе при декодировании бита информации анализируются не уровни сигнала в полубитах, а наличие информационного перепада в бите в области возможного его появления.

Так как область появления информационного перепада фазоманипулированного сигнала в середине бита для используемых приемопередающих устройств всегда можно определить и выделить интервал времени в середине каждого из битов и подсчитать в нем число перепадов. Если прошел один перепад, то в зависимости от его полярности формируют высокий или низкий уровни выходного бинарного сигнала. Отсутствие перепада в течение измерительного интервала или наличие более одного перепада свидетельствует об ошибке в принимаемом сообщении. Вероятность попадания помехи в ограниченную область, где появляется информационный перепад, будет меньше, чем во весь интервал передаваемого информационного бита.

Благодаря этому игнорируются помехи за пределами интервала, что позволяет исключить повторные передачи (не снижать скорость передачи за счет уменьшения числа повторных слов).

На фиг.1 приведена диаграмма работы модели устройства, представленного в прототипе, при наличии помех.

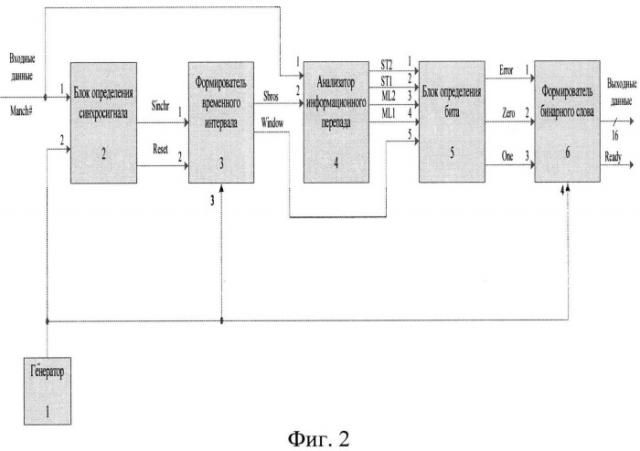

На фиг.2 приведена структурная схема устройства преобразования фазоманипулированного кода в бинарный, реализующая предлагаемый способ и выполненная на логических элементах.

На фиг.3 приведены диаграммы работы блока определения синхросигнала и формирователя временного интервала.

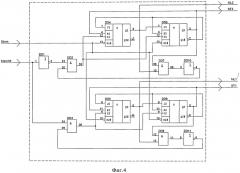

На фиг.4 приведен вариант реализации анализатора информационного перепада.

На фиг.5 и 6 приведены диаграммы работы анализатора информационного перепада.

На фиг.7 приведен вариант реализации блока определения бита.

На фиг.8 приведена диаграмма работы блока определения бита.

На фиг.9, 10 приведены диаграммы работы формирователя бинарного слова.

Способ осуществляется следующим образом.

Структурная схема устройства преобразования фазоманипулированного кода в бинарный, представленная на фиг.2, содержит генератор стабильной частоты 1, блок определения синхросигнала 2, формирователь временного интервала 3, анализатор информационного перепада 4, блок определения бита 5, формирователь бинарного слова 6.

Информационные слова в фазоманипулированном коде поступают на первый вход блока определения синхросигнала 2 и первый вход анализатора информационного перепада 4. Каждое слово начинается с синхросигнала, длительность которого составляет три периода информационного разряда. В первой половине синхросигнала передается уровень логического «0», во второй - уровень логической «1».

В блоке определения синхросигнала 2 осуществляется определение типа синхросигнала поступающего информационного слова и формирование импульсов начала и окончания поступления информационного слова (16 разрядов данных и разряд паритета).

При достоверном определении синхросигнала на выходе блока определения синхросигнала 2 формируются импульс «Sinhr» (фиг.3), который сигнализирует о поступлении первого информационного разряда, и через семнадцать микросекунд импульс «Reset» (фиг.3), который сигнализирует о поступлении разряда контроля четности.

Формирователь временного интервала 3 формирует сигнал «Sbros» определенной длительности, в течение которого возможно появление информационного перепада бита, а также временную зону «Window» длительностью семнадцать микросекунд, в течение которой происходит анализ данных «ST1», «ST2», «ML1», «ML2» с анализатора информационного перепада 4. Работа формирователя временного интервала 3 иллюстрируется диаграммой на фиг.3.

Сигнал «Sbros» является разрешающим для подсчета числа информационных перепадов на анализаторе информационного перепада 4.

Информация с выходов «ST2» и «ML2» анализатора информационного перепада 4 (старший и младший разряды счетчика, реализованного на триггерах DD4, DD6 фиг.4), соответствующая числу перепадов из единицы в ноль, анализируется блоком определения значения бита 5. Информация с выходов «ST1» и «ML1» анализатора информационного перепада 4 (старший и младший разряды счетчика, реализованного на триггерах DD5, DD8 фиг.4), соответствующая числу перепадов из ноля в единицу, также анализируется блоком определения значения бита 5. Работа анализатора информационного перепада 4 иллюстрируется диаграммой на фиг.5, фиг.6.

Блок определения бита 5, вариант реализации которого представлен на фиг.7, предназначен для определения значения и достоверности принятого информационного бита в зависимости от информации на входах «ML1», «ST1», «ML2», «ST2». Результат анализа входной информации представлен в таблице. В результате анализа делается вывод о значении бита или ошибке принимаемого бита. Работа блока определения бинарного бита 5 иллюстрируется диаграммой на фиг.8.

Если на выходе «One» появляется единичный импульс, то это означает, что в принятом бите отсутствует ошибка, и он равен единице.

Если на выходе «Zero» появляется единичный импульс, то это означает, что в принятом бите отсутствует ошибка, и он равен нулю.

Если на выходе «Error» появляется сигнал высокого уровня, то это означает, что в принятом бите ошибка, и в этом случае блокируется выдача информационного слова с формирователя бинарного слова 6.

Формирователь бинарного слова 6 осуществляет преобразование информации, поступающей по линиям «Zero» и «One», в последовательный вид, а затем в двоичный параллельный шестнадцатиразрядный код. Работа формирователя бинарного слова 6 иллюстрируется диаграммами на фиг.9, фиг.10.

При этом в качестве входных информационных слов использовались тестовые сообщения в виде командного слова: 0000100000100001 и слова данных: 1010101111001101.

На фиг.9 показан входной сигнал Manch# и выходной сигнал Ready формирователя бинарного слова 6, сигнализирующий о выдаче принятого слова в виде параллельного шестнадцатиразрядного кода. На фиг.10 луч 1 - сигнал Ready, лучи D0-D15 - выставляемые разряды сообщения с 1-го по 16-й (D0-старший разряд слова, D15 - младший). Выставляемое слово удерживается на выходах формирователя принятого бинарного слова 6 порядка 19 мкс.

Предлагаемый способ реализован в модуле магистрального канала (ММК) ГНДИ. 467754.001, НИИИС.

Литература

1. Преобразователь фазоманипулированного кода в бинарный. - Патент на изобретение RU 2163418 C1, H03M 5/12, 2001.

2. Способ демодуляции сигнала в манчестерском коде. - Патент на изобретение RU 2394368 С2, H03M 5/12, 2006 (прототип).

Способ преобразования фазоманипулированного кода в бинарный, отличающийся тем, что в каждом такте в области возможного появления информационного перепада формируют временной интервал, в течение которого разрешают запись информации или в первый счетчик импульсов по факту поступления информационного перепада и его изменения из положительной полярности в отрицательную, или во второй счетчик в случае изменения информационного перепада из отрицательной полярности в положительную, в момент окончания временного интервала анализируют состояния счетчиков и, если в первом счетчике записана логическая единица, а во втором - логический ноль, формируют бинарный сигнал положительной полярности, если в первом счетчике записан логический ноль, а во втором - логическая единица, формируют бинарный сигнал отрицательной полярности, в случае записи в любой из счетчиков более одного информационного перепада или отсутствия перепада формируют сигнал об ошибке информационного бита.