Устройство защиты выводов микросхемы от электростатических разрядов

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в увеличении реактивного импеданса устройства защиты на высоких частотах. Устройство защиты выводов микросхемы от электростатических разрядов, включающее ключевые n-канальный и р-канальный транзисторы, управляющие n-канальный и р-канальный транзисторы, два нагрузочных резистора, входную шину, шину питания и шину земли, причем в него введены первый и второй дополнительные индукторы, причем сток р-канального ключевого транзистора и исток р-канального управляющего транзистора соединены с первым выводом первого индуктора, второй вывод которого соединен с входной шиной, а также сток n-канального ключевого транзистора и исток n-канального управляющего транзистора соединены с первым выводом второго индуктора, второй вывод которого также соединен с входной шиной. 3 ил.

Реферат

Изобретение относится к области электроники и приборостроения, в частности к устройствам обработки высокочастотных сигналов.

Элементы защиты от электростатических разрядов являются обязательной частью входных и выходных цепей интегральных микросхем. Емкость этих элементов связывает сигнальные выводы с типами питания и заземления, ограничивает частотный диапазон обрабатываемых сигналов.

Близким к заявленному изобретению является известное из уровня техники устройство защиты входов интегральных схем со структурой МДП, содержащее два полевых (ключевых) транзистора, два нагрузочных резистора, два диода, шину питания, общую шину, входную и выходную шины, при этом диоды соединены последовательно и включены между шиной питания и общей шиной, первый резистор включен между входной шиной и общей точкой соединения диодов, исток первого ключевого транзистора подключен к общей шине, его сток - к истоку второго ключевого транзистора и к входной шине, а сток второго транзистора подключен к упомянутой шине питания III.

Основным недостатком данного решения по отношению к заявленному изобретению является то, что в рабочем режиме при положительной или отрицательной полярности стрессового напряжения в нем открывается только один из ключевых транзисторов, вследствие этого необходимо вводить в схему мощные транзисторы большой площади, что в конечном итоге приводит к его значительным топологическим размерам, и большой емкости.

Наиболее близким к заявленному изобретению является известное устройство защиты выводов интегральных схем со структурой МДП от электростатических разрядов /2/.

Основная функция устройства защиты состоит в ограничении напряжения на затворах входных МДП элементов путем переключения разрядного тока из входных и выходных цепей в шину земли. Проблемными являются входные элементы защиты, поскольку они, с одной стороны, должны обеспечивать соответствующий уровень защиты от электростатических разрядов (ЭСР), а с другой, должны иметь минимальное паразитное сопротивление и емкость, чтобы минимизировать падение напряжения на этом элементе и уменьшить дополнительную емкость защищаемого устройства. В момент подачи на вывод устройства разрядного напряжения оба ключевых транзистора открыты, а при нормальном режиме работы (при рабочем напряжении) полезный сигнал, поступающий на вход, проходит в общую интегральную схему (не показана), при этом ключевые транзисторы закрыты, то есть устройство защиты не препятствует передаче полезного сигнала. Интегральная схема наиболее уязвима при подаче отрицательного разрядного напряжения на контактную площадку входной шины, при оборванной шине земли и положительного разрядного напряжения при оборванной шине питания. При положительной полярности напряжения электростатического разряда (до 2000 В) ток поступает на входную шину и далее протекает через ключевой транзистор и далее через элемент защиты цепей питания на шину земли, в то же время управляющий транзистор открывает ключевой транзистор. При отрицательной полярности напряжения электростатического разряда (до -2000 В) ток вытекает через входную шину, протекая через ключевой транзистор и далее через элемент защиты цепей питания на шину земли, в то же время управляющий транзистор открывает ключевой транзистор. Таким образом, при возникновении ЭСР на входной шине как при отрицательной полярности напряжения электростатического разряда, так и при положительной полярности, происходит разделение разрядного тока на две равновеликие составляющие (на одинаковые два плеча) и функционально обеспечивается протекание разрядного тока по двум ключевым транзисторам одновременно, что ведет к уменьшению вдвое сопротивления в цепи разрядного тока или дает возможность вдвое уменьшить размеры транзисторов и емкость устройства защиты.

Результаты исследований показали, что уменьшение площади ключевых транзисторов в 2 раза не приводит к изменению предельно допустимого ЭСР (характеристика стойкости интегральных микросхем к ЭСР), величина которого по прежнему в пределах 2000 В. Однако уменьшить емкость устройства защиты более чем в два раза это решение не позволяет. Схемотехнические средства снижения емкости элементов защиты практически исчерпаны. Емкость элементов защиты не опускается ниже 1пΦ.

Задачей настоящего изобретения является увеличение реактивного импеданса элементов защиты до величины, не влияющей на выходное сопротивление высокочастотного вывода, которое составляет 50 или 75 Ом. То есть до величины не менее 750 Ом.

Для этого устройство защиты выводов микросхемы от электростатических разрядов содержит ключевые n-канальные и р-канальные МДП транзисторы, управляющие n-канальные и р-канальные МДП транзисторы, два одинаковых нагрузочных резистора, включенные между стоками управляющих транзисторов и шинами питания. Причем сток управляющего n-канального транзистора соединен с затвором ключевого р-канального транзистора, а сток управляющего р-канального транзистора соединен с затвором ключевого n-канального транзистора, что обеспечивает включение как n-канального, так и р-канального ключевых транзисторов при любом напряжении разрядного тока.

Увеличение реактивного импеданса устройства защиты на высоких частотах достигается включением двух высокочастотных индукторов в цепи электростатического разряда. Первый индуктор включен между сигнальным выводом микросхемы и объединенными истоком управляющего р-канального и стоком ключевого р-канального транзисторов. Второй индуктор вкючен между сигнальным выводом и объединенными истоком управляющего и стоком ключевого n-канального транзисторов. Индуктор и емкость транзисторов в устройстве защиты образуют последовательный резонансный контур. Причем резонансная частота последовательного контура должна быть меньше нижней границы рабочего диапазона частот и больше верхней границы спектра электростатического разряда. Для модели электростатического разряда от тела человека постоянная времени составляет не менее 150 нс. Это соответствует верхней частоте спектра электростатического разряда около 1 МГц.

В отсутствие индукторов емкость элементов защиты значительно снижает входной импеданс микросхемы. При емкости элементов защиты 1 пФ половина мощности входного сигнала теряется на элементах защиты уже при частоте входного сигнала 2 ГГц. На более высоких частотах схема становится неработоспособной. Введение индуктора в цепь разряда создает последовательный резонансный контур, который проявляет себя как конденсатор на частотах ниже резонансной, и как индуктор - на частотах выше резонансной. Сигнал электростатического разряда имеет спектр частот ниже 1 МГц. И подавляется элементом защиты. Информационный сигнал микросхемы должен быть значительно выше резонансной частоты контура.

Паразитная емкость индуктора определяется его конструкцией и образует с его номинальной индуктивностью параллельный колебательный контур, резонансная частота которого должна быть больше верхней границы рабочего диапазона.

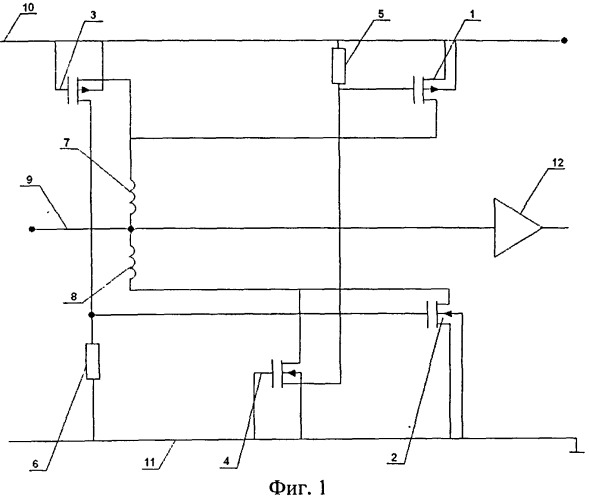

Электрическая схема входного тракта передачи сигнала с раскрытием элементов защиты от электростатического разряда приведена на фиг.1, где:

1 - ключевой (р-канальный) транзистор

2 - ключевой (n-канальный) транзистор

3 - управляющий (р-канальный) транзистор

4 - управляющий (n-канальный) транзистор

5 - нагрузочный резистор

6 - нагрузочный резистор

7 - первый индуктор

8 - второй индуктор

9 - входная шина

10 - шина питания

11 - шина земли

12 - элемент защиты цепей питания.

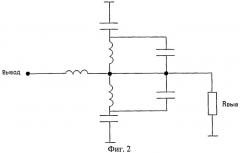

Малосигнальная эквивалентная схема тракта передачи сигнала по выводу микросхемы приведена на фиг.2.

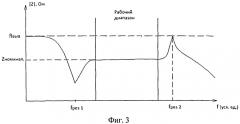

Зависимость входного импеданса от частоты сигнала приведена на фиг.3.

Реактивный импеданс последовательного резонансного контура на частотах выше резонансного имеет индуктивный характер, увеличивается с повышением частоты и слабо влияет на собственный импеданс сигнального вывода микросхемы (фиг.2).

Элемент защиты выводов микросхемы от электростатических разрядов включает два ключевых транзистора, два управляющих транзистора, два нагрузочных резистора, входную шину, шину питания, шину земли и два дополнительных индуктора, в котором сток первого ключевого транзистора 1 и исток первого управляющего транзистора 3 объединены и подключены к первому выводу первого индуктора 7, а также сток второго ключевого транзистора 2 и исток второго управляющего транзистора 4 объединены и подключены к первому выводу второго индуктора 8, второй вывод которого соединен с входной шиной 9. Индуктор 7 образует резонансный контур с последовательно включенной проходной емкостью транзисторов 1 и 3, индуктор 8 образует резонансный контур с проходной емкостью транзисторов 2 и 4, причем собственная резонансная частота индукторов должна быть больше верхней границы частотного диапазона микросхемы, а резонансная частота последовательного контура, образованного индуктором 7 и 8 и проходной емкостью транзисторов 1 и 3 или 2 и 4, должна быть меньше нижней границы частотного диапазона микросхемы. В этом случае реактивный импеданс элементов защиты будет индуктивным и по модулю значительно больше волнового сопротивления вывода микросхемы, а элементы защиты не будут влиять на параметры сигнала.

При появлении на входе электростатического разряда резонансный контур ведет себя как конденсатор, так как спектр разрядного импульса значительно ниже резонансной частоты контура. Все напряжение разряда приложено к транзисторам и устройство защиты работает по известной схеме так, как будто индукторы закорочены проводником.

Например, на частоте работы современных мобильных телефонов 5 ГГц и емкости элемента защиты 1пΦ емкостной импеданс элемента защиты составит 30 Ом. Два элемента защиты снизят его до 15 Ом. При входном импедансе приемника 50 Ом. Входной импеданс вывода составит 11,5 Ом. Полезный ток входного сигнала составит 19% от входного тока. Отсутствие согласования импедансов антенны приемника приводит к неравномерности чувствительности в диапазоне рабочих частот и неустойчивому приему сигнала.

Если включить в каждую цепь защиты от разрядов индуктор с номиналом 5 нГ, то получим два параллельных резонансных контура с резонансной частотой 2,2 ГГц. При этом импеданс индуктора на рабочей частоте составит примерно 160 Ом. Полезный ток входного сигнала увеличится до 62% от входного тока. Импеданс индуктора можно увеличить до 20 нГ при его реализации на кристалле микросхемы без существенного увеличения размеров кристалла. При этом полезная составляющая входного сигнала возрастет до 77%.

Источники информации

1. Авторское свидетельство СССР №1083362.

2. Патент РФ №2308146 - прототип.

Устройство защиты выводов микросхемы от электростатических разрядов, включающее ключевые n-канальный и р-канальный транзисторы, управляющие n-канальный и р-канальный транзисторы, два нагрузочных резистора, входную шину, шину питания и шину земли, отличающееся тем, что в него введены первый и второй дополнительные индукторы, причем сток р-канального ключевого транзистора и исток р-канального управляющего транзистора соединены с первым выводом первого индуктора, второй вывод которого соединен с входной шиной, а также сток n-канального ключевого транзистора и исток n-канального управляющего транзистора соединены с первым выводом второго индуктора, второй вывод которого также соединен с входной шиной.