Передающий каскад в шинном узле шинной сети для выработки соответствующего передаваемому сигналу битового сигнала и способ выработки битового сигнала из передаваемого сигнала

Иллюстрации

Показать всеИзобретение относится к электротехнике, к передающему каскаду в шинном узле шинной сети, прежде всего в шинном узле EIB-сети, который подключен к шинной линии (Bus+, Bus-), для выработки соответствующего передаваемому сигналу, который имеет последовательность передаваемых импульсов, битового сигнала, который для каждого передаваемого импульса состоит из активного импульса, который имеет длительность Δt=t1-t0, причем t0 указывает на начало активного импульса, a t1 - на конец активного импульса, и глубину Ua импульса, и следующего за активным импульсом выравнивающего импульса, со схемой (А) для выработки активного импульса, факультативно, схемой (В) для выработки выравнивающего импульса, и по меньшей мере одной управляющей схемой (С), которая выдает передаваемый сигнал (Usend), по меньшей мере, схеме (А) для выработки активного импульса. Глубина (Ua) импульса активного импульса установлена заданным опорным напряжением (Uref), которое является независимым от величины постоянной составляющей напряжения битового сигнала. Технический результат - возможность замены активных элементов на пассивные компоненты. 2 н. и 4 з. п. ф-лы, 6 ил.

Реферат

Изобретение относится к передающему каскаду в шинном узле шинной сети, прежде всего в шинном узле EIB-сети, который подключен к шинной линии для выработки соответствующего передаваемому сигналу битового сигнала, а также к способу выработки битового сигнала из передаваемого сигнала, причем передаваемый сигнал состоит из последовательности передаваемых импульсов.

Шинные узлы должны, с одной стороны, обеспечивать связь между находящимися в них управляющими блоками, чаще всего микропроцессорами, а с другой стороны, также обеспечивать через шину электропитание этих управляющих блоков и, кроме того, подключенных прикладных схем, таких как реле, датчики, клавиатуры, дисплеи и т.п. Поэтому шинный узел в этом смысле содержит передатчик, приемник и источник питания для внутренних схем и, при необходимости, дополнительно для прикладных схем.

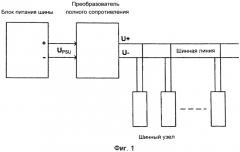

На фиг.1 показана конфигурация шины с несколькими шинными узлами. Для электропитания содержатся один или несколько сетевых блоков питания, выходное сопротивление которых, впрочем, должно быть повышено для того, чтобы воспрепятствовать тому, что частота передачи связи по шине будет демпфирована сетевым блоком питания, в худшем случае до полного погашения. Для этого используются промежуточно включенные преобразователи полного сопротивления, которые, предпочтительно, выполнены в виде дроссельных модулей.

Требования к передающему каскаду, когда он используется в EIB-сети (European Installation Bus - прим. Переводчика), установлены в «Коnnех Handbuch, Version 2.0». На основании этих требований происходит сертификация готовых приборов шины.

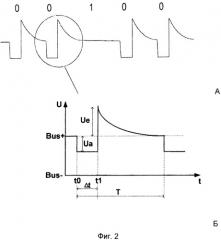

На фиг.2 на фрагменте (А) показана битовая последовательность из приведенной в качестве примера EIB-телеграммы, которая генерируется согласно последовательности импульсов передаваемого сигнала, на фрагменте (Б) показаны детали отдельного битового импульса. Bus+ является номинальным напряжением шины, Bus- представляет собой общий потенциал для дальнейших рассмотрений, то есть потенциал массы. EIB-сигнал отдельного передаваемого импульса определяется от номинального напряжения Bus+ шины ограниченным во времени и синхронизируемым по длительности с передаваемым сигналом падением Ua напряжения, в дальнейшем называемым активным импульсом. С целью минимизации энергии при отправлении сообщения затем следует заданное превышение напряжения Ue выше номинального напряжения Bus+ шины, которое начинает так называемый уравнивающий импульс. При взаимодействии с дроссельным модулем как преобразователем полного сопротивления блока питания шины, который при этом одновременно представляет собой накопитель энергии, после каждого активного сигнала (передаваемого импульса) происходит обратная подача энергии на шинную линию. После этого выравнивающий импульс затухает в виде экспоненциальной функции, пока после истечения битового периода Т не появится следующий бит телеграммы. Тогда уравнивающий импульс должен полностью затухнуть, чтобы были обеспечены заданные условия напряжения для следующего бита.

Шинные узлы в их функции передатчика соответственно генерируют эти сигналы. Идеальным образом то же самое количество энергии, которое извлекает передаваемый импульс из шины с активным импульсом, снова подводится во время выравнивающего импульса.

Для того чтобы выработать битовый сигнал, которыйудовлетворяет вышеописанным требованиям, в обычном случае требуются две части схемы, а именно схема для выработки активного импульса и схема для выработки следующего за активным импульсом выравнивающего импульса, хотя имеется также решение, которое отказывается от последней схемы. Для этого предусмотрена по меньшей мере одна управляющая схема, которая выдает передаваемый сигнал, по меньшей мере, схеме для выработки активного импульса.

Подобный передающий каскад описан в DE 102006011595 В4. Там моделирование активного импульса происходит в соответствии с текущим приложенным постоянным напряжением шины, причем амплитуда активного импульса задается амплитудой вырабатываемого в передающем каскаде передаваемого сигнала. Для воспроизводства энергии вызванная активным импульсом потеря энергии сохраняется в емкостном накопительном элементе. Этим путем на накопительном элементе создается напряжение, которое выше, чем напряжение шины. В схеме для выработки активного импульса и в схеме для выработки выравнивающего импульса соответственно предусмотрена управляющая схема, причем управляющие схемы общаются друг с другом, чтобы передать дальше передаваемый сигнал.

ЕР 0909497 В1 описывает шинный контроллер с управляемой по амплитуде передающей схемой, в котором изменение амплитуды активного импульса регулируется посредством напряжения на узле схемы делителя напряжения.

WO 6/31012 А1 описывает передающий каскад, в котором напряжение +V используется для регулировки изменения амплитуды активного импульса независимо от постоянной составляющей напряжения шинного сигнала.

WO 98/04027 A1 описывает передающий каскад согласно ограничительной части п.1, в котором предусмотрены схема для выработки активного импульса и схема для выработки выравнивающего импульса, а также управляющая схема, которая выдает передающий сигнал, по меньшей мере, на схему для выработки активного импульса. При этом малая емкость трансформируется в схеме Миллера, которая состоит из этой малой емкости, а также из транзистора и управляющего сопротивления, и с двумя схемами усилителя тока с достаточно большой емкостью, так что при краткосрочном рассмотрении относительно постоянной времени предоставляется в распоряжение низкоомное соединение с шинной линией. Оно имеет стабильное снижение напряжения, которое возникает из напряжения шины минус источник постоянного напряжения и минус напряжение база-эмиттер транзистора последней схемы усилителя тока. Так как эмиттер с передающим транзистором для длительности активного импульса отбирается на массу, на шине независимо от напряжения шины находится активный импульс, который каждый раз имеет одинаковые по величине амплитуды.

Известный передающий каскад использует, прежде всего, в схеме для выработки активного импульса большое количество активных схемных элементов, которые существенно увеличивают стоимость передающего каскада.

Задача настоящего изобретения состоит в том, чтобы дополнительно упростить упомянутый передающий каскад и тем самым снизить его стоимость за счет в значительной мере отказа от активных электронных элементов и использования пассивных электронных компонентов, которые, как правило, являются существенно более дешевыми.

При этом каждый раз посредством оптимизированного формирования сигнала необходимо позаботиться о том, что отобранная энергия в максимально возможной степени могла быть возвращена на шину.

Эта задача решена посредством передающего каскада по п.1 формулы изобретения. Предпочтительные варианты осуществления являются предметом зависимых пунктов формулы изобретения. Использование передающего каскада согласно изобретению дается в п.6 формулы изобретения.

Изобретение отказывается от использования схемы Миллера из уровня техники с последовательно включенными схемами усилителя тока, которые обременены большим количеством транзисторов. Этот совокупный комплекс заменяется единственной схемой с пассивными схемными элементами, так что активные элементы присутствуют лишь в управляющей схеме или же в передающем транзисторе. Использование только пассивных элементов обуславливает компромисс при согласовании емкости конденсатора С1 и сопротивлений R1, R2 и R3, как поясняется еще далее.

Согласно изобретению у передающего каскада глубина импульса активного импульса устанавливается заданным опорным напряжением, которое является независимым от величины постоянной составляющей напряжения битового сигнала или сигнала шины. Благодаря этому удается, так сказать, заранее получить информацию о том, как много энергии отберет активный импульс, так что посредством подходящего выбора параметров элемента выдержки времени (например, дифференцирующей схемы) может быть задано поведение затухания выравнивающего импульса. При этом глубину импульса активного импульса поддерживает постоянной за счет отрицательной обратной связи по переменной составляющей напряжения битового сигнала, что, кроме того, способствует возможности точного определения отобранной в активном импульсе энергии. Помимо этого, согласно изобретению предусмотрено, что между несущей напряжение частью шинной линии и узлом напряжения подключен конденсатор, причем узел напряжения образует отбор напряжения питаемой за счет опорного напряжения схемы делителя напряжения, который через защитное сопротивление приложен к базе транзистора, который является частью управляющей схемы передающего транзистора, причем сопротивления схемы делителя напряжения задают глубину импульса, и причем емкость конденсатора и величины сопротивлений схемы делителя напряжения и защитного сопротивления согласованы так, что их постоянная времени обеспечивает перенос передаваемого сигнала в течение длительности активного импульса.

При этом опорное напряжение может быть обеспеченным источником питания шинного узла напряжением питания или промежуточным напряжением, которое вырабатывается в источнике питания шинного узла.

Еще более предпочтительно предусмотрено, что, когда имеется схема для выработки выравнивающего импульса, она имеет по меньшей мере два накопителя энергии, которые к началу передаваемого импульса включены параллельно и в течение длительности передаваемого импульса заряжаются до имеющегося в данный момент напряжения шины, а в конце передаваемого импульса включаются последовательно, причем общее напряжение на последовательно включенных накопителях энергии подключается к шине. Тем самым надежно достигается, что имеется напряжение, которое прямо или косвенно, то есть предварительно подготовлено, имеется в распоряжении как требуемое превышение напряжения, затухание которого можно просто оптимизировать.

Предпочтительно, предусмотрена одна единственная управляющая схема, которая управляет схемой для выработки активного импульса и схемой для выработки выравнивающего импульса. Это упрощает фактическое построение схемы и будет возможным, так как выравнивающий импульс непосредственно синхронизируется передаваемым импульсом.

Наконец, изобретение описывает применение передающего каскада по пп.1-5 формулы изобретения в специализированной для решения конкретной задачи интегральной схеме (ASIC - Application Specific Integrated Circuit), которая может также содержать дополнительные детали схемы, например приемник, источник питания и т.п.

В дальнейшем изобретение будет более подробно разъяснено с помощью прилагаемого рисунка.

Фиг.1 показывает пример конфигурации шины.

Фиг.2 на фрагменте (А) показывает битовую последовательность из приведенной в качестве примера EIB-диаграммы, а на фрагменте (Б) - детали битового импульса из битовой последовательности.

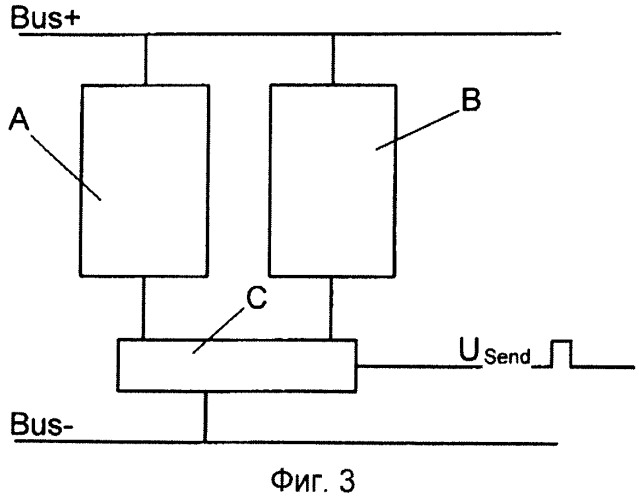

Фиг.3 показывает блок-схему передающего каскада согласно примеру осуществления настоящего изобретения.

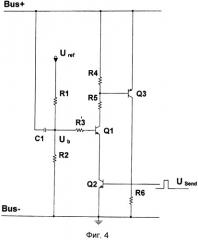

Фиг.4 показывает пример осуществления схемы для выработки активного импульса, которая используется в передающем каскаде согласно настоящему изобретению.

Фиг.5 показывает схему для выработки выравнивающего импульса, которая используется в передающем каскаде согласно настоящему изобретению.

Фиг.6 показывает пример полного передающего каскада согласно настоящему изобретению вместе с управляющей схемой.

В нижеследующем описании и на рисунках представлены многочисленные определенные подробности. Однако понятно, что варианты осуществления настоящего изобретения могут применяться на практике без этих определенных подробностей. В других случаях опущены хорошо известные схемы, структуры и способы, чтобы не усложнять понимание изобретения. Понятно, что в представленных вариантах осуществления могут быть предприняты многочисленные модификации и изменения без удаления от объема изобретения. Поэтому представленные примеры осуществления должны рассматриваться как описательные, а не как ограничительные. Прежде всего, понятно, что, хотя примеры осуществления выполнены с биполярными транзисторами, могут быть использованы другие технологии, так что схемы, например, могли бы быть реализованы с полевыми транзисторами.

На фиг.3 показана блок-схема передающего каскада в шинном узле согласно одному варианту осуществления настоящего изобретения. При этом схема А для выработки активного импульса и схема В для выработки следующего за активным импульсом выравнивающего импульса управляются от единственной управляющей схемы С, которая выдает передаваемый сигнал, по причине упрощения представленный как отдельный передаваемый импульс Usend, как схеме А для выработки активного импульса, так и схеме В для выработки выравнивающего импульса. Выдающее сигнал Usend управляющее устройство на фигурах не показано. Альтернативно, передающий каскад может быть реализован также без схемы В для выработки выравнивающего импульса,

На фиг.4 показан пример схемы для выработки активного импульса для передающего каскада согласно настоящему изобретению.

Транзистор Q3 представляет собой передающий транзистор в качестве эмиттерного повторителя, который переключается управляющей схемой, которая образована из транзисторов Q1 и Q2. Передаваемый сигнал Usend прикладывается к базе транзистора Q2. В состоянии покоя, то есть в отсутствие передаваемого импульса, транзистор Q2 заперт и, поскольку через сопротивление R5 не может протекать никакой ток, также, следовательно, и транзистор Q3. Так как транзистор Q2 заперт, то по цепи тока база-эмиттер транзистора Q1 не может протекать никакой ток, поэтому он также закрыт, хотя к базе от образованного сопротивлениями R1 и R2 делителя напряжения через защитное сопротивление R3 приложено управляющее напряжение Ub. Тем самым транзистор Q1 подготовлен к открыванию. При выдаче импульса Usend длительностью Δt=t1-t0 от (не показанного) управляющего устройства открывается транзистор Q2. Поскольку теперь по цепи тока база-эмиттер транзистора Q1 течет ток, транзистор Q1 также открывается. Теперь через сопротивление R5 течет ток, который открывает передающий транзистор Q3 и сдвигает напряжение Bus+ шины заданным посредством сопротивления R6 током вниз. На шине образуется активный импульс.

Конденсатор С1 служит для отрицательной обратной связи по переменной составляющей напряжения сигнала шины. Конденсатор передает падающий фронт при t0 как отрицательное напряжение делителю напряжения R1, R2. Когда оно достигнет величины -Ub плюс суммируемых падений напряжения на отрезке база-эмиттер транзистора Q1 и напряжения насыщения эмиттер-коллектор Q2, то транзистор Q1 закрывается и, как следствие, также транзистор Q3, так что напряжение шины Bus+ больше не может падать. За счет постоянного подрегулирования посредством отрицательной обратной связи через конденсатор С1 напряжение Ua остается постоянным в течение всей длительности импульса Δt=t1-t0. При соответствующем подборе параметров напряжение Ub на узлах С1, R1 и R2, так сказать, перезаписывается падающим напряжением сигнала на шине.

При этом величины сопротивлений R1, R2 и R2 должны быть, с одной стороны, по возможности высокими, чтобы не очень сильно загружать шинную линию, а с другой стороны, достаточно низкими, чтобы в момент передаваемого импульса Usend обеспечить надежное открывание транзистора Q1. Также суммарную постоянную времени ветви обратной связи следует задать так, чтобы переменный сигнал по напряжению в течение Δt=t1-t0 хорошо переносился от шины. Эта постоянная времени задается емкостью конденсатора С1 и величиной параллельно соединенных сопротивлений R1, R2 и R3. Эти частично противоположные требования могут быть удовлетворены лишь с компромиссом. При этом глубина импульса задается посредством Uref и делителя напряжения R1, R2 вдобавок к падениям напряжения на теперь активных транзисторах Q1 и Q2. Если величина сопротивления R3 не будет выбрана слишком высокой, то падением напряжения из-за очень низкого тока базы транзистора Q1 можно будет пренебречь.

Напряжением питания для подключенных прикладных систем может быть Uref или также промежуточное напряжение, которое вырабатывается источником питания для шинного узла, как это, например, описано в WO 2011/085703. Опорное напряжение Uref может быть использовано напрямую, если оно имеет требуемую величину, чтобы достичь требуемой глубины импульса. Оно может быть также обеспечено диодом Зенера или регулятором напряжения. Для подобных вариантов осуществления сопротивление R2 может стать ненужным.

На фиг.5 показана схема для выработки выравнивающего импульса. В состоянии покоя, следовательно, без передаваемого импульса Usend, который воздействует на базу транзистора Q6, схема по причине закрытого транзистора Q6 и, как следствие, также закрытого транзистора Q5 является обесточенной. При подаче импульса Usend продолжительностью Δt=t1-t0 со стороны (не показанного) управляющего устройства транзистор Q6 открывается. Через сопротивление R7 и диод D2 конденсатор С2 заряжается до имеющегося в данный момент напряжения шины Bus+, которое существует во время активного импульса. Одновременно через сопротивление R11 и диод D6 течет ток базы для транзистора Q5, который теперь также открывается. Через диод D5 и сопротивление R9 конденсатор С4 также заряжается до имеющегося в данный момент напряжения шины. Конденсаторы С2 и С4 сначала во время активного импульса включены параллельно. Также через диод D4 и через сопротивление R8 течет ток, однако если сопротивление R8 выбирается относительно высокоомным, этим током можно пренебречь и он загружает шину лишь в малой степени. Транзистор Q4 закрыт и, поскольку катоды обоих диодов D4 и D5 имеют примерно одинаковый потенциал, конденсатор СЗ практически разряжен.

В момент времени t1 передаваемый сигнал Usend заканчивается и транзистор Q6 закрывается, так что через сопротивление R7 и диод D2 больше не протекает никакой ток. Как следствие, транзистор Q5 также закрывается. Диоды D4 и D5 расположены противополярно, так что этот участок также не проводит никакой ток. Теперь ток течет от заряженного конденсатора С4 через участок коллектор-база транзистора Q4, разряженный конденсатор С3 и сопротивление R8. Транзистор Q4 открывается. Теперь оба конденсатора С4 и С2 включены последовательно. Их суммарное напряжение выше, чем напряжение Bus+ шины, так что теперь в шину течет относительно большой ток, который ограничивается сопротивлением R9. Теперь конденсатор С3 будет постоянно подзаряжаться через сопротивление R8, пока транзистор Q4 снова не закроется. Благодаря соответствующему подбору конденсатора С3 и сопротивления R8 и полученной вследствие этого постоянной времени получают во взаимодействии с преобразователем полного сопротивления блока питания шины заданным образом затухающий выравнивающий импульс для требуемого согласно фиг.2 поведения.

На фиг.6 показана комбинация схем согласно фиг.4 и фиг.5. Транзистор Q2 берет на себя здесь также функцию транзистора Q6 из схемы согласно фиг.5, так что передаваемый импульс Usend подается как на схему для выработки активного импульса, так и на схему для выработки выравнивающего импульса. Предусмотрен развязывающий диод D1, который отделяет схемы с точки зрения функции друг от друга.

Раскрытые в вышеприведенном описании, на рисунках, а также в пунктах формулы изобретения признаки изобретения могут как по отдельности, так и в любой комбинации быть существенными для осуществления изобретения.

1. Передающий каскад в шинном узле шинной сети, прежде всего в шинном узле EIB-сети, который подключен к шинной линии (Bus+, Bus-), для выработки соответствующего передаваемому сигналу, который имеет последовательность передаваемых импульсов, битового сигнала, который для каждого передаваемого импульса состоит из:активного импульса, который имеет длительность Δt=t1-t0, причем t0 указывает на начало активного импульса, a t1 - на конец активного импульса, и глубину Ua импульса, иследующего за активным импульсом выравнивающего импульса, с:- схемой (А) для выработки активного импульса,- схемой (В) для выработки выравнивающего импульса, и- по меньшей мере одной управляющей схемой (С) для выдачи передаваемого сигнала (Usend), по меньшей мере, схеме (А) для выработки активного импульса,при этом глубина (Ua) импульса активного импульса установлена заданным опорным напряжением (Uref), которое является независимым от величины постоянной составляющей напряжения битового сигнала,при этом схема (А) для выработки активного импульса выполнена таким образом, что она поддерживает постоянной глубину (Ua) импульса активного импульса за счет отрицательной обратной связи по переменной составляющей напряжения битового сигнала,отличающийся тем, чтомежду несущей напряжение частью шинной линии (Bus+) и узлом (Ub) напряжения подключен конденсатор (С1),причем узел (Ub) напряжения образует отбор напряжения питаемой за счет опорного напряжения (Uref) схемы (Uref, R1, R2) делителя напряжения, который через защитное сопротивление (R3) приложен к базе транзистора (Q1), который является частью управляющей схемы (Q1, Q2) передающего транзистора (Q3),причем сопротивления (R1, R2) схемы делителя напряжения задают глубину (Ua) импульса, ипричем емкость конденсатора (С1) и величины сопротивлений (R1, R2) схемы делителя напряжения и защитного сопротивления (R3) согласованы так, что их постоянная времени обеспечивает перенос передаваемого сигнала в течение длительности Δt активного импульса.

2. Передающий каскад по п.1, отличающийся тем, что опорное напряжение (Uref) является обеспечиваемым источником питания шинного узла напряжением питания.

3. Передающий каскад по п.1, отличающийся тем, что опорное напряжение (Uref) является вырабатываемым источником питания шинного узла промежуточным напряжением.

4. Передающий каскад по п.1, отличающийся тем, что схема (В) для выработки выравнивающего импульса имеет по меньшей мере два накопителя (С2, С4) энергии и выполнена таким образом, что она:- в начале (t0) активного импульса параллельно включает два накопителя энергии, так что они в течение длительности (Δt) активного импульса заряжаются до имеющегося в данный момент напряжения шины, и- в конце (t1) активного импульса последовательно включает два накопителя энергии и суммарное напряжение на включенных последовательно накопителях (С2, С4) энергии подключает к шине.

5. Передающий каскад по п.1, отличающийся тем, что предусмотрена одна единственная управляющая схема (С) для управления как схемой (А) для выработки активного импульса, так и схемой (В) для выработки выравнивающего импульса.

6. Использование передающего каскада по одному из пп.1-5 в специализированной для решения конкретной задачи электрической схеме.