Устройство формирования переноса в сумматоре

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации арифметических устройств. Техническим результатом является повышение надежности. Устройство содержит логические транзисторы n-типа, предзарядовые транзисторы р-типа, инвертирующие элементы, каждый из которых содержит тактовый транзистор р-типа, логический транзистор р-типа и тактовый транзистор n-типа, шину питания, шину земли, логические выводы, логические входы, прямой и инверсный выходы. 1 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации арифметических устройств.

Известно устройство формирования переноса в составе сумматора (Патент РФ №2239227, G06F 7/50 от 27.10.2004). Это устройство содержит в разряде два предзарядовых транзистора р-типа и 12 логических транзисторов n-типа. Недостатками устройства являются ограниченное быстродействие при необходимости перезаряда выходных емкостей через цепь из 4 последовательно соединенных транзисторов и ограниченные функциональные возможности, поскольку соседние (четные) разряды сумматра должны выполняться на транзисторах дополняющего р-типа, что также снижает быстродействие устройства.

Наиболее близким техническим решением к предлагаемому является устройство формирования переноса на основе дифференциальной схемотехники типа «домино» (Пат. США №7428568, FIG.1, G06F 7/50, НКИ 708/702 от 23.09.2008 г.). Устройство содержит два предзарядовых транзисторов р-типа, два транзистора обратной связи р-типа, тактовый транзистор n-типа и десять логических транзисторов n-типа. Недостатком устройства является недостаточная надежность функционирования, поскольку в исходном состоянии и при неравенстве переменных до момента поступления парафазных сигналов переноса на обоих дифференциальных выходах устройства сохраняются сигналы логической 1, что ведет к неопреленности функционирования устройства для последовательно включенных каскадов (разрядов сумматора).

Техническим результатом изобретения является повышение надежности.

Технический результат достигается тем, что устройство формирование переноса в сумматоре содержит десять логических транзисторов n-типа, первый и второй предзарядовые транзисторы р-типа, которые включены между шиной питания и соответственно первым и вторым логическими выводами, попарно соединены последовательно и включены между первым логическим выводом и общим выводом первый и второй, третий и четвертый, пятый и четвертый логические транзисторы n-типа, а также соединены попарно последовательно и включены между вторым логическим выводом и общим выводом шестой и седьмой, восьмой и девятый, десятый и девятый логические транзисторы n-типа, затворы логических транзисторов n-типа подключены к соответствующим логическим входам устройства, причем попарно объединены затворы первого и третьего, второго и пятого, шестого и восьмого, седьмого и десятого логических транзисторов n-типа, а также содержит первый и второй инвертирующие элементы, каждый из которых содержит тактовый и логический транзисторы р-типа и тактовый транзистор n-типа, которые включены последовательно между шиной питания и шиной земли, первый и второй логические выводы подключены к затворам логических транзисторов р-типа соответственно первого и второго инвертирующих элементов, точка соединения логического транзистора р-типа и тактового транзистора n-типа первого инвертирующего элемента подключена к прямому выходу устройства и к затвору первого предзарядового транзистора р-типа. а точка соединения логического транзистора р-типа и тактового транзистора n-типа второго инвертирующего элемента подключена к инверсному выходу устройства и к затвору второго предзарядового транзистора р-типа, затворы тактовых транзисторов n-типа и затворы тактовых транзисторов р-типа первого и второго инвертирующих элементов, а также общий вывод подключены к тактовой шине.

Существенными отличительными признаками в указанной совокупности признаков является наличие инвертирующих элементов, содержащих последовательно включенные между шиной питания и шиной земли тактовый и логический транзисторы р-типа и тактовый транзистор n-типа в их совокупности с новыми связями и известными признаками устройства.

Наличие в предлагаемом устройстве перечисленных выше существенных отличительных признаков обеспечивает решение поставленной технической задачи - повышения надежности.

В устройстве-прототипе известные логические функции переноса при тактировании и при неравенстве переменных до момента поступления парафазных сигналов переноса реализуются при наличии на дифференциальных выходах устройства сигналов высокого уровня, что ведет к неопреленности функционирования устройства для последовательно включенных каскадов (разрядов сумматора). В заявленном устройстве те же логические функции реализуются при наличие нулевых сигналов на выходах переноса, что при непосредственном соединении устройств данного типа исключает неопределенность логического состояния и временной "дребезг" сигналов. Предзарядовые транзисторы р-типа, управляемые по затворам с парафазных выходов, обеспечивают не только наличие нулевых сигналов на выходах переноса в исходном состояннн, но и за счет обратной связи надежность сохранности нулевого сигнала на одном из выходов переноса в процессе переключения в парафазное состояние.

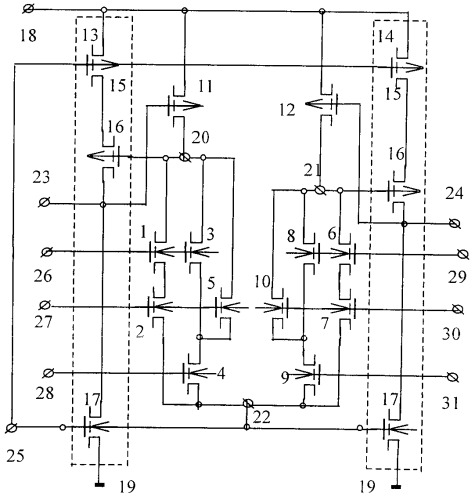

На чертеже приведена принципиальная схема заявляемого устройства формирования переноса в сумматоре.

Устройство содержит десять логическиех транзисторов 1-10 n-типа, первый 11 и второй 12 предзарядовые транзисторы р-типа, первй 13 и второй 14 инвертирующие элементы, каждый из которых содержит тактовый 15 и логический 16 транзисторы р-типа и тактовый транзистор 17 n-типа, которые включены последовательно между шиной питания 18 и шиной земли 19.

Первый 11 и второй 12 предзарядовые транзисторы р-типа включены между шиной питания 18 и соответственно первым 20 и вторым 21 логическим выводами. Попарно соединены последовательно и включены между первым логическим выводом 20 и общим выводом 22 первый 1 и второй 2, третий 3 и четвертый 4, пятый 5 и четвертый 4 логические транзисторы n-типа, а также соединены попарно последовательно и включены между вторым логическим выводом 21 и общим выводом 22 шестой 6 и седьмой 7, восьмой 8 и девятый 9, десятый 10 и девятый 9 логические транзисторы n-типа.

Первый 20 и второй 21 логические выводы подключены к затворам логического транзистора 16 р-типа соответственно первого 13 и второго 14 инвертирующего элемента. Точка соединения логического транзистора 16 р-типа и тактового транзистора 17 n-типа первого инвертирующего элемента 13 подключена к прямому выходу 23 устройства и к затвору первого предзарядового транзистор 11 р-типа. Точка соединения логического транзистора 16 р-типа и тактового транзистора 17 n-типа второго инвертирующего элемента 14 подключена к инверсному выходу 24 устройства и к затвору второго предзарядового транзистора 12 р-типа. Затворы тактовых транзисторов 17 n-типа, затворы тактовых транзисторов 15 р-типа первого 13 и второго 14 инвертирующих элементов, а также общий вывод 22 подключены к тактовой шине 25. Затворы логических транзисторов 1-10 n-типа подключены к логическим входам 26-31 устройства, причем попарно объединены затворы первого 1 и третьего 3, второго 2 и пятого 5, шестого 6 и восьмого 8, седьмого 7 и десятого 10 логических транзисторов n-типа.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при единичном сигнале на тактовой шине 25 тактовые транзисторы р-типа 15 закрыты, а тактовые транзисторы 17 n-типа открыты в первом 13 и втором 14 инвертирующих элементах. Выходы 23 и 24 устройства находятся в нулевом состоянии, предзарядовые транзисторы 11 и 12 р-типа открыты и узловые емкости логических выходов 20 и 21 заряжаются до напряжения шины питания.

На логический вход 26 подан сигнал переменной А, а на логический вход 27 подан сигнал переменной В, на логический вход 28 - сигнал переменной (переноса) С, на логический вход 29 подан сигнал переменной Ā, на логический вход 30 - сигнал переменной B ¯ , а на логический вход 31 - сигнал переменной C ¯ .

Рабочий полутакт начинается с подачи на тактовую шину 25 нулевого сигнала, при этом тактовые транзисторы 15 р-типа инвертирующих элементов 13,14 открываются, а тактовые транзисторы 17 n-типа закрываются. При равенстве переменных А=В=1 проводящей является цепь первого 1 и второго 2 логических транзисторов n-типа. При С=1 дополнительно проводят цепи, состоящие из логических транзисторов 3-4 и 4-5 n-типа. Напряжение на узловой емкости первого логического вывода 20 падает, тактовый транзистор 15 р-типа первого инвертирующего элемента 13 открывается, напряжение на прямом выходе 23 устройства растет, а первый предзарядовый транзистор 11 р-типа закрывается. При неравенстве переменных А и В и при переносе С=1 проводящей является цепь транзистора 4 и одного из последовательно с ним включенного 3 или 5 логического транзистора n-типа. При этом на прямом выходе 23 устройства формируеся сигнал логической 1, что соответствует результату переноса, равного 1. Цепи, содержащие логические транзисторы 6-10, при этом выключены и на инверсном выходе 24 устройства сохраняется нулевой сигнал, т.е. C ¯ = 0 .

Аналогично функционируют цепи логических транзисторов 6-10 n-типа при сответствующих инверсных значениях переменных А и В и при переносе С=0. В этом случае на инверсном выходе 24 устройства формируется сигнал логической 1, а на прямом выходе 23 устройства - сигнал логического 0.

Устройство формирования переноса в сумматоре, содержащее десять логических транзисторов n-типа, первый и второй предзарядовые транзисторы р-типа, которые включены между шиной питания и соответственно первым и вторым логическими выводами, попарно соединены последовательно и включены между первым логическим выводом и общим выводом первый и второй, третий и четвертый, пятый и четвертый логические транзисторы n-типа, а также соединены попарно последовательно и включены между вторым логическим выводом и общим выводом шестой и седьмой, восьмой и девятый, десятый и девятый логические транзисторы n-типа, затворы логических транзисторов n-типа подключены к соответствующим логическим входам устройства, причем попарно объединены затворы первого и третьего, второго и пятого, шестого и восьмого, седьмого и десятого логических транзисторов n-типа, отличающееся тем, что устройство содержит первый и второй инвертирующие элементы, каждый из которых содержит тактовый и логический транзисторы р-типа и тактовый транзистор n-типа, которые включены последовательно между шиной питания и шиной земли, первый и второй логические выводы подключены к затворам логических транзисторов р-типа соответственно первого и второго инвертирующих элементов, точка соединения логического транзистора р-типа и тактового транзистора n-типа первого инвертирующего элемента подключена к прямому выходу устройства и к затвору первого предзарядового транзистора р-типа, а точка соединения логического транзистора р-типа и тактового транзистора n-типа второго инвертирующего элемента подключена к инверсному выходу устройства и к затвору второго предзарядового транзистора р-типа, затворы тактовых транзисторов n-типа и затворы тактовых транзисторов р-типа первого и второго инвертирующих элементов, а также общий вывод подключены к тактовой шине.