Управление скоростью, с которой обрабатываются запросы на прерывание, формируемые адаптерами

Иллюстрации

Показать всеГруппа изобретений относится к вычислительной технике и может быть использована для управления обработкой запросов прерывания. Техническим результатом является обеспечение возможности управления скоростью обработки прерываний. Сущность изобретений состоит в том, что контролируются ситуации, при которых прерывания адаптера переводятся в режим ожидания. С учетом прерывания, передаваемого на операционную систему, последующие прерывания подавляются на всех центральных процессорах в конфигурации. Операционная система обрабатывает прерывание, включая проверку и обработку указателей событий, о которых уведомляется, пока операционная система не прекращает блокировку. Это позволяет операционной системе контролировать число ожидающих прерываний и число процессоров, обрабатывающих эти прерывания. 2 н. и 8 з. п. ф-лы, 41 ил.

Реферат

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Изобретение относится в общем к обработке прерывания в вычислительной среде, а, в частности, к управлению обработкой запросов прерывания, сгенерированных адаптерами вычислительной среды.

В некоторых вычислительных средах, например, основанных на системе z/Architecture®, предложенной International Business Machines Corporation, Армонк, Нью-Йорк, прерывания, запрошенные адаптерами ввода/вывода (I/O), определяются в качестве подклассов прерывания. Эти подклассы используются, например, для присваивания приоритетов прерываниям для их обработки операционной системой процессора.

Для обработки процессором вычислительной среды прерываний подкласса прерывания (ISC), процессор должен быть приспособлен к этому подклассу. После приспособления процессор может обрабатывать прерывания этого подкласса, но не других подклассов, к которым он не приспособлен. Несколько процессоров могут быть приспособлены к подклассу и, следовательно, несколько процессоров могут одновременно обрабатывать прерывания данного класса.

В патенте США No. 7065598 под названием "Method, System, and Article of Manufacture for Adjusting Interrupt Levels", опубликованном 20 июня 2006 г., на имя Connor и др., предоставляется способ, система и изделие для установки уровней прерывания. Определяется скорость прерываний текущей системы вычислительного устройства, где скорость прерываний текущей системы является суммой скоростей прерываний нескольких сред, генерирующих прерывание. Скорость прерываний текущей системы сравнивается по меньшей мере с одной пороговой скоростью прерываний, относящейся к вычислительному устройству. На основе сравнения для среды, генерирующей прерывание, нескольких сред, генерирующих прерывание, устанавливается уровень замедления прерывания.

В патенте США No. 7398343 под названием "Interrupt Processing System", опубликованном 8 июля 2008 года, на имя Marmash и др., описывается система обработки прерываний, имеющая регистры хранения прерываний, каждый из которых соответствует различному классу прерываний. Очередь записи предоставляет информацию об обслуживании, необходимом регистрам хранения прерываний. Регистр вектора прерываний имеет битовые позиции в соответствии с различными классами прерываний. Очередь чтения на выходе соединена с несколькими регистрами хранения прерываний и регистром вектора прерываний. Логика определения соединяется между схемой разрешения конфликтов, данные в которую загружаются очередями записи и чтения, и процессором для: (а) указания того, произошла ли передача прерывания от схемы разрешения конфликтов записи к процессору; (б) определения класса прерывания такого переданного прерывания; (в) активации одной из битовых позиций в соответствии с определенным классом прерывания в регистре вектора прерывания для сохранения состояния, указывающего требование по обслуживанию для такого определенного класса прерывания; и (г) определения того, были ли переданы данные, сохраненные в регистре вектора прерывания, на процессор посредством очереди чтения и селектора схемы разрешения конфликтов.

В патенте США No. 6615305 под названием "Interrupt Pacing in Data Transfer Unit", опубликованном 2 сентября 2003 г., на имя Olesen и др., раскрываются аппаратура и способ управления количеством прерываний, которое блок передачи данных генерирует для ЦП. Блок, задающий скорость, используется для регистрации предпринятых попыток передачи (событий) данных с блока передачи данных на ЦП и сравнивает это значение с пороговым пределом, определенным пользователем. Если количество событий достигает порогового предела, тогда для ЦП генерируется прерывание.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Согласно одной из особенностей настоящего изобретения предлагается возможность управления тем количеством процессоров, которые одновременно обрабатывают прерывания данного подкласса прерываний, и/или управления скоростью обработки прерываний.

Преодоление недостатков известного уровня техники и достижение преимуществ обеспечивается за счет способа по п.1 и соответствующих системы и компьютерного программного продукта для управления обработкой прерывания в вычислительной среде с несколькими процессорами.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Одна или несколько особенностей настоящего изобретения конкретно охарактеризованы и отдельно заявлены в формуле изобретения, следующей за описанием. Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее подробного описания в сочетании с сопровождающими его чего чертежами, на которых:

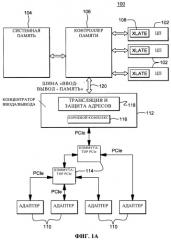

ФИГ.1A иллюстрирует один вариант осуществления вычислительной среды для включения и использования одной или нескольких особенностей настоящего изобретения.

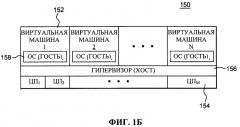

ФИГ.1Б иллюстрирует один из вариантов осуществления центрального комплекса обработки данных, в котором хост выполняет функции одной или нескольких гостей согласно одной из особенностей настоящего изобретения.

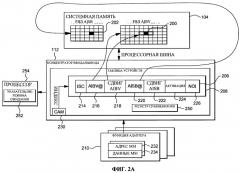

ФИГ.2A - один из вариантов осуществления дополнительных подробностей системной памяти и концентратора ввода-вывода, показанных на ФИГ.1A, согласно одной из особенностей настоящего изобретения.

ФИГ.2Б - другой из вариантов осуществления дополнительных подробностей системной памяти и концентратора ввода-вывода, показанных на ФИГ.1A, согласно одной из особенностей настоящего изобретения.

ФИГ.2B - один из вариантов осуществления записей в гостевой таблице (GAIT) прерываний адаптера, используемой согласно одной из особенностей настоящего изобретения.

ФИГ.2Г - один из вариантов осуществления гостевой области (GISA) состояния прерываний, используемой согласно одной из особенностей настоящего изобретения.

ФИГ.2Д - один из вариантов осуществления записей таблицы (AIFT) переадресации прерываний адаптера, используемых согласно одной из особенностей настоящего изобретения.

ФИГ.3 - один из вариантов осуществления общего представления логики для обработки прерываний, инициируемых сообщениями, полученных от адаптеров согласно одной из особенностей настоящего изобретения.

ФИГ.4 - один из вариантов осуществления диаграммы состояния, иллюстрирующей переход между различными режимами обработки прерываний согласно одной из особенностей настоящего изобретения.

ФИГ.5A - один из вариантов осуществления команды Set Interruption Controls, используемой согласно одной из особенностей настоящего изобретения.

ФИГ.5Б-5Г - примеры содержимого полей, используемых командой Set Interruption Controls, показанной на ФИГ.5A, согласно одной из особенностей настоящего изобретения.

ФИГ.5Д - один из примеров блока (AIPB) параметров прерывания адаптера, используемого согласно одной из особенностей настоящего изобретения.

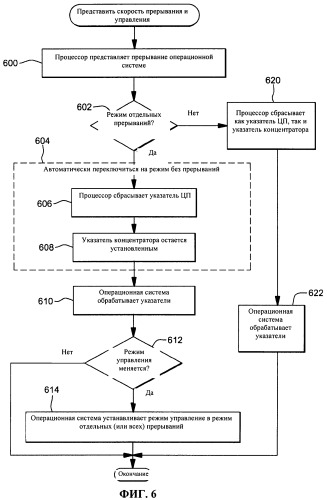

ФИГ.6 - один из вариантов осуществления логики для управления скоростью, с которой обрабатываются прерывания, согласно одной из особенностей настоящего изобретения.

ФИГ.7 - один из вариантов осуществления логики для управления скоростью, с которой гостем обрабатываются прерывания, согласно одной из особенностей настоящего изобретения.

ФИГ.8 - один из вариантов осуществления диаграммы перехода состояний, показанной на ФИГ.4, а также переход от одного режима к другому в виртуальной среде согласно одной из особенностей настоящего изобретения.

ФИГ.9A - один из вариантов осуществления команды Modify PCI Function Controls, используемой согласно одной из особенностей настоящего изобретения.

ФИГ.9Б - один из вариантов осуществления поля, используемого командой Modify PCI Function Controls, проиллюстрированной на ФИГ.9A согласно одной из особенностей настоящего изобретения.

ФИГ.9B - один из вариантов осуществления другого поля, используемого командой Modify PCI Function Controls проиллюстрированной на ФИГ.9A согласно одной из особенностей настоящего изобретения.

ФИГ.9Г - один из вариантов осуществления содержимого блока информации о функциях (FIB), используемого согласно одной из особенностей настоящего изобретения.

ФИГ.10 - один из вариантов осуществления общего представления логики команды Modify PCI Function Controls согласно одной из особенностей настоящего изобретения.

ФИГ.11 - один из вариантов осуществления логики, связанной с операцией регистрации прерываний адаптера, которая может быть определена командой Modify PCI Function Controls, согласно одной из особенностей настоящего изобретения.

ФИГ.12 - один из вариантов осуществления логики, связанной с операцией отмены регистрации прерываний адаптера, которая может быть определена командой Modify PCI Function Controls, согласно одной из особенностей настоящего изобретения.

ФИГ.13A - один из вариантов осуществления команды Call Logical Processor, используемой согласно одной из особенностей настоящего изобретения.

ФИГ.13Б - один из вариантов осуществления блока запроса, используемого командой Call Logical Processor, показанной на ФИГ.13A, для выполнения операции списка согласно одной из особенностей настоящего изобретения.

ФИГ.13B - один из вариантов осуществления блока ответа для операции списка, показанной на ФИГ.13Б, согласно одной из особенностей настоящего изобретения.

ФИГ.13Г - один из вариантов осуществления записи списка функций, применимой согласно одной из особенностей настоящего изобретения.

ФИГ.14A - один из вариантов осуществления блока запроса, используемого командой Call Logical Processor, показанной на ФИГ.13A, для выполнения операции функции запроса согласно одной из особенностей настоящего изобретения.

ФИГ.14Б - один из вариантов осуществления блока, ответственного за операцию функции запроса, показанную на ФИГ. 14А, согласно одной из особенностей настоящего изобретения.

ФИГ.15A - один из вариантов осуществления блока запроса, используемого командой Call Logical Processor, показанной на ФИГ.13A, для выполнения групповой операции запроса согласно одной из особенностей настоящего изобретения.

ФИГ.15Б - один из вариантов осуществления блока ответа для групповой операции запроса, показанной на ФИГ.15A, согласно одной из особенностей настоящего изобретения.

ФИГ.16 иллюстрирует один вариант осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения.

ФИГ.17 иллюстрирует один вариант осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.18 иллюстрирует дополнительный пример компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.19 иллюстрирует другой пример компьютерной системы, содержащей компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.20 иллюстрирует один вариант осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.21A иллюстрирует один вариант осуществления исполнительного устройства компьютерной системы по ФИГ.20, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.21Б иллюстрирует один вариант осуществления устройства перехода компьютерной системы по ФИГ.20, в котором содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.21B - один из вариантов осуществления блока загрузки/сохранения проиллюстрированной на ФИГ.20, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ФИГ.22 иллюстрирует один вариант осуществления эмулированной хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

Согласно одной из особенностей настоящего изобретения предложена возможность управления скоростью, с которой обрабатываются запросы прерываний. Это управление включает изменение количества процессоров для выполнения обработки прерывания.

В одном из примеров для запроса прерывания адаптер посылает запрос на прерывание (MSI), инициируемое сообщениями. Затем запрос MSI преобразовывается в уведомление о событии адаптера ввода/вывода (I/O), в котором устанавливается один или несколько определенных указателей и осуществляется запрос на представление прерывания операционной системе (или другому программному обеспечению, такому как другие программы и т.д.). В контексте настоящего изобретения термин операционная система включает драйвера устройств операционной системы. В одном из вариантов осуществления множественные запросы прерывания (например, MSI) от одного или нескольких адаптеров объединяются в единичное прерывание для операционной системы, но с установкой соответственных указателей. Например, если концентратор ввода/вывода уже получил запрос MSI, предоставил в свою очередь запрос прерывания ЦП, и это прерывание все еще находится в режиме ожидания, тогда, если концентратор получает один или несколько других MSI, то ЦП не предоставляет дополнительное прерывание. Одно прерывание заменяет и представляет собой множество запросов MSI. Однако один или несколько указателей, связанных с каждым дополнительным запросом, все еще устанавливаются.

В ответ на представление прерывания операционной системе может быть представлено другое прерывание. Это прерывание может быть обработано, как тем же самым ЦП, так и другим ЦП. Таким образом, несколькими ЦП одновременно может обрабатываться несколько запросов.

Согласно одной из особенностей настоящего изобретения управление обеспечивается для замедления доставки запросов прерываний адаптера, поступающих от функций адаптера. Например, в ответ на представление прерывания адаптера операционной системе другие прерывания блокируются, но указатели устанавливаются соответственно этим заблокированным прерываниям. Блокировка продолжается до тех пор, пока, например, операционная система не определит, если вообще определит, что необходимы дополнительные процессоры (например, ЦП) для обработки указателей (например, если скорость прерываний адаптера превышает предопределенный порог). В качестве альтернативы, если были обработаны все указатели и операционная система завершила обработку их событий, тогда операционная система может определить, что блокировка более не является необходимой. В таком случае, поступление дополнительных прерываний снова разрешается.

Используемый в описании термин "адаптер" означает адаптер любого типа (например, адаптер памяти, сетевой адаптер, адаптер обработки, криптографический адаптер, адаптер на основе PCI, адаптеры ввода-вывода другого типа и т.д.). В одном из вариантов осуществления адаптер содержит одну функцию. Тем не менее, в других вариантах осуществления адаптер может содержать множество функций. В зависимости от того, содержит ли адаптер одну функцию или множество функций, применима одна или несколько особенностей настоящего изобретения. Кроме того, в представленных примерах термин адаптер используется взаимозаменяемо с термином функция адаптера (например, функция PCI), если не указано иное.

Далее будет описан один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения согласно ФИГ.1. В одном из примеров вычислительной средой 100 является сервер System z®, предлагаемый International Business Machines Corporation. Основой сервера System z® является z/Architecture®, предлагаемая International Business Machines Corporation. Подробности, касающиеся z/Architecture®, описаны в публикации IBM® под названием "z/Architecture-Principles of Operation", публикация IBM №SA22-7832-07 (февраль 2009 г.). IBM®, System z® и z/Architecture® являются зарегистрированными товарными знаками International Business Machines Corporation (Армонк, штат Нью-Йорк, США). Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний. В одном из примеров вычислительная среда 100 содержит один или несколько центральных процессоров (ЦП) 102, связанных с системной памятью 104 (иначе называемой основной памятью) посредством контроллера 106 памяти. Для доступа к системной памяти 104 центральный процессор 102 выдает запрос чтения или записи, в котором содержится адрес, используемый для доступа к системной памяти. Поскольку адрес, содержащийся в запросе, обычно не может непосредственно использоваться для доступа к системной памяти, он транслируется в адрес, который может непосредственно использоваться для доступа к системной памяти. Адрес транслируется посредством механизма 108 трансляции (XLATE). Например, адрес транслируется из виртуального адреса в действительный или абсолютный адрес с использованием, например, динамической трансляции адресов (DAT).

Запрос, содержащий транслированный адрес, принимается контроллером 106 памяти. В одном из примеров контроллер 106 памяти состоит из аппаратного обеспечения и используется для арбитража при доступе к системной памяти и для обеспечения непротиворечивости памяти. Этот арбитраж осуществляется применительно к запросам, принимаемым от ЦП 102, а также запросам, принимаемым от одного или нескольких адаптеров 110. Подобно центральным процессорам адаптеры выдают в системную память 104 запросы на получение доступа к системной памяти. В одном из примеров адаптером 110 является адаптер шины межсоединения периферийных компонентов (PCI) или адаптер на основе PCI Express (PCIe), содержащий одну или несколько функций PCI. Функция PCI выдает запрос, который маршрутизируется в концентратор 112 ввода-вывода (например, концентратор PCI) посредством одного или нескольких коммутаторов (например, коммутаторов PCIe) 114. В одном из примеров концентратор ввода-вывода состоит из аппаратного обеспечения, включающего один или несколько конечных автоматов.

Концентратор ввода-вывода содержит, например, корневой комплекс 116, который принимает запрос от коммутатора. В запросе содержится адрес ввода-вывода, используемый, например, для осуществления прямого доступа (DMA) к памяти или для запроса прерывания (MSI), инициируемого сообщениями. Этот адрес предоставляется блоку 118 трансляции и защиты адресов, который имеет доступ к информации, используемой как для DMA запроса, так и для запроса MSI.

При DMA операции блок 118 трансляции и защиты адресов может транслировать адрес адресу, используемому для получения доступа к системной памяти. Затем инициированный адаптером запрос, содержащий транслированный адрес, предоставляется контроллеру 106 памяти посредством, например, шины 120 "ввод-вывод - память". Контроллер памяти осуществляет арбитраж и в соответствующее время пересылает системной памяти запрос с транслированным адресом. При запросе MSI информация в блоке 118 трансляции и защиты адресов получается для облегчения преобразования запроса MSI в уведомление о событии адаптера ввода/вывода, как описано в данной публикации.

В еще одном из вариантов осуществления в дополнение к или вместо одного или нескольких центральных процессоров 102 центральный комплекс обработки данных, показанный на ФИГ.1Б, соединяется с контроллером 106 памяти. В этом конкретном примере центральный комплекс 150 обработки данных обеспечивает поддержку виртуальной машины. Центральный комплекс 150 обработки данных включает, например, одну или несколько виртуальных машин 152, один или несколько центральных процессоров 154 и, по меньшей мере, один гипервизор 156, каждый из которых описывается ниже.

Поддержка виртуальной машины центральным комплексом обработки данных обеспечивает способность работы с большим количеством виртуальных машин, каждая из которых может осуществлять выполнение гостевой операционной системы 158, такой как z/Linux. Каждая виртуальная машина 152 может работать в качестве отдельной системы. То есть, каждая виртуальная машина может независимо быть перезагружена, осуществлять выполнение гостевой операционной системы и работать с различными программами. Операционная система или прикладная программа, запущенная на виртуальной машине, может иметь доступ к полной и окончательной системе, но на практике доступной является только ее часть.

В этом конкретном примере моделью виртуальных машин является V=V модель, в которой память виртуальной машины обеспечивается виртуальной памятью, вместо реальной памяти. Каждая виртуальная машина имеет виртуальную линейную область в памяти. Физические ресурсы принадлежат гипервизору 156, например, VM гипервизору, и совместно используемые физические ресурсы, по мере необходимости, передаются гипервизором гостевым операционным системам для соблюдения их требований по обработке. Эта V=V модель виртуальной машины предполагает, что взаимодействия между гостевыми операционными системами и физическими совместно используемыми машинными ресурсами управляются VM гипервизором, поскольку большое количество гостей обычно препятствует разделению и назначению гипервизором ресурсов аппаратного обеспечения для настроенного гостя. Одна или несколько особенностей V=V модели также описываются в IBM публикации под названием "z/VM: Running Guest Operating Systems", IBM публикация No. SC24-5997-02, опубликованная в октябре 2001 года.

Центральные процессоры 154 являются ресурсами физического процессора, которые могут быть назначены для использования виртуальной машиной. Например, виртуальная машина 152 включает один или несколько логических процессоров, каждый из которых представляет собой все или часть ресурсов 154 физического процессора, которые могут быть динамически назначены для виртуальной машины. Виртуальные машины 152 управляются гипервизором 156. Например, гипервизор может быть реализован в аппаратно-программном обеспечении, работающем на процессорах 154, или может являться частью операционной хост-системы, выполняющейся на машине. В одном из примеров гипервизор 156 является VM гипервизором, таким как z/VM®, предоставленным International Business Machines Corporation, Армонк, Нью-Йорк. Один из вариантов осуществления z/VM® описывается в IBM публикации под названием "z/VM: General Information Manual", IBM публикация No. GC24-5991-05, опубликованная в мае 2003 года.

В контексте настоящего изобретения аппаратно-программное обеспечение содержит, например, микрокод, милликод и/или макрокод процессора. Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном варианте осуществления изобретения оно содержит, например, собственный код, который, как правило, поставляют как микрокод, который содержит выверенное программное обеспечение, или микрокод, характерный для базового аппаратного обеспечения, и управляет доступом операционной системы к аппаратному обеспечению системы.

Как показано на ФИГ.1A и 1Б, один или несколько адаптеров могут отправлять прерывания (MSI), инициируемые сообщениями. Эти прерывания преобразовываются в уведомления о событии адаптера ввода/вывода для одной или нескольких операционных систем, в которых устанавливаются указатели и запрашиваются одно или несколько прерываний. Операционная система может являться операционной системой, которая не является гостем или гостевой операционной системой, выполняющаяся хостом (например, z/VM®). Для облегчения этой обработки в концентраторе ввода/вывода и памяти используются различные структуры данных, как описывается со ссылкой на ФИГ.2А-2Б.

В частности, на ФИГ.2A проиллюстрирован один из вариантов осуществления структур, используемых для предоставления уведомления о событии адаптера операционной системе, которая не является гостевой, а на ФИГ.2Б проиллюстрирован один из вариантов осуществления структур, используемых для предоставления уведомления о событии адаптера гостю. Контроллер памяти на этих фигурах не показан, но может быть использован. Концентратор ввода/вывода может быть соединен с системной памятью и/или процессором 254 напрямую или через контроллер памяти. Как показано на ФИГ.2A, в одном из вариантов осуществления системная память 104 включает одну или несколько структур данных, используемых для облегчения обработки прерывания. В этом примере системная память 104 включает битовый вектор (AIBV) 200 прерывания адаптера и опциональный суммарный бит (AISB) 202 прерывания адаптера, связанные с конкретным адаптером. Для каждого адаптера может существовать AIBV и соответствующий AISB.

В одном из примеров битовый вектор 200 прерывания адаптера является одноразмерным рядом одного или нескольких указателей (например, битов) в основном запоминающем устройстве, которое связывается с адаптером (например, функцией PCI). Биты в битовом векторе прерывания адаптера представляют собой числа вектора MSI. Бит, равный единице, в AIBV указывает на условие или тип события для связанного адаптера. В одном из примеров функции PCI каждый бит в связанном AIBV соответствует вектору MSI. Следовательно, если функция PCI поддерживает только один вектор MSI, тогда AIBV включает единичный бит; если функция PCI поддерживает несколько векторов MSI, тогда AIBV включает по биту на каждый вектор MSI. В примере, проиллюстрированном на ФИГ.2A, функция PCI поддерживает несколько векторов MSI (например, 3) и, следовательно, в AIBV 200 находится несколько бит (например, 3). Каждый из битов соответствует конкретному событию, например, бит 0 AIBV при установке значения, равного единице, указывает на завершенную операцию; бит 1 AIBV при установке значения, равного единице, указывает на событие ошибки; и т.д. Как показано, в этом примере устанавливается бит 1.

В одном из конкретных примеров команда (например, команда Modify PCI Function Controls) используется для указания AIBV для функции PCI. А именно, команда, которая отправляется операционной системой и выполняется процессором, определяет подлинность функции PCI, ячейку основного запоминающего устройства области, которая включает AIBV, смещение из этой ячейки в первый бит AIBV и количество бит, которые включают AIBV. AIBV может находиться на любой байтовой границе или на любой битовой границе. Это обеспечивает гибкость операционной системы для упаковки AIBV нескольких адаптеров в непрерывный диапазон битов и байтов. В одном из примеров проверка подлинности функции PCI включается в обработку функции. Обработка функции включает, например, активацию указателя, который указывает на то, активирована ли обработка функции PCI; номер функции PCI, который определяет функцию (номер является статическим идентификатором и может быть использован в качестве индекса таблицы функции для размещения конкретной записи); и номер экземпляра, который указывает конкретный экземпляр этой обработки функции. Например, во время каждой из активации обработки функции номер экземпляра увеличивается для предоставления нового номера экземпляра. Обработка функции используется для размещения записи таблицы функции в таблице функции, которая включает одну или несколько записей. Например, один или несколько бит обработки функции используются в качестве индекса таблицы функции для размещения конкретной записи таблицы функции. Запись в таблице функций включает информацию о связанной с ней функции PCI. Например, она может включать различные указатели о состоянии связанной с ней функцией адаптера и один или несколько индексов записи таблицы устройства, использующиеся для размещения записей таблицы устройства для этой функции адаптера. Записи в таблице устройств включают информацию, используемую для предоставления определенных услуг соответствующим им функциям адаптера (например, трансляция адреса, обработка прерывания). (Что касается операционной системы, то в одном из вариантов осуществления обработка является обычным неясным идентификатором адаптера.) В этом примере в дополнение к AIBV для адаптера существует AISB 202, который включает единичный указатель (например, бит), связанный с адаптером. AISB, равный единице, указывает на то, что одному или нескольким битам в AIBV, связанном с AISB, было присвоено значение, равное единице. AISB является опциональным, по одному для каждого из адаптеров, по одному для каждого из выбранных адаптеров или по одному на группу адаптеров.

В одной из конкретных реализаций функций PCI команда (например, команда Modify PCI Functions Controls) используется для указания AISB для функции PCI. В частности, команда, которая отправляется операционной системой и выполняется процессором, определяет подлинность функции PCI (например, обработки), ячейку основного запоминающего устройства области, которая включает AISB, смещение из этой ячейки в первый бит AISB и управление возможностью короткого уведомления о прерывании адаптера, указывающее, что существует суммарный бит. AISB может находиться на любой байтовой границе или на любой битовой границе. Это обеспечивает гибкость операционной системы для упаковки AISB нескольких адаптеров в непрерывный диапазон битов и байтов.

Операционная система может назначать единичный AISB для нескольких функций PCI. Это действие связывает несколько AIBV с единичным суммарным битом. Следовательно, такой AISB, равняющийся единице, указывает на то, что операционная система должна осуществлять сканирование нескольких AIBV.

В одном из примеров AIBV и AISB указываются посредством адресов, расположенных в записи 206 таблицы устройства таблицы 208 устройства, расположенной в концентраторе 112 ввода/вывода. В одном из примеров таблица 208 устройства размещается внутри блока трансляции адреса и защиты концентратора ввода/вывода. Таблица 208 устройства включает одну или несколько записей 206, каждая из которых указывается для конкретной функции 210 адаптера. Запись 206 в таблице устройств включает количество полей, которое может быть заполнено, например, посредством вышеупомянутой команды. Значения одного или нескольких полей устанавливаются на основе политики и/или конфигурации. Примеры полей включают:

Подкласс 214 прерывания (ISC): Указывает подкласс прерывания для прерывания. ISC определяет маскируемый класс прерываний адаптера, которые могут быть связаны с приоритетом, с которым операционная система обрабатывает прерывание.

Адрес (@) 216 AIBV: Предоставляет, например, действительный адрес начала ячейки запоминающего устройства, который включает AIBV для конкретной функции адаптера, назначенной для этой записи таблицы устройства.

Сдвиг 218 AIBV: Сдвиг в ячейке основного запоминающего устройства в начало AIBV.

Адрес (@) 220 AISB: Предоставляет, например, действительный адрес начала ячейки запоминающего устройства, который включает AISB для этой функции PCI, если операционная система указала на AISB.

Сдвиг 222 AISB: Сдвиг в ячейке основного запоминающего устройства в AISB.

Управление (активация) 224 возможностью короткого уведомления о прерывании адаптера: Это управление указывает, имеется ли AISB.

Количество прерываний (N01) 226: Указывает максимальное количество векторов MSI, предоставленных для этой функции PCI, где ноль указывает на отказ от предоставления.

В других вариантах осуществления в DTE может содержаться больше, меньше информации или другая информация.

В одном из вариантов осуществления запись в таблице устройств, используемая для конкретного запроса прерывания посредством адаптера, расположена с использованием, например, идентификатора запросчика (RID) (и/или части адреса), содержащегося в запросе, выдаваемом адаптером (например, функцией 210 PCI). В запросе содержится идентификатор запросчика (например, 16-разрядное значение, указывающее, например, номер шины, номер устройства и номер функции), а также адрес для использования с целью доступа к прерыванию. Запрос, содержащий RID и адрес, выдается, например, посредством коммутатора, например, ассоциативной памяти (САМ 230), которая используется для получения значения индекса. Например, в САМ содержится множество записей, каждая из которых соответствует индексу в таблице устройств. Каждая запись в САМ содержит значение RID. Если, например, принятый RID соответствует значению, содержащемуся в записи в САМ, для определения местоположения записи в таблице устройств используется соответствующий индекс из таблицы устройств. Иными словами, выводимые из САМ данные используются для индексации в таблице 208 устройств. Если соответствие отсутствует, принятый пакет отбрасывается (в других вариантах осуществления не требуется САМ или другое средство поиска, и RID используется в качестве индекса). Содержащийся DTE используется при обработке запроса прерывания, как описывается в данной публикации.

В одном из конкретных вариантов, если запрос прерывания выполняется для гостя (например, гостем со страничной организацией режима записи в память; т.е., гостем V=V) в конкретной области или логическом разделе, тогда запись в таблице устройств также включает поле 228 области, как показано на ФИГ.2Б. Это поле указывает зону, к которой относится гость. В другом варианте осуществления это поле не используется или может быть использовано даже в случаях, если гости не предоставлены (например, для указания зоны или логического раздела, в котором запущена операционная система).

В одном из примеров в системе z/Architecture® посредством команды Start Interpretive Execution (SIE) в режиме интерпретации на уровне 2 выполняется гость со страничной организацией. Например, гипервизор логического разбиения (LPAR) выполняет команду SIE, чтобы начать логическое разбиение в физической постоянной памяти. Если операционной системой при этом логическом разбиении является z/VM®, она передает команду SIE для выполнения своих гостевых (виртуальных) машин в своем V=V (виртуальном) запоминающем устройстве. Соответственно, гипервизор LPAR использует SIE уровня 1, а гипервизор z/VM® использует SIE уровня 2.

Для облегчения обработки прерывания для гостей используются другие структуры данных, некоторые из которых сохраняются в хост-памяти 270, а другие - в гостевой памяти 271. Примеры этих структур описываются ниже.

В одном из примеров хост-память 270 включает, например, передающийся AISB ряд 272 и гостевую таблицу (GAIT) 274 прерываний адаптера. AISB ряд 272 переадресации - это ряд AISB, который используется в сочетании с гостевой таблицей прерываний адаптера для определения того, нацелен ли запрос MSI на гостевую операционную систему или на хост. AISB ряд переадресации включает AISB хост каждой функции PCI, который назначается гостю, и для которого хост, который является наполовину гостевым, запрашивает прерывание уведомления о событии адаптера. Такой ряд размещается в запоминающем устройстве хоста хостом гостя (например, z/VM®). Гостевая таблица 274 прерываний адаптера используется в сочетании с передающимся AISB рядом для определения того, нацелен ли запрос MSI на хост или на один из его гостей, и, если на гостя, то на какого именно. Соотношение между указателями (например, битами) равняется один к одному в передающемся AISB ряде и GAIT записях. Это означает, что, если бит в передающемся AISB ряду имеет значение, равное единице, и соответствующая GAIT информация содержит передающуюся информацию, то уведомление о событии адаптера находится в состоянии ожидания для адаптера для гостя, связанного с AISB указателем (например, битом) и соответствующей GAIT записью.

Если используется GAIT запись и она включает определенное значение (например, все нули), тогда целью запроса MSI является хост. Если используется GAIT запись, и она не содержит определенного значения, тогда целью запроса MSI является гость. Кроме того, если целью запроса MSI является гость, тогда GAIT запись включает следующую информацию, проиллюстрированную на ФИГ.2B: адрес хоста и сдвиг AISB гостя для функции 290 PCI; адрес хоста и гостевую область (GISA) 291 состояния прерывания; и гостевой подкласс (GISC) 292 прерываний для прерывания адаптера, генерируемого для гостя.

Следующие подробности о гостевой области (GISA) 276 состояния прерываний предоставляются со ссылкой на ФИГ.2Г. В одном из примеров GISA 276 является блоком управления, в котором прерывание гостевого адаптера находится в состоянии ожидания. Согласно одной из особенностей настоящего изобретения он включает, например, маску (SIMM) 277 режима единичного прерывания, которая является маской, имеющей по биту на каждый гостевой подкласс прерываний, и которая используется для указания того, что режим прерывания для подкласса является режимом единичного прерывания, как описывается ниже; маску (NIMM) 279 режима без прерываний, которая является маской, имеющей по биту на каждый гостевой подкласс прерывания, и которая ис