Аналого-цифровой преобразователь

Иллюстрации

Показать всеИзобретение относится к электронике и может быть использовано в микроэлектронных системах обработки аналоговых сигналов и преобразовании аналоговой информации в цифровую, в частности при разработке аналого-цифровых преобразователей (АЦП) с малым энергопотреблением, многоканальных системах приема и обработки информации с многоэлементных приемников оптического сигнала. Технический результат заявленного изобретения заключается в уменьшении площади кристалла АЦП и уменьшении потребляемой мощности за счет уменьшения суммарной емкости набора конденсаторов. Технический результат достигается за счет введения дополнительных блоков взвешивающих конденсаторов деления с ключами, аналогичных основному блоку взвешивающих конденсаторов деления с ключами, при этом емкость наименьшего конденсатора каждого дополнительного блока не равна удвоенной емкости наибольшего конденсатора основного блока или предыдущего дополнительного блока взвешивающих конденсаторов деления с ключами, а выходы дополнительных блоков взвешивающих конденсаторов деления с ключами объединены с выходом основного блока взвешивающих конденсаторов деления с ключами. 2 ил.

Реферат

Изобретение относится к электронике и может быть использовано в микроэлектронных системах обработки аналоговых сигналов и преобразовании аналоговой информации в цифровую, в частности при разработке аналого-цифровых преобразователей (АЦП) с малым энергопотреблением, многоканальных системах приема и обработки информации с многоэлементных приемников оптического сигнала.

Известен аналого-цифровой преобразователь последовательного приближения на перераспределении зарядов (Патент США №US 005675340 A М. Кл. H03M 1/12, опубликованный 7 апреля 1995 г.), состоящий из модуля n-битного цифроаналогового преобразователя (ЦАП) на перераспределении зарядов, управляемого регистром последовательного приближения, компаратора. Выходное напряжение ЦАП и входное напряжение АЦП поступают на компаратор, генерирующий управляющие воздействия для цифровой логики управления регистра последовательного приближения.

Основными недостатками описанного АЦП являются большая площадь кристалла и высокое энергопотребление вследствие большой суммарной емкости переключаемых конденсаторов.

Известен аналого-цифровой преобразователь последовательного приближения на перераспределении зарядов (Патент США №US 007893860 B2 М. Кл. H03M 1/12, опубликованный 27 мая 2009 г.), представляющий собой модуль преобразования, содержащий набор ключей и конденсаторов различной емкости, компаратор, модуль управления. Емкость каждого последующего конденсатора блока преобразования отличается от емкости предыдущего в два раза.

Основными недостатками описанного АЦП также являются большая площадь кристалла и высокое энергопотребление вследствие большой суммарной емкости переключаемых конденсаторов.

Так же известен аналого-цифровой преобразователь последовательного приближения (F. Lei Gao et al., "A low-power SAR ADC for IRFPA ROIC", Infrared, Millimeter-Wave, and Terahertz Technologies II, Proceedings of SPIE Vol.8562, 2012), состоящий из ЦАП, компаратора и схемы цифрового управления. ЦАП работает по принципу перераспределения зарядов с масштабированием заряда и напряжения и состоит из блока двоично-взвешенных конденсаторов с ключами и блока резистивных делителей, формирующего из внешнего опорного напряжения множество равных поддиапазонов. Выходное напряжение ЦАП и входное напряжение АЦП поступают на компаратор, генерирующий управляющие воздействия для цифровой логики управления регистра последовательного приближения. Преобразование выполняется в две стадии. На первой стадии при помощи блока двоично-взвешенных конденсаторов с ключами и внешнего опорного напряжения определяются старшие разряды, а также поддиапазон резистивного делителя, соответствующий входному напряжению АЦП. Младшие разряды определяются на второй стадии при помощи того же блока двоично-взвешенных конденсаторов с ключами. При этом в качестве опорных используются напряжения соответствующего поддиапазона резистивного делителя.

Основными недостатками данного АЦП являются большая площадь кристалла и высокое энергопотребление вследствие большой суммарной емкости переключаемых конденсаторов. Задание рабочего диапазона напряжений при помощи матрицы резистивных делителей напряжения приводит к понижению температурной стабильности схемы.

Известен аналого-цифровой преобразователь последовательного приближения (Г.И. Волович «Схемотехника аналоговых и аналого-цифровых электронных устройств», издательский дом «Додэка-XXI», Москва, 2005 г., стр.444, рис.9.11), состоящий из цифровой схемы управления, вход которой соединен с выходом компаратора напряжений, один вход которого является входом аналого-цифрового преобразователя, а другой соединен с выходом цифроаналогового преобразователя, состоящего из операционного усилителя с замыкаемым ключом конденсатором в отрицательной обратной связи, не инвертирующий вход которого подключен к входу общего опорного напряжения, а инвертирующий вход соединен с выходом основного блока взвешивающих конденсаторов деления с ключами, представляющего собой набор конденсаторов, емкости которых соотносятся как целые степени двух, первая обкладка каждого из которых соединяется с выходом основного блока, и двухпозиционных ключей, выход каждого из которых соединен со второй обкладкой соответствующего ключу конденсатора, первый вход каждого ключа подключен к входу общего опорного напряжения, второй вход каждого ключа подключен к входу опорного напряжения, а вход управления ключа соединен с соответствующим выходом цифровой схемы управления.

Данное устройство является ближайшим к предлагаемому техническому решению.

АЦП работает следующим образом. В начальный момент времени цифровая схема управления принудительно задает на вход ЦАП код, соответствующий половине его шкалы. Эта величина составляет половину возможного диапазона преобразуемых сигналов АЦП. Если входное напряжение больше, чем эта величина, то на выходе компаратора устанавливается логическая единица, если меньше, то логический ноль. В последнем случае схема управления должна переключить старший разряд обратно в состояние нуля. Непосредственно вслед за этим, остаток, таким же образом, сравнивается с ближайшим младшим разрядом. После всех подобных выравнивающих шагов в регистре последовательного приближения оказывается двоичное число, из которого после цифроаналогового преобразования получается напряжение, соответствующее входному преобразуемому напряжению с точностью до младшего разряда. Выходное число может быть считано с цифровой схемы управления в виде параллельного двоичного кода.

Основными недостатками описанного АЦП являются большая площадь кристалла и высокое энергопотребление. Действительно, основой АЦП является ЦАП на коммутируемых конденсаторах с суммированием заряда, содержащий набор конденсаторов, емкости которых соотносятся как целые степени двух (Г.И. Волович «Схемотехника аналоговых и аналого-цифровых электронных устройств», издательский дом «Додэка-XXI», Москва, 2005 г., стр.400, рис.8.16). Для увеличения разрядности АЦП на один бит требуется удвоение суммарной емкости набора конденсаторов и, соответственно, занимаемой ими площади на кристалле. Большая суммарная емкость набора конденсаторов приводит к большому суммарному заряду, необходимому для их зарядки и разрядки, а следовательно, и большой потребляемой мощности.

Техническим результатом изобретения является уменьшение площади кристалла АЦП, а также уменьшение потребляемой мощности.

Технический результат достигается тем, что аналого-цифровой преобразователь, состоящий из цифровой схемы управления, вход которой соединен с выходом компаратора напряжений, один вход которого является входом аналого-цифрового преобразователя, а другой вход соединяется с выходом цифроаналогового преобразователя, состоящего из операционного усилителя с замыкаемым ключом конденсатором в отрицательной обратной связи, не инвертирующий вход которого подключен к входу общего опорного напряжения, а инвертирующий вход подключен к выходу основного блока взвешивающих конденсаторов деления с ключами, представляющего собой набор конденсаторов, причем емкость каждого следующего конденсатора равна удвоенной емкости предыдущего, первая обкладка каждого конденсатора соединяется с выходом основного блока, а вторая обкладка с выходом соответствующего конденсатору двухпозиционного ключа, первый вход каждого ключа соединен со входом общего опорного напряжения, второй вход каждого ключа соединен со входом опорного напряжения основного блока, а вход управления ключа соединяется с соответствующим выходом цифровой схемы управления, при этом преобразователь содержит дополнительные блоки взвешивающих конденсаторов деления с ключами, аналогичных основному блоку взвешивающих конденсаторов деления с ключами, при этом емкость наименьшего конденсатора каждого дополнительного блока не равна удвоенной емкости наибольшего конденсатора основного блока или предыдущего дополнительного блока взвешивающих конденсаторов деления с ключами, а выходы дополнительных блоков взвешивающих конденсаторов деления с ключами объединены с выходом основного блока взвешивающих конденсаторов деления с ключами.

Технических решений, содержащих признаки, сходные с отличительными, не выявлено, что позволяет сделать вывод о соответствии заявляемого технического решения критерию "новизна".

Предлагаемый преобразователь имеет существенное отличие от прототипа. Существенным отличием является то, что преобразователь содержит дополнительные блоки, каждый из которых представляет собой набор из конденсаторов, емкости которых в пределах дополнительного блока соотносятся как целые степени двух, первая обкладка каждого из которых соединяется с выходом дополнительного блока, и двухпозиционных ключей, выход каждого из которых соединен со второй обкладкой соответствующего ключу конденсатора, первый вход каждого ключа соединен со входом общего опорного напряжения, второй вход каждого ключа соединен со входом дополнительного опорного напряжения дополнительного блока, а вход управления ключа соединяется с соответствующим выходом цифровой схемы управления, причем выходы дополнительных блоков взвешивающих конденсаторов деления с ключами объединены с выходом основного блока взвешивающих конденсаторов деления с ключами, а величина дополнительного опорного напряжения V r e f p дополнительного p-го блока определяется выражением:

V r e f p = V c o m − C о с ⋅ ( V c o m − V r e f 0 ) C 1 p ⋅ 2 ( 1 + H ) , г д е ( 1 )

p - номер дополнительного блока, 1≤p≤m;

m - количество дополнительных блоков;

Vcom - общее опорное напряжение;

Coc- емкость конденсатора обратной связи;

V r e f 0 - опорное напряжение основного блока взвешивающих конденсаторов деления с ключами;

i0 - количество конденсаторов в основном блоке взвешивающих конденсаторов деления с ключами;

ip - количество конденсаторов в p-м дополнительном блоке;

C1p - емкость наибольшего конденсатора p-го дополнительного блока;

H - суммарное количество конденсаторов в основном блоке взвешивающих конденсаторов деления с ключами и в дополнительных блоках до p-го включительно;

Основой АЦП является ЦАП на коммутируемых конденсаторах с суммированием заряда, содержащий набор конденсаторов, емкости которых соотносятся как целые степени двух. Так как минимальная емкость взвешивающего конденсатора ограничена рядом физических и технологических параметров, ранее для увеличения разрядности АЦП на один бит требовалось удвоение суммарной емкости набора конденсаторов и, соответственно, занимаемой ими площади на кристалле. Большая суммарная емкость набора конденсаторов приводила к большому суммарному току, необходимому для их зарядки и разрядки, а следовательно, и большой потребляемой мощности. Уменьшение занимаемой площади и потребляемой мощности достигается следующим образом. Работа ЦАП основана на перераспределении зарядов, а заряд k-го конденсатора определяется выражением qk=Ck·(Vcom-Vref). В предлагаемом преобразователе тот же заряд при меньшей емкости конденсатора достигается путем уменьшения соответствующего опорного напряжения Vref.

Тем самым, новая совокупность признаков позволяет сделать заключение о соответствии заявляемого технического решения критерию "изобретательский уровень".

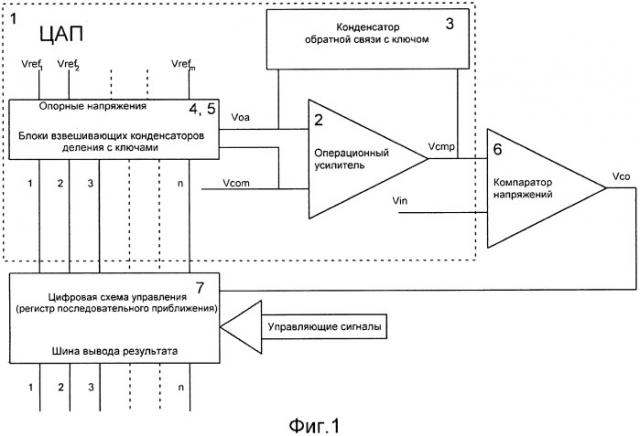

На фиг.1 представлена структурная схема заявляемого n-битного АЦП последовательного приближения.

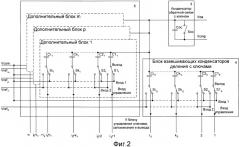

На фиг.2 представлена структурная схема блоков взвешивающих конденсаторов деления с ключами ЦАП на перераспределении зарядов.

На фиг.1 и 2 изображено: 1 - цифроаналоговый преобразователь, 2 - операционный усилитель, 3 - конденсатор обратной связи с ключом, Coc - конденсатор обратной связи, Soc - ключ конденсатора обратной связи, 4 - основной блок взвешивающих конденсаторов деления с ключами, C10…Ck0…Ci0 - взвешивающие конденсаторы деления, при этом емкость k-го конденсатора определяется выражением C k 0 = C о с 2 k , где 1≤k≤i0, S10…Sk0…Si0 - ключи взвешивающих конденсаторов деления, 5 - дополнительные блоки взвешивающих конденсаторов деления с ключами, C11, C21…Ck1…Ci1 - взвешивающие конденсаторы деления первого дополнительного блока, при этом емкость k-го конденсатора определяется выражением C k 1 = C 1 1 2 k - 1 где 1≤k≤i1, а i1 - количество конденсаторов в первом дополнительном блоке, S11…Sk1…Si1 - ключи взвешивающих конденсаторов деления, 6 - компаратор напряжений, 7 - цифровая схема управления.

Как показано на фиг.1 и 2, вход цифровой схемы управления 7 соединен с выходом Vco компаратора 6, на один вход которого подается входное преобразуемое напряжение Vin, а на другой - напряжение с выхода Vcmp цифроаналогового преобразователя 1, состоящего из операционного усилителя 2 с замыкаемым ключом конденсатором в отрицательной обратной связи 3, на не инвертирующий вход которого подается общее опорное напряжение Vcom, а на инвертирующий вход подается сигнал с выхода основного блока взвешивающих конденсаторов деления с ключами Voa, представляющего собой набор из конденсаторов C10…Ck0…Ci0, емкости которых соотносятся как целые степени двух, первая обкладка каждого из которых соединяется с выходом блока, и двухпозиционных ключей S10…Sk0…Si0, выход каждого из которых соединен со второй обкладкой соответствующего ключу конденсатора, на первый вход каждого ключа подается общее опорное напряжение Vcom, на второй вход каждого ключа подается опорное напряжение V r e f 0 , а на вход управления ключа поступает сигнал с соответствующего выхода цифровой схемы управления 7, также цифроаналоговый преобразователь содержит m дополнительных блоков 5, каждый из которых представляет собой набор из конденсаторов C1p…Ckp…Cip, емкости которых в пределах дополнительного блока соотносятся как целые степени двух, первая обкладка каждого из которых соединяется с выходом дополнительного блока, и двухпозиционных ключей S1p…Skp…Sip, выход каждого из которых соединен со второй обкладкой соответствующего ключу конденсатора, на первый вход каждого ключа подается общее опорное напряжение Vcom, на второй вход каждого ключа подается дополнительное опорное напряжение дополнительного блока V r e f p , а на вход управления ключа поступает сигнал с соответствующего выхода цифровой схемы управления 7, причем выходы дополнительных блоков взвешивающих конденсаторов деления с ключами объединены с выходом основного блока взвешивающих конденсаторов деления с ключами Voa, а величина дополнительного опорного напряжения V r e f p дополнительного p-го блока определяется выражением 1.

В случае идентичных основного блока взвешивающих конденсаторов деления с ключами и дополнительных блоков взвешивающих конденсаторов деления с ключами, количество конденсаторов в каждом блоке i=i0=ip При емкости Coc=2×C1p устройство работает следующим образом. При диапазоне входных преобразуемых напряжений АЦП от Vmin до Vmax, на входы опорных напряжений АЦП подаются опорные напряжения:

Vcom=Vmin - общее опорное напряжение;

V r e f 0 = V m i n − V m a x − V m i n 2 0 - опорное напряжение основного блока взвешивающих конденсаторов деления с ключами;

V r e f 1 = V m i n − V m a x − V m i n 2 i - дополнительное опорное напряжение первого дополнительного блока конденсаторов;

V r e f 2 = V m i n − V m a x − V m i n 2 2 ⋅ i - дополнительное опорное напряжение второго дополнительного блока конденсаторов;

V r e f p = V m i n − V m a x − V m i n 2 i ⋅ p - дополнительное опорное напряжение p-го дополнительного блока конденсаторов.

На вход Vin компаратора 6 подается входное преобразуемое напряжение.

В начальный момент времени цифровая схема управления принудительно задает на вход ЦАП код, соответствующий половине его шкалы. Эта величина составляет половину возможного диапазона преобразуемых сигналов АЦП. Если входное напряжение больше, чем эта величина, то на выходе компаратора устанавливается логическая единица, если меньше, то логический ноль. В последнем случае схема управления должна переключить старший разряд обратно в состояние нуля. Непосредственно вслед за этим остаток таким же образом сравнивается с ближайшим младшим разрядом. После всех подобных выравнивающих шагов в регистре последовательного приближения оказывается двоичное число, из которого после цифроаналогового преобразования получается напряжение, соответствующее входному преобразуемому напряжению с точностью до младшего разряда. Выходное число может быть считано с цифровой схемы управления в виде параллельного двоичного кода.

Эталонное напряжение на выходе ЦАП генерируется следующим образом. Преобразование состоит из двух фаз. В первой фазе ключи S1…Si всех блоков находятся в положении 1, замыкая выход с входом 1 и подключая нижнюю обкладку конденсатора к источнику общего опорного напряжения Vcom. Ключ Soc замкнут. Во второй фазе ключ Soc размыкается, и если k-й бит dk входного i-разрядного слова на входе управления k-го ключа принимает значение логической "1", то соответствующий ключ Sk переключается в положение 2, замыкая выход с входом 2 и подключая нижнюю обкладку конденсатора к источнику дополнительного опорного напряжения V r e f p , или остается в положении 1, если dk принимает значение логического "0". Суммарный заряд конденсаторов р-го блока составит:

q p = ( V c o m − V r e f p ) ⋅ ∑ k = 1 i p C k p ⋅ d k p , ( 2 )

а напряжение на выходе ЦАП составит:

V c m p = V c o m + ∑ p = 0 m q p C о с .

Преимущества предлагаемого технического решения по сравнению с прототипом заключаются в уменьшение площади кристалла и энергопотребления за счет уменьшения суммарной емкости блоков переключаемых конденсаторов. Данное улучшение достигается путем ввода дополнительных блоков взвешивающих конденсаторов деления с ключами с дополнительными опорными напряжениями.

При одинаковой доступной площади кристалла, по сравнению с прототипом, предложенный АЦП можно легко масштабировать, что позволяет в разы увеличить разрядность, а соответственно и точность преобразования.

Поскольку минимальный размер конденсатора ограничен рядом параметров, как физических, так и технологических, для получения требуемого числа разрядов в подобных ЦАП и АЦП обычной практикой является увеличение емкости конденсатора обратной связи и добавление взвешенных конденсаторов большей емкости. Так как генерация эталонного напряжения на выходе ЦАП для сравнения с входным преобразуемым напряжением происходит при помощи перераспределения заряда на взвешенных конденсаторах, для получения минимального кванта заряда можно прибегнуть не только к уменьшению емкостей конденсаторов, но и соответствующих опорных напряжений, заряжающих конденсаторы.

Пример предлагаемого решения. Имеется n-разрядный преобразователь по схеме прототипа и нам необходимо создать (n+1) разрядное АЦП. Минимальная емкость Cmin в наборе взвешенных конденсаторов определяется используемой технологией и не может быть уменьшена. Следовательно, по схеме прототипа, (n+1) разряд АЦП можно получить, добавив к набору взвешенных конденсаторов емкость величиной Cmin·2n+1 , иначе говоря, удвоив суммарную емкость конденсаторов. В предлагаемой схеме можно ввести в исходную схему дополнительный блок взвешенных конденсаторов с ключами, состоящий лишь из одного конденсатора минимальной емкости Cmin, и подать на этот дополнительный блок дополнительное опорное напряжение вполовину величины опорного напряжения. Тем самым ЦАП будет в состоянии формировать уменьшенные в 2 раза напряжения, чем и достигается увеличение разрядности АЦП. Однако при этом суммарная емкость конденсаторов и занимаемая ими площадь практически не изменится.

Емкости минимальных конденсаторов различных дополнительных блоков могут и отличаться, однако должно выполняться соотношение зарядов конденсаторов:

q i p = 2 ⋅ q 1 p + 1 , где:

q i p - заряд i-го (наименьшего) конденсатора р-го дополнительного блока;

q 1 p + 1 - заряд первого (наибольшего) конденсатора р+1-го дополнительного блока.

При этом q i p определяется выражением q i p = C i p ⋅ ( V c o m − V r e f p ) , из которого следует выражение 2, и означающее, что заряд, формируемый на наименьшей емкости предыдущего блока, должен быть в два раза больше заряда, формируемого на наибольшем конденсаторе последующего блока.

В случае не идентичных блоков появляется дополнительная возможность оптимизации схемы по количеству и структуре каждого дополнительного блока в зависимости от параметров используемой технологии и возможности внешних устройств задания множества опорных напряжений необходимой точности.

В случае многоканального АЦП, устройство задания множества опорных напряжений может быть одно для всех каналов.

Аналого-цифровой преобразователь, состоящий из цифровой схемы управления, вход которой соединен с выходом компаратора напряжений, один вход которого является входом аналого-цифрового преобразователя, а другой вход соединяется с выходом цифроаналогового преобразователя, состоящего из операционного усилителя с замыкаемым ключом конденсатором в отрицательной обратной связи, не инвертирующий вход которого подключен к входу общего опорного напряжения, а инвертирующий вход подключен к выходу основного блока взвешивающих конденсаторов деления с ключами, представляющего собой набор конденсаторов, причем емкость каждого следующего конденсатора равна удвоенной емкости предыдущего, первая обкладка каждого конденсатора соединяется с выходом основного блока, а вторая обкладка с выходом соответствующего конденсатору двухпозиционного ключа, первый вход каждого ключа соединен со входом общего опорного напряжения, второй вход каждого ключа соединен со входом опорного напряжения основного блока, а вход управления ключа соединяется с соответствующим выходом цифровой схемы управления, отличающийся тем, что в него введены дополнительные блоки взвешивающих конденсаторов деления с ключами, аналогичных основному блоку взвешивающих конденсаторов деления с ключами, при этом емкость наименьшего конденсатора каждого дополнительного блока не равна удвоенной емкости наибольшего конденсатора основного блока или предыдущего дополнительного блока взвешивающих конденсаторов деления с ключами, а выходы дополнительных блоков взвешивающих конденсаторов деления с ключами объединены с выходом основного блока взвешивающих конденсаторов деления с ключами.