Устройство синхронного приема двоичной информации по дублирующим каналам связи

Иллюстрации

Показать всеИзобретение относится к области связи и вычислительной технике и может быть использовано в устройствах передачи данных. Техническим результатом является повышение надежности. Устройство содержит блоки повышения достоверности, накопители информации, блоки ключей, элементы ИЛИ-НЕ, сумматор по модулю два, блок выдачи информации, элементы И и ИЛИ, блок статистического контроля, содержащий триггеры, счетчики, элементы И, ИЛИ, НЕ, светодиоды, формирователь одиночного импульса. 3 ил.

Реферат

Изобретение относится к технике связи и вычислительной технике и может быть использовано в аппаратуре передачи данных.

Известно устройство для приема информации по двум параллельным каналам связи [авторское свидетельство СССР №590856, кл. H04L 1/16 за 1976 г.], содержащее входной элемент И, входной элемент ИЛИ, блоки защиты от ошибок, информационные вход и выход и выход сигнала переспроса. Недостатком этого устройства является относительно невысокое качество приема информации с значительным переспросом информации и снижением пропускной способности каналов.

Наиболее близким к предлагаемому изобретению является устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью [патент №473314 на одноименное изобретение по МПК H04L 1/16 от 14.06.1972 г., бюл. №21 от 05.06.1975 г.], содержащее первый и второй блоки повышения достоверности, первый и второй накопители информации, первый и второй блоки ключей, первый и второй элементы ИЛИ-НЕ, сумматор по модулю два, блок выдачи информации, первые элементы И и ИЛИ, а также первый и второй информационные входы, информационный выход и выход переспроса, при этом первый и второй информационные входы, представляющие собой информационные входы приема двоичной информации последовательным кодом первого и второго каналов, соединены соответственно с информационными входами первого и второго накопителя и параллельно с соответствующими входами сумматора по модулю два, группа выходов первого накопителя поразрядно соединена с группой входов первого блока повышения достоверности и с группой входов первого блока ключей, группа выходов которого поразрядно соединена с первой группой входов блока выдачи информации, группа выходов которого является информационным выходом устройства, группа выходов второго накопителя поразрядно соединена с группой входов второго блока повышения достоверности и с группой входов второго блока ключей, группа выходов которого поразрядно соединена со второй группой входов блока выдачи информации, выход сигнала отбраковки первого блока повышения достоверности соединен с первыми входами первых элементов И и ИЛИ-НЕ, а выход сигнала отбраковки второго блока повышения достоверности соединен со вторым входом первого элемента И и первым входом второго элемента ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторыми входами первого и второго элементов ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен с входом управления первого блока ключей, выход второго элемента ИЛИ-НЕ соединен с входом управления второго блока ключей и третьим входом первого элемента ИЛИ-НЕ.

К недостаткам известного устройства следует отнести то, что оно не защищено от зацикливания при переспросе информации при некоторых устойчивых неисправностях в нем или в каналах связи, а также при некоторых устойчивых искажениях самой информации, в нем отсутствуют четкая синхронизация приема и своевременного анализа информации и поэтому известное устройство требует дополнительного творчества для обеспечения его работоспособности.

Техническим результатом и целью заявляемого устройства является устранение указанных выше недостатков прототипа - исключение ситуаций его зацикливания в связи с переспросом информации путем статистического выявления по критерию устойчивых неисправностей, приводящих к бессмысленному и бесконечному переспросу, с индикацией для обслуживающего персонала факта неисправности устройства, а также обеспечение работоспособности устройства путем согласования работы его составных частей с помощью введенных в него регламентных сигналов синхронизации.

Указанный технический результат и цель достигаются тем, что устройство, содержащее первый и второй блоки повышения достоверности, первый и второй накопители информации, первый и второй блоки ключей, первый и второй элементы ИЛИ-НЕ, сумматор по модулю два, блок выдачи информации, первые элементы И и ИЛИ, а также первый и второй информационные входы, информационный выход и выход переспроса, при этом первый и второй информационные входы, представляющие собой информационные входы приема двоичной информации последовательным кодом первого и второго каналов, соединены соответственно с информационными входами первого и второго накопителя и параллельно с соответствующими входами сумматора по модулю два, группа выходов первого накопителя поразрядно соединена с группой входов первого блока повышения достоверности и с группой входов первого блока ключей, группа выходов которого поразрядно соединена с первой группой входов блока выдачи информации, группа выходов которого является информационным выходом устройства, группа выходов второго накопителя поразрядно соединена с группой входов второго блока повышения достоверности и с группой входов второго блока ключей, группа выходов которого поразрядно соединена со второй группой входов блока выдачи информации, выход сигнала отбраковки первого блока повышения достоверности соединен с первыми входами первых элементов И и ИЛИ-НЕ, а выход сигнала отбраковки второго блока повышения достоверности соединен со вторым входом первого элемента И и первым входом второго элемента ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторыми входами первого и второго элементов ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен с входом управления первого блока ключей, выход второго элемента ИЛИ-НЕ соединен с входом управления второго блока ключей и третьим входом первого элемента ИЛИ-НЕ, дополнительно содержит блок статистического контроля в составе триггеров окна контроля, сбоя по модулю два, неисправности устройства, неисправности первого канала и неисправности второго канала, счетчиков приема сообщений, переспроса, отбраковки первого и второго каналов, второго, третьего и четвертого элементов И, второго, третьего и четвертого элементов ИЛИ, первого и второго элементов НЕ, светодиодов неисправности устройства, первого и второго каналов, формирователя одиночного импульса, входов импульсов синхронизации, старт, стоп и плюсовой и минусовой входы шины питания, при этом вход импульсов синхронизации соединен с первым входом второго элемента И, второй и третий входы которого соединены соответственно с выходом сумматора по модулю два и прямым выходом триггера окна контроля, а выход которого соединен с входом установки в единицу триггера сбоя по модулю два, прямой выход которого соединен с первым входом третьего элемента И, второй и третий входы которого соединены через первый и второй элементы НЕ соответственно с выходами сигнала отбраковки первого и второго блоков повышения достоверности, а выход которого соединен со вторым входом первого элемента ИЛИ, вход старт соединен с входом установки в единицу триггера окна контроля, вход установки в ноль которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с входами стоп, +1 счетчика приема сообщений, опроса первого и второго блоков повышения достоверности, считывания блока выдачи информации и первым входом четвертого элемента И, второй и третий входы которого соединены соответственно с выходом первого элемента ИЛИ и инверсным выходом триггера неисправности, а выход которого соединен с первым входом третьего элемента ИЛИ, входом +1 счетчика переспроса и выходом переспроса устройства, входы +1 счетчика отбраковки первого канала и счетчика отбраковки второго канала соединены соответственно с выходами сигнала отбраковки первого и второго блоков повышения достоверности, выходы переполнения счетчика приема сообщений, счетчика переспроса, счетчика отбраковки первого канала и счетчика отбраковки второго канала соединены соответственно с первым входом четвертого элемента ИЛИ, с входами установки в единицу триггеров неисправности устройства, первого канала и второго канала, прямые выходы триггеров неисправности устройства, первого канала и второго канала соединены через соответствующие светодиоды с минусовым входом шины питания устройства, входы установки в ноль счетчиков переспроса, отбраковки первого канала и второго канала и триггеров первого канала и второго канала соединены с выходом четвертого элемента ИЛИ, второй вход которого соединен с входами установки в ноль триггера неисправности устройства и счетчика приема сообщений, со вторыми входами второго и третьего элементов ИЛИ и выходом формирователя одиночного импульса, вход которого соединен с плюсовым входом шины питания устройства.

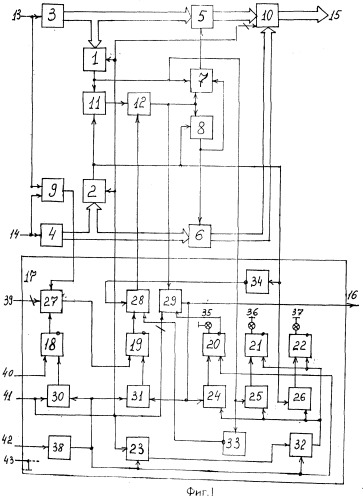

На фиг.1-3 представлены электрическая структурная схема устройства и временная диаграмма его работы.

Устройство содержит первый 1 и второй 2 блоки повышения достоверности, первый 3 и второй 4 накопители информации, первый 5 и второй 6 блоки ключей, первый 7 и второй 8 элементы ИЛИ-НЕ, сумматор 9 по модулю два, блок 10 выдачи информации, первые элементы 11 и 12 И и ИЛИ, а также первый 13 и второй 14 информационные входы, информационный выход 15 и выход 16 переспроса, блок 17 статистического контроля в составе триггеров 18, …, 22 окна контроля, сбоя по модулю два, неисправности устройства, неисправности первого канала и неисправности второго канала, счетчиков 23, …, 26 приема сообщений, переспроса, отбраковки первого и второго каналов, второго 27, третьего 28 и четвертого 29 элементов И, второго 30, третьего 31 и четвертого 32 элементов ИЛИ, первого 33 и второго 34 элементов НЕ, светодиодов 35, 36, 37 неисправности устройства, первого и второго каналов, формирователя 38 одиночного импульса, входов 39, …, 41 импульсов синхронизации, старт, стоп и плюсовой вход 42 и минусовой вход 43 шины питания.

Первый 13 и второй 14 информационные входы, представляющие собой информационные входы приема двоичной информации последовательным кодом первого и второго каналов, соединены соответственно с информационными входами первого 3 и второго 4 накопителя и параллельно с соответствующими входами сумматора 9 по модулю два, группа выходов первого накопителя 3 поразрядно соединена с группой входов первого блока 1 повышения достоверности и с группой входов первого блока 5 ключей, группа выходов которого поразрядно соединена с первой группой входов блока 10 выдачи информации, группа выходов которого является информационным выходом 15 устройства, группа выходов второго накопителя 4 поразрядно соединена с группой входов второго блока 2 повышения достоверности и с группой входов второго блока 6 ключей, группа выходов которого поразрядно соединена со второй группой входов блока 10 выдачи информации, выход сигнала отбраковки первого блока 1 повышения достоверности соединен с первыми входами первых элементов 11 И и 7 ИЛИ-НЕ, а выход сигнала отбраковки второго блока 2 повышения достоверности соединен со вторым входом первого элемента 11 И и первым входом второго элемента 8 ИЛИ-НЕ, выход первого элемента 11 И соединен с первым входом первого элемента 12 ИЛИ, выход которого соединен со вторыми входами первого 7 и второго 8 элементов ИЛИ-НЕ, выход первого элемента 7 ИЛИ-НЕ соединен с входом управления первого блока 5 ключей, выход второго элемента 8 ИЛИ-НЕ соединен с входом управления второго блока 6 ключей и третьим входом первого элемента 7 ИЛИ-НЕ, вход 39 импульсов синхронизации соединен с первым входом второго элемента 27 И, второй и третий входы которого соединены соответственно с выходом сумматора 9 по модулю два и прямым выходом триггера 18 окна контроля, а выход которого соединен с входом установки в единицу триггера 19 сбоя по модулю два, прямой выход которого соединен с первым входом третьего элемента 28 И, второй и третий входы которого соединены через первый 33 и второй 34 элементы НЕ соответственно с выходами сигнала отбраковки первого 1 и второго 2 блоков повышения достоверности, а выход которого соединен со вторым входом первого элемента 12 ИЛИ, вход 40 старт соединен с входом установки в единицу триггера 18 окна контроля, вход установки в ноль которого соединен с выходом второго элемента 30 ИЛИ, первый вход которого соединен с входами 41 стоп, +1 счетчика 23 приема сообщений, опроса первого 1 и второго 2 блоков повышения достоверности и считывания блока 10 выдачи информации и первым входом четвертого элемента 29 И, второй и третий входы которого соединены соответственно с выходом первого элемента 12 ИЛИ и инверсным выходом триггера 20 неисправности устройства, а выход которого соединен с первым входом третьего элемента 31 ИЛИ, входом +1 счетчика 24 переспроса и выходом 16 переспроса устройства, входы +1 счетчика 25 отбраковки первого канала и счетчика 26 отбраковки второго канала соединены соответственно с выходами сигнала отбраковки первого 1 и второго 2 блоков повышения достоверности, выходы переполнения счетчика 23 приема сообщений, счетчика 24 переспроса, счетчика 25 отбраковки первого канала и счетчика 26 отбраковки второго канала соединены соответственно с первым входом четвертого элемента 32 ИЛИ, с входами установки в единицу триггера неисправности 20 устройства, триггера 21 первого канала и триггера 22 второго канала, прямые выходы которых соединены через соответствующие светодиоды 35, 36, 37 с минусовым входом 43 шины питания устройства, входы установки в ноль счетчиков 24, 25, 26 переспроса, отбраковки первого канала и второго канала и триггеров 21 и 22 неисправности первого канала и второго канала соединены с выходом четвертого элемента 32 ИЛИ, второй вход которого соединен с входами установки в ноль триггера 20 неисправности устройства и счетчика 23 приема сообщений, со вторыми входами второго 30 и третьего 31 элементов ИЛИ и выходом формирователя 38 одиночного импульса, вход которого соединен с плюсовым входом 42 шины питания устройства, выход третьего элемента 31 ИЛИ соединен со входом установки в ноль триггера 19 сбоя по модулю два.

В устройстве использованы элементы широкого применения, точнее - широко используемая двоичная логика, которая легко реализуется с помощью практически любой серии интегральных микросхем.

Устройство работает следующим образом.

В составе первого 13 и второго 14 (фиг.1) каналов связи, кроме основных информационных цепей, входят служебные цепи, по которым передаются служебные сигналы, такие как синхроимпульсы (СИ) 39, СТАРТ 40, СТОП 41, переспрос 16. Вопросы специфики работы каналов и их интерфейс выходят за рамки настоящей заявки и поэтому здесь не рассматриваются. Однако для понимания сути изобретения ниже использованы служебные сигналы СИ, СТАРТ и СТОП, характерные для некоторых синхронных интерфейсов. При этом каждый бит передаваемой последовательным кодом через информационные входы 13 и 14 двоичной информации сопровождается соответствующим СИ, передний фронт которого совпадает с серединой этого бита информации.

Пусть, например, по первому 13 и второму 14 каналам связи, работающим в режиме дублирования, одновременно передаются сообщения байтами с двумя контрольными разрядами по модулю три, то есть 10-разрядными сообщениями, каждый бит которых (нулевой или единичный) сопровождается соответствующим СИ. Перед началом сообщения выдается импульс СТАРТ, а по окончанию сообщения - импульс СТОП, и пусть, например, первое сообщение представляет собой код 10101010 (10) (фиг.2, эпюры «СИ», «инф.1», «инф.2», «СТАРТ», «СТОП»).

Пусть также в качестве блоков 1 и 2 повышения достоверности используют схемы сверток по модулю три, обнаруживающие 100% одноразрядных искажений информации и формирующие при этом на выходах блоков 1 и 2 потенциальный сигнал отбраковки. В качестве первого 3 и второго 4 накопителей пусть используют сдвиговые регистры (CP), удобные для приема информации последовательным кодом, а для использования далее параллельным.

Тогда при синхронном приеме в CP 3 и CP 4 первого сообщения с помощью СИ 39, подаваемых на входы сдвига этих CP (на фиг.1 не показаны), эти два принимаемых двоичных кода побитно сравниваются между собой с помощью сумматора 9 по модулю два и элемента 27 И, опрашиваемого теми же СИ 39, но задержанными на их длину (по

заднему фронту СИ), причем с разрешения триггера (Тг) 18 только в окне приема информации между сигналами СТАРТ 40 и СТОП 41 (фиг.2, эпюра «Тг окна контр.»).

Следует заметить, что перед началом работы при подаче на устройство напряжения на шины питания (ШП) 42 и 43 с помощью формирователя одиночного импульса (ФОИ) 38 формируется импульс, устанавливающий в ноль все элементы памяти 18, …, 26. Если при приеме первого сообщения все его биты будут приняты без искажений (обнаруживаются все искажения любой кратности), то на выходе элемента 27 И будет неизменно логический ноль и Тг 19 останется в нулевом исходном состоянии (фиг.2 эпюра «Тг сбоя»).

По завершении приема первого сообщения по сигналу СТОП 41 происходит опрос блоков 1 и 2 повышения достоверности, в данном случае - сверток по модулю три (сворачивают байт полезной информации), а затем сравнение полученной свертки с контрольным кодом - 10. При равенстве свертки и контрольного кода в каждом блоке 1 и 2 независимо формируется свой сигнал отбраковки, равный нулевому потенциалу (фиг.2, эпюры «Вых. отбр. бл.1» и «Вых. отбр. бл.2»).

В этой ситуации отсутствия обнаружения искажения первого сообщения логические элементы 7, 8, 11 и 12 открывают блок 6 ключей (на выходе элемента 8 ИЛИ-НЕ сформирован уровень логической единицы) и закрывают блок 7 ключей (на выходе элемента 7 ИЛИ-НЕ сформирован уровень логического нуля). Тем самым к моменту поступления на вход считывания блока 10 считывания информации соответствующего сигнала считывания - импульса СТОП (фиг.2, эпюра «Считывание информации») - кондиционная информация первого сообщения через блок 6 ключей поступает на соответствующую группу входов блока 10 выдачи информации и считывается по заднему фронту импульса СТОП через выход блока 10 на информационный выход 15 устройства. Естественно, при этом на выход 16 переспроса соответствующий сигнал не поступает, так как на соответствующем входе элемента 29 И к моменту его опроса (также по импульсу СТОП 41) имеется нулевой потенциал с выхода элемента ИЛИ 12. Никакие неисправности на светодиодах 35, 36 и 37 не индицируются.

Близкая к рассмотренной ситуации логика работы устройства имеет место, когда блоки 1 и 2 (в данном примере сумматоры по модулю три и схемы сравнения с контрольными кодами) работают таким образом, что один блок обнаруживает искажение информации, а другой - нет. Если сигнал отбраковки (логическая единица) формируется на выходе блока 1, то открывается блок 6 ключей для кондиционной информации и закрывается блок 5 ключей для искаженной информации. Если сигнал отбраковки формируется на выходе блока 2, то открывается блок 5 ключей для кондиционной информации и закрывается блок 6 ключей для искаженной информации. При этом, как и в рассмотренной выше ситуации абсолютной исправности, сигнал 16 переспроса не формируется и прием информации осуществляется сколь угодно долго по исправному каналу. Кроме того, блок 17 статистического контроля анализирует, имел ли место случайный сбой или присутствует устойчивая неисправность.

Каждый факт выработки сигнала отбраковки учитывается на соответствующем счетчике 25 для блока 1 и счетчике 26 для блока 2, которые периодически по сигналу переполнения счетчика 23 приема сообщений сбрасываются в ноль, блокируя установку в единицу соответствующих Тг 21 и Тг 22 неисправности каналов 1 и 2. В зависимости от выбранного критерия, но в любом случае разрядность счетчиков 25 и 26 должна быть меньше разрядности счетчика 23, при переполнении счетчика 25 (или 26) срабатывает триггер 21 (или 22), индицируя на светодиоде 36 (или 37) неисправность канала 1 (или канала 2) для обслуживающего персонала для принятия соответствующих мер (ремонт и т.п.).

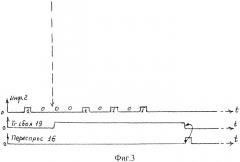

В описанных выше ситуациях совершенно естественно блокируется работа сумматора 9 по модулю два, так как искажения только в одном из каналов обязательно приведут к срабатыванию сумматора 9 по модулю два. Работу сумматора 9 по модулю два необходимо блокировать также в ситуации, когда одновременно оба блока 1, 2 обнаруживают искажение информации (при этом наиболее вероятны алгоритмические ошибки, сформированные на передающем пункте типа несоответствия контрольных кодов полезной информации и т.п.), и осуществлять переспрос информации. Это блокирование осуществляется с помощью элементов НЕ 33 и 34 и элемента И 28 во всех ситуациях кроме одной, когда (Возможна такая кратная неисправность, которая не обнаруживается логикой суммирования по модулю три.) сигналы отбраковки блоков 1 и 2 отсутствуют. При этом элементы НЕ 33 и 34 открывают элемент И 28 и если при этом сумматор 9 по модулю два обнаружит несовпадение информации между каналами хотя бы в одном бите, то сработает Тг 19, который через элементы 28, 12, 7 и 8 закроет оба блока 5 и 6 ключей, блокируя выдачу информации, и обеспечит прохождение через элемент 29 сигнала 16 переспрос. На фиг.3 показана ситуация, когда при тех же исходных условиях (те же эпюры фиг.2: «СТАРТ», «СИ», «СТОП», «инф.1», «Тг окна контр.», которые мысленно относятся к фиг.3) возникает сбой в третьем бите инф.2: вместо логической единицы принят логический ноль (фиг.3, эпюра «инф.2»). Тогда по соответствующему СИ установится в единицу Тг сбоя 19, а затем по заданному фронту сигнала СТОП 41 с разрешения элементов 33, 34, 28, 12 и 29 будет выработан сигнал 16 переспроса.

При любой устойчивой неисправности устройства (или сигналов 13 и 14 связи или передающего пункта), приводящей к формированию сигнала 16 переспроса, процессы в устройстве повторятся вновь и произойдет зацикливание, если не предусмотреть обнаружение и прерывание этого.

Для этого на вход +1 счетчика 24 переспроса подаются с выхода элемента И 29 одноименные сигналы, которые суммируются до переполнения указанного счетчика 24. Если переспрос был вызван случайным сбоем, то в зависимости от выбранного критерия (разрядностей счетчика 23 приема сообщений и счетчика 24 переспроса) после переполнения счетчика 23 произойдет сброс счетчика 24 и работа продолжится. По сигналу переполнения счетчика 24 Тг 20 неисправности устройства устанавливается в состояние логической единицы и блокирует на элементе И 29 формирование очередных сигналов 16 переспроса. При этом зажигается соответствующий светодиод 35, сигнализирующий обслуживающему персоналу о необходимости срочного ремонта в связи с невозможностью дальнейшей работы.

Устройство синхронного приема двоичной информации по дублирующим каналам связи, содержащее первый и второй блоки повышения достоверности, первый и второй накопители информации, первый и второй блоки ключей, первый и второй элементы ИЛИ-НЕ, сумматор по модулю два, блок выдачи информации, первые элементы И и ИЛИ, а также первый и второй информационные входы, информационный выход и выход переспроса, при этом первый и второй информационные входы, представляющие собой информационные входы приема двоичной информации последовательным кодом первого и второго каналов, соединены соответственно с информационными входами первого и второго накопителя и параллельно с соответствующими входами сумматора по модулю два, группа выходов первого накопителя поразрядно соединена с группой входов первого блока повышения достоверности и с группой входов первого блока ключей, группа выходов которого поразрядно соединена с первой группой входов блока выдачи информации, группа выходов которого является информационным выходом устройства, группа выходов второго накопителя поразрядно соединена с группой входов второго блока повышения достоверности и с группой входов второго блока ключей, группа выходов которого поразрядно соединена со второй группой входов блока выдачи информации, выход сигнала отбраковки первого блока повышения достоверности соединен с первыми входами первых элементов И и ИЛИ-НЕ, а выход сигнала отбраковки второго блока повышения достоверности соединен со вторым входом первого элемента И и первым входом второго элемента ИЛИ-НЕ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторыми входами первого и второго элементов ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен с входом управления первого блока ключей, выход второго элемента ИЛИ-НЕ соединен с входом управления второго блока ключей и третьим входом первого элемента ИЛИ-НЕ, отличающееся тем, что устройство дополнительно содержит блок статистического контроля в составе триггеров окна контроля, сбоя по модулю два, неисправности устройства, неисправности первого канала и неисправности второго канала, счетчиков приема сообщений, переспроса, отбраковки первого и второго каналов, второго, третьего и четвертого элементов И, второго, третьего и четвертого элементов ИЛИ, первого и второго элементов НЕ, светодиодов неисправности устройства, первого и второго каналов, формирователя одиночного импульса, входов импульсов синхронизации, старт, стоп и плюсовой вход и минусовой вход шины питания, при этом вход импульсов синхронизации соединен с первым входом второго элемента И, второй и третий входы которого соединены соответственно с выходом сумматора по модулю 2 и прямым выходом триггера окна контроля, а выход которого соединен с входом установки в единицу триггера сбоя по модулю два, прямой выход которого соединен с первым входом третьего элемента И, второй и третий входы которого соединены через первый и второй элементы НЕ соответственно с выходами сигнала отбраковки первого и второго блоков повышения достоверности, а выход которого соединен со вторым входом первого элемента ИЛИ, вход старт соединен с входом установки в единицу триггера окна контроля, вход установки в ноль которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с входами стоп, +1 счетчика приема сообщений, опроса первого и второго блоков повышения достоверности, считывания блока выдачи информации и первым входом четвертого элемента И, второй и третий входы которого соединены соответственно с выходом первого элемента ИЛИ и инверсным выходом триггера неисправности, а выход которого соединен с первым входом третьего элемента ИЛИ, входом +1 счетчика переспроса и выходом переспроса устройства, входы +1 счетчика отбраковки первого канала и счетчика отбраковки второго канала соединены соответственно с выходами сигнала отбраковки первого и второго блоков повышения достоверности, выходы переполнения счетчика приема сообщений, счетчика переспроса, счетчика отбраковки первого канала и счетчика отбраковки второго канала соединены соответственно с первым входом четвертого элемента ИЛИ, с входами установки в единицу триггеров неисправности устройства, первого канала и второго канала, прямые выходы триггеров неисправности устройства, первого канала и второго канала соединены через соответствующие светодиоды с минусовым входом шины питания устройства, входы установки в ноль счетчиков переспроса, отбраковки первого канала и второго канала и триггеров первого канала и второго канала соединены с выходом четвертого элемента ИЛИ, второй вход которого соединен с входами установки в ноль триггера неисправности устройства и счетчика приема сообщений, со вторыми входами второго и третьего элементов ИЛИ и выходом формирователя одиночного импульса, вход которого соединен с плюсовым входом шины питания устройства, выход третьего элемента ИЛИ соединен с входом установки в ноль триггера сбоя по модулю два.