Управляемый усилитель и аналоговый смеситель сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах умножения частоты. Достигаемый технический результат: получение на выходе не только амплитудных изменений выходного сигнала под действием управляющего напряжения, но и его фазы, что позволяет подавить основные гармоники. Управляемый усилитель и смеситель аналоговых сигналов содержит первый (1) и второй (2) источники противофазных входных напряжений, первый (3) входной транзистор, эмиттер которого через первый (4) токостабилизирующий двухполюсник связан с первым (5) источником питания, второй (6) входной транзистор, эмиттер которого через второй (7) токостабилизирующий двухполюсник связан с первым (5) источником питания, третий (8) входной транзистор, эмиттер которого связан с эмиттером четвертого (9) входного транзистора и через третий (10) токостабилизирующий двухполюсник соединен с первым (5) источником питания, дифференциальную цепь нагрузки, согласованную со вторым источником питания. 3 з.п. ф-лы, 21 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого со входов канала «X» зависит от уровня сигнала управления канала «Y». Управляемый усилитель и аналоговый смеситель сигналов (УУ) являются базовыми узлами современных систем приема и обработки сигналов ВЧ и СВЧ диапазонов.

В современной микроэлектронике широкое применение получили дифференциальные каскады (ДК) на составных транзисторах [1-13]. Их коэффициент усиления по напряжению зависит от величины статического тока общей эмиттерной цепи ДК (Iy=I0) и, следовательно, такие ДК являются (при электронном изменении величины тока Iy=I0) управляемыми усилителями (УУ).

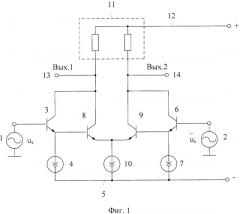

Ближайшим прототипом заявляемого устройства, архитектура которого присутствует также и в других патентах и монографиях [1-13], является управляемый усилитель на основе так называемого каскада Дарлингтона, фиг.1, представленный в книге Аналоговые интегральные схемы. Элементы, схемы, системы и применения / Под ред. Дж. Коннели. - М.: Мир, 1977, стр.75, рис.3.7», содержащий первый 1 и второй 2 источники противофазных входных напряжений, первый 3 входной транзистор, эмиттер которого через первый 4 токостабилизирующий двухполюсник связан с первым 5 источником питания, второй 6 входной транзистор, эмиттер которого через второй 7 токостабилизирующий двухполюсник связан с первым 5 источником питания, третий 8 входной транзистор, эмиттер которого связан с эмиттером четвертого 9 входного транзистора и через третий 10 токостабилизирующий двухполюсник соединен с первым 5 источником питания, дифференциальную цепь нагрузки 11, согласованную со вторым 12 источником питания и связанную с первым 13 и вторым 14 выходами устройства, причем эмиттер первого 3 входного транзистора соединен с базой третьего 8 входного транзистора, эмиттер второго 6 входного транзистора соединен с базой четвертого 9 входного транзистора, коллектор третьего 8 входного транзистора соединен по переменному току с коллектором первого 3 входного транзистора и связан с первым 13 выходом устройства, коллектор четвертого 9 входного транзистора соединен по переменного току с коллектором второго 6 входного транзистора и связан со вторым 14 выходом устройства.

Существенный недостаток известного устройства состоит в том, что при электронном управлении величиной коэффициента усиления (Ку) в известном УУ фаза выходного напряжения в рабочем диапазоне частот дифференциального каскада (ДК) не изменяется на 180°. Как следствие, это не позволяет использовать известный ДК в структуре ряда устройств радиотехники, например, в качестве смесителя аналоговых сигналов, фазовых детекторов и т.п.

Основная задача предлагаемого изобретения состоит в получении на выходе ДК не только амплитудных изменений выходного сигнала под действием управляющего напряжения канала «Y», но и его фазы. Как следствие, это позволяет создавать на основе предлагаемого устройства смесители аналоговых сигналов с хорошим подавлением основной гармоники.

Поставленная задача решается тем, что в УУ фиг.1, содержащем первый 1 и второй 2 источники противофазных входных напряжений, первый 3 входной транзистор, эмиттер которого через первый 4 токостабилизирующий двухполюсник связан с первым 5 источником питания, второй 6 входной транзистор, эмиттер которого через второй 7 токостабилизирующий двухполюсник связан с первым 5 источником питания, третий 8 входной транзистор, эмиттер которого связан с эмиттером четвертого 9 входного транзистора и через третий 10 токостабилизирующий двухполюсник соединен с первым 5 источником питания, дифференциальную цепь нагрузки 11, согласованную со вторым 12 источником питания и связанную с первым 13 и вторым 14 выходами устройства, причем эмиттер первого 3 входного транзистора соединен с базой третьего 8 входного транзистора, эмиттер второго 6 входного транзистора соединен с базой четвертого 9 входного транзистора, коллектор третьего 8 входного транзистора соединен по переменному току с коллектором первого 3 входного транзистора и связан с первым 13 выходом устройства, коллектор четвертого 9 входного транзистора соединен по переменного току с коллектором второго 6 входного транзистора и связан со вторым 14 выходом устройства, предусмотрены новые элементы и связи - базы первого 3 и второго 6 входных транзисторов связаны по переменному току с общей шиной 15 первого 5 и второго 12 источников питания, первый 1 источник входного напряжения подключен по переменному току к эмиттеру первого 3 входного транзистора, второй 2 источник входного напряжения подключен по переменному току к эмиттеру второго 6 входного транзистора, а объединенные эмиттеры третьего 8 и четвертого 9 входных транзисторов связаны по переменному току с источником управляющего напряжения 16.

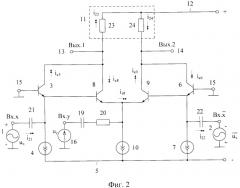

На фиг.1 показана схема УУ-прототипа, а на фиг.2 - схема заявляемого УУ в соответствии с п.1 и п.2 формулы изобретения.

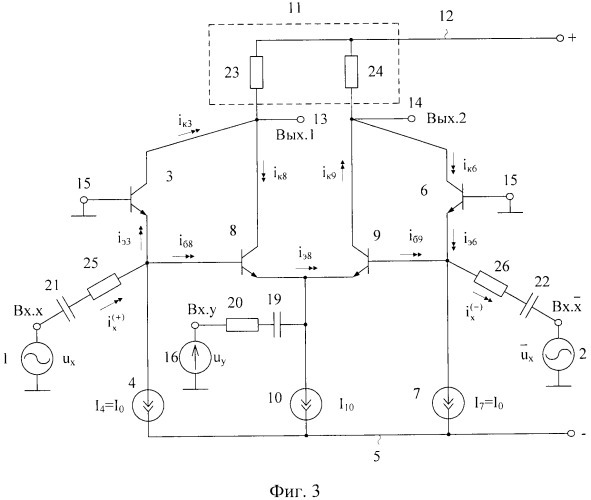

На фиг.3 показана схема заявляемого УУ в соответствии с п.3 формулы изобретения.

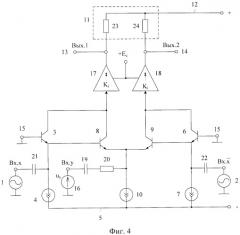

На фиг.4 показана схема заявляемого УУ в соответствии с п.4 формулы изобретения.

На фиг.5 показана схема фиг.4 с конкретным выполнением первого 17 и второго 18 дополнительных усилителей тока.

На фиг.6 представлена схема заявляемого УУ фиг.2 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 показана зависимость коэффициента усиления по напряжению от величины тока третьего 10 токостабилизирующего двухполюсника схемы фиг.6 при U x = U ¯ x = 1 м В , I2=I10=Ivar=2.045 мA.

Данный график необходим для правильной настройки управляемого усилителя, работающего в режиме смесителя сигналов.

На фиг.8 приведен спектр выходных сигналов при управляющем напряжении источника 16 (канал «Y») с частотой fy=100 кГц и амплитудой Uy=465 мB схемы фиг.6, а также напряжениях первого 1 и второго 2 источников противофазных напряжений Ux=1 мB, U ¯ x = 1 м В , fx=10 МГц.

На фиг.9 показана осциллограмма выходного напряжения схемы фиг.6 при fy=100 кГц, Uy=465 мB, а также Ux=1 мВ, U ¯ x = 1 м В , fx=10 МГц.

На фиг.10 представлена схема заявляемого УУ фиг.2 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.11 показана зависимость коэффициента усиления по напряжению схемы фиг.10 от тока третьего 10 токостабилизирующего двухполюсника при напряжениях источников сигналов 1 и 2 (канал «X») U x = U ¯ x = 1 м В .

На фиг.12 представлен спектр выходного напряжения схемы фиг.10 при fy=100 кГц, Uy=463.5 мB, а также U x = U ¯ x = 1 м В , fx=10 МГц. При этом подавление центральной гармоники с частотой 10 МГц - более 20 раз.

На фиг.13 приведена осциллограмма выходного напряжения схемы фиг.10 при fу=100 кГц, Uy=463.5 мB, а также U x = U ¯ x = 1 м В , fx=10 МГц.

На фиг.14 представлена схема заявляемого УУ фиг.5 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда последовательно с входными разделительными конденсаторами включены согласующие резисторы R7=R5=250 Ом.

На фиг.15 показана зависимость модуля коэффициента усиления по напряжению схемы фиг.14 при напряжении U x = U ¯ x = 1 м В . При этом фаза выходного напряжения УУ в точке излома характеристики Ky=φ(I10) меняется на 180°.

На фиг.16 приведен спектр выходного сигнала схемы фиг.14, при fx=100 кГц, Uy=1 мВ, fy=10 МГц. При этом подавление центральной гармоники - более чем в 20 раз.

На фиг.17 показана осциллограмма выходного напряжения схемы фиг.14 при U x = U ¯ x = 415 м В , fx=100 кГц, а также Uy=1 мB, fy=10 МГц.

На фиг.18 представлена схема заявляемого УУ фиг.5 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» для случая, когда источники противофазных входных напряжений 1 и 2 подключены к эмиттерам входных транзисторов 3 и 6 УУ.

На фиг.19 представлена зависимость модуля коэффициента усиления УУ фиг.18 при Uy=1 мВ от напряжения источника управляющего напряжения 16 (uy). При токах I0=Ivar>2 мА и токах I10=Ivar<2 мА фаза выходного сигнала изменяется на 180°.

На фиг.20 представлен спектр выходного сигнала схемы фиг.18 при fx=100 кГц, Uy=1 мB, fy=10 МГц, из которого следует, что УУ обеспечивает подавление центральной гармоники более чем в 20 раз.

На фиг.21 приведена осциллограмма выходного напряжения схемы фиг.18 при U x = U ¯ x = 415 м В , fx=100 кГц, Uy=1 мB, fy=10 МГц.

Заявляемый управляемый усилитель фиг.2, который может функционировать как смеситель аналоговых сигналов, содержит первый 1 ux и второй 2 u ¯ x источники противофазных входных напряжений, передача которых на выход устройства образует канал «X», первый 3 входной транзистор, эмиттер которого через первый 4 токостабилизирующий двухполюсник связан с первым 5 источником питания, второй 6 входной транзистор, эмиттер которого через второй 7 токостабилизирующий двухполюсник связан с первым 5 источником питания, третий 8 входной транзистор, эмиттер которого связан с эмиттером четвертого 9 входного транзистора и через третий 10 токостабилизирующий двухполюсник соединен с первым 5 источником питания, дифференциальную цепь нагрузки 11, согласованную со вторым 12 источником питания и связанную с первым 13 и вторым 14 выходами устройства, причем эмиттер первого 3 входного транзистора соединен с базой третьего 8 входного транзистора, эмиттер второго 6 входного транзистора соединен с базой четвертого 9 входного транзистора, коллектор третьего 8 входного транзистора соединен по переменному току с коллектором первого 3 входного транзистора и связан с первым 13 выходом устройства, коллектор четвертого 9 входного транзистора соединен по переменного току с коллектором второго 6 входного транзистора и связан со вторым 14 выходом устройства. Базы первого 3 и второго 6 входных транзисторов связаны по переменному току с общей шиной 15 первого 5 и второго 12 источников питания, первый 1 источник входного напряжения подключен по переменному току к эмиттеру первого 3 входного транзистора, второй 2 источник входного напряжения подключен по переменному току к эмиттеру второго 6 входного транзистора, а объединенные эмиттеры третьего 8 и четвертого 9 входных транзисторов связаны по переменному току с источником управляющего напряжения 16.

Кроме того, на фиг.2 в соответствии с п.2 формулы изобретения между источником управляющего напряжения 16 (Uy), передачу от которого будем называть каналом «Y», и объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов включены последовательно соединенные первый 19 вспомогательный конденсатор и первый 20 вспомогательный резистор.

В схеме фиг.2 первый 1 и второй 2 источники входного напряжения подключены к эмиттерам первого 3 и второго 6 входных транзисторов через соответствующие разделительные конденсаторы 21 и 22. Дифференциальная цепь нагрузки 11 в схеме фиг.2 реализована на резисторах 23 и 24.

На фиг.3 в соответствии с п.3 формулы изобретения первый 1 источник входного напряжения подключен по переменному току к эмиттеру первого 3 входного транзистора через последовательно соединенные первый 21 разделительный конденсатор и первый 25 дополнительный резистор, а второй 2 источник входного напряжения подключен по переменному току к эмиттеру второго 6 входного транзистора через последовательно соединенные второй 22 разделительный конденсатор и второй 26 дополнительный резистор.

На фиг.4 в соответствии с п.4 формулы изобретения коллектор третьего 8 входного транзистора связан с первым 13 выходом устройства через первый 17 дополнительный усилитель тока, а коллектор четвертого 9 входного транзистора связан с вторым 14 выходом устройства через второй 18 дополнительный усилитель тока.

На фиг.5 первый 17 и второй 18 дополнительные усилители тока реализованы на транзисторах 27 и 28, включенных по схеме с общей базой. Потенциал объединенных баз транзисторов 27 и 28 устанавливается источником напряжения 29 (в частном случае - общей шиной источников питания). Для передачи приращений коллекторных токов транзисторов 3 и 6 в эмиттерные цепи транзисторов 27 и 28 используются резисторы 30 и 31, а также конденсаторы 32 и 33.

Рассмотрим работу УУ фиг.2 в диапазоне частот, когда влиянием конденсаторов 19, 21, 22 можно пренебречь из-за их малого сопротивления на переменном токе.

Входной сигнал (их) канала «X» передается от источников напряжений 1 и 2 в цепь нагрузки 11 на выходы 13 и 14 по двум каналам. Первый канал, образуемый каскадами с общей базой на транзисторах 3 и 6, не инвертирует фазы сигналов ux и u ¯ x (1 и 2)к соответствующим выходам 13 и 14. При этом крутизна преобразования ux и u ¯ x в коллекторные токи транзисторов 3 и 6

i к 3 = u x r э 3 = u x ϕ т I 4 , ( 1 )

i к 6 = u ¯ x r э 6 = u ¯ x ϕ т I 7 , ( 2 )

где rэ3, rэ6 - сопротивления эмиттерных переходов соответствующих транзисторов 3 и 6;

φт=25 мВ - температурный потенциал,

I4, I7 - статические токи двухполюсников 4, 7.

Второй канал передачи сигналов канала «X» к выходу 13 (14) - инвертирующий. Он связан поступлением напряжений ux (1) и u ¯ x (2) на базы транзисторов 8 и 9 и их преобразованием в коллекторные токи транзисторов 8 и 9. Коэффициенты преобразования напряжений ux и u ¯ x в выходные токи этого канала зависят от уровня тока в общей эмиттерной цепи транзисторов 8 и 9, т.е. тока третьего 10 токостабилизирующего двухполюсника I10:

i к 8 ≈ u x + u ¯ x r э 8 + r э 9 , ( 3 )

i к 9 ≈ u x + u ¯ x r э 8 + r э 9 , ( 4 )

Как следствие, суммарный ток в резисторе 23 (24) дифференциальной цепи нагрузки имеет разностные составляющие:

i 23 = u x r э 3 − u x + u ¯ x r э 8 + r э 9 , ( 5 )

где rэ3, rэ8, rэ9 - сопротивления эмиттерных переходов соответствующих транзисторов 3, 8 и 9:

r э 3 = ϕ т I 4 , r э 6 = ϕ т I 7 , ( 6 )

r э 8 = r э 9 = 1 2 ϕ т I 10 ,

где I4=I7=const, I10 - статические токи двухполюсников 4, 7, 10, причем суммарный ток общей эмиттерной цепи транзисторов 8 и 9

i 10 ( t ) = I 10 + u y R 20 . ( 7 )

Таким образом, в резисторе нагрузки 23 (24) протекают две противофазные составляющие токов, обусловленные входным сигналом канала «X». Нулевое значение суммарный ток через резистор R23 (R24) принимает при

I 10 0 ≈ 2 I 4 = c o n s t ( 8 )

Если суммарный ток общей эмиттерной цепи транзисторов 8 и 9 под действием источника управляющего напряжения 16 (Uy) становится меньше или больше, чем I 10 0 , то происходит изменение фазы выходного сигнала ДК - в схеме преобладает либо первый неинвертирующий канал передачи ux и u ¯ x через транзисторы 3 и 6, либо второй инвертирующий канал (транзисторы 8, 9). Этот эффект достигается за счет новых связей в заявляемом ДК и является необходимым условием для реализации на его основе не только управляемого фазочувствительного (к управляющему сигналу канала «Y») усилителя, но и смесителя сигналов каналов «X» и «Y» с подавлением центральной гармоники ux и u ¯ x . Причем переменная составляющая выходного напряжения УУ фиг.2

U в ы х ≈ u x u y ( R 23 + R 24 ) 2 ϕ т R 20 ( 9 )

Из (1)-(9) следует, что заявляемое устройство обеспечивает смешение (перемножение) двух сигналов ux и uy, что подтверждается результатами моделирования фиг.8 и фиг.9, фиг.12 и фиг.13, фиг.16 и фиг.17, фиг.20 и фиг.21.

В СВЧ смесителях сигналов фиг.3 резисторы 25 и 26 могут выполнять функции цепей согласования источника входного напряжения канала «X» (1, 2) и УУ с заданным волновым сопротивлением, например, 50 Ом.

Замечательная особенность заявляемого устройства - возможность использования в системах СВЧ связи, реализуемых на основе SiGe техпроцессов.

Таким образом, предлагаемое техническое решение является альтернативным решением широко распространенного смесителя Гильберта.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US 2009/058466 fig.3.

2. Патент US №6.137.363.

3. Патент US №3.482.177 fig.3.

4. Патентная заявка US 2005/0225389 fig.3.

5. Патентная заявка US 2009/289714 fig.3.

6. Патент JP 52-139346, кл. 98(5)/А31, 1997.

7. Патент US 4.101.842 fig.1.

8. Патент US5.006.818.

9. Патент СССР 813692.

10. Патент СССР 497713.

11. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с.- стр.56, рис.2-11.

12. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983.- 216 с. - стр.140, рис.4.11.

13. Гальперин М.В. и др. Усилители постоянного тока / Гальперин М.В., Злобин Ю.П., Павленко В.А. - 2-е изд., перераб. и доп. - М.: Энергия, 1978, стр.78, рис.2-14.

1. Управляемый усилитель и смеситель аналоговых сигналов, содержащий первый (1) и второй (2) источники противофазных входных напряжений, первый (3) входной транзистор, эмиттер которого через первый (4) токостабилизирующий двухполюсник связан с первым (5) источником питания, второй (6) входной транзистор, эмиттер которого через второй (7) токостабилизирующий двухполюсник связан с первым (5) источником питания, третий (8) входной транзистор, эмиттер которого связан с эмиттером четвертого (9) входного транзистора и через третий (10) токостабилизирующий двухполюсник соединен с первым (5) источником питания, дифференциальную цепь нагрузки (11), согласованную со вторым (12) источником питания и связанную с первым (13) и вторым (14) выходами устройства, причем эмиттер первого (3) входного транзистора соединен с базой третьего (8) входного транзистора, эмиттер второго (6) входного транзистора соединен с базой четвертого (9) входного транзистора, коллектор третьего (8) входного транзистора соединен по переменному току с коллектором первого (3) входного транзистора и связан с первым (13) выходом устройства, коллектор четвертого (9) входного транзистора соединен по переменному току с коллектором второго (6) входного транзистора и связан со вторым (14) выходом устройства, отличающийся тем, что базы первого (3) и второго (6) входных транзисторов связаны по переменному току с общей шиной (15) первого (5) и второго (12) источников питания, первый (1) источник входного напряжения подключен по переменному току к эмиттеру первого (3) входного транзистора, второй (2) источник входного напряжения подключен по переменному току к эмиттеру второго (6) входного транзистора, а объединенные эмиттеры третьего (8) и четвертого (9) входных транзисторов связаны по переменному току с источником управляющего напряжения (16).

2. Управляемый усилитель и смеситель аналоговых сигналов по п.1, отличающийся тем, что между источником управляющего напряжения (16) и объединенными эмиттерами третьего (8) и четвертого (9) входных транзисторов включены последовательно соединенные первый (19) вспомогательный конденсатор и первый (20) вспомогательный резистор.

3. Управляемый усилитель и смеситель аналоговых сигналов по п.1, отличающийся тем, что первый (1) источник входного напряжения подключен по переменному току к эмиттеру первого (3) входного транзистора через последовательно соединенные первый (21) разделительный конденсатор и первый (25) дополнительный резистор, а второй (2) источник входного напряжения подключен по переменному току к эмиттеру второго (6) входного транзистора через последовательно соединенные второй (22) разделительный конденсатор и второй (26) дополнительный резистор.

4. Управляемый усилитель и смеситель аналоговых сигналов по п.1, отличающийся тем, что коллектор третьего 8 входного транзистора связан с первым (13) выходом устройства через первый (17) дополнительный усилитель тока, а коллектор четвертого (9) входного транзистора связан с вторым (14) выходом устройства через второй (18) дополнительный усилитель тока.