Декодирующее устройство кода хэмминга

Иллюстрации

Показать всеИзобретение относится к кодирующим устройствам помехоустойчивого кода. Технический результат заключается в создании декодирующего устройства кода Хэмминга с упрощенной схемой реализации. Декодирующее устройство кода Хэмминга дополнительно содержит двухвходовой элемент И, счетчик и последовательно-параллельный сдвигающий регистр, выходы которого соединены со вторыми входами двухвходовых сумматоров по модулю 2 соответственно, выходы которых соединены с первыми входами двухвходовых элементов И, выходы которых являются информационными выходами устройства, а вторые входы объединены и соединены с первым выходом счетчика, второй, третий и четвертый выходы которого соединены с первыми входами первого, второго и третьего двухвходовых элементов И-НЕ соответственно, вторые входы которых объединены и соединены с выходом дополнительно введенного двухвходового элемента И, первый вход которого соединен со входом синхронизации сдвигающего регистра, входом синхронизации счетчика и является входом синхронизации устройства, а второй вход соединен со входом последовательной записи сдвигающего регистра и информационным входом D устройства. Достигаемым техническим результатом является формирование на выходе декодирующего устройства кода Хэмминга неискаженной кодовой комбинации. 2 ил.

Реферат

Изобретение относится к декодирующим устройствам помехоустойчивого кода, обеспечивающего восстановление передаваемой по каналу связи информации после ее искажений под действием помех

Известно декодирующее устройство кода Хэмминга, исправляющее однократную ошибку и преобразующее последовательный входной код в параллельный выходной код (см. книгу Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973, с. 359, рис. 6.11), содержащее входное устройство, распределитель импульсов с (k+r) выходами, 2k двухвходовых элементов И-НЕ, k триггеров наборного устройства, r многовходовых элементов ИЛИ, r двухвходовых элементов И-НЕ, выходы которых соединены с соответствующими входами r счетных триггеров, дешифратор на r входов, схему исправления ошибок на основе k сумматоров по модулю 2, k двухвходовых элементов И.

Недостатком устройства является сложность схемной реализации, связанная, в основном, с необходимостью использования многовыходного распределителя импульсов и большого количества логических элементов.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Решаемой технической задачей является создание декодирующего устройства кода Хэмминга с упрощенной схемной реализацией.

Достигаемым техническим результатом является формирование на выходе декодирующего устройства кода Хэмминга неискаженной кодовой комбинации.

Для достижения технического результата в декодирующем устройстве кода Хэмминга, содержащем r-двухвходовых элементов И-НЕ, где r - количество проверочных элементов, счетные триггеры, информационные входы которых соединены с соответствующими входами двухвходовых элементов И-НЕ, а входы сброса объединены и соединены с входом сброса устройства, дешифратор, входы которого соединены с выходами счетных триггеров, соответственно, а выходы соединены с первыми входами двухвходовых сумматоров по модулю 2, двухвходовые элементы И, новым является то, что дополнительно введены двухвходовой элемент И, счетчик и последовательно-параллельный сдвигающий регистр, выходы которого соединены со вторыми входами двухвходовых сумматоров по модулю 2, соответственно, выходы которых соединены с первыми входами двухвходовых элементов И, выходы которых являются информационными выходами устройства, а вторые входы объединены и соединены с первым выходом счетчика, второй, третий и четвертый выходы которого соединены с первыми входами первого, второго и третьего двухвходовых элементов И-НЕ, соответственно, вторые входы которых объединены и соединены с выходом дополнительно введенного двухвходового элемента И, первый вход которого соединен со входом синхронизации сдвигающего регистра, входом синхронизации счетчика и является входом синхронизации устройства, а второй вход соединен с входом последовательной записи последовательно-параллельного сдвигающего регистра и информационным входом D устройства.

Новая совокупность существенных признаков позволяет сформировать на выходе декодирующего устройства кода Хэмминга неискаженную кодовую комбинацию, исправить одиночную ошибку и упростить схемную реализацию декодирующего устройства.

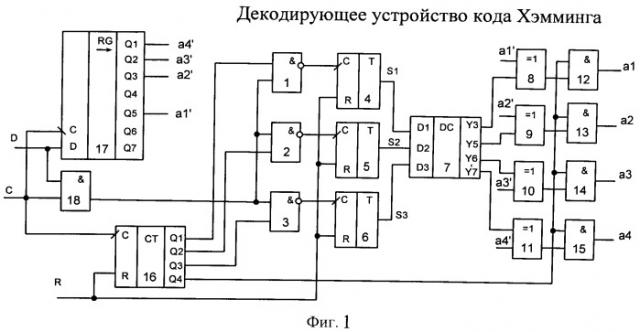

На фиг.1 представлена схема заявляемого декодирующего устройства кода Хэмминга. Устройство содержит r-двухвходовых элементов И-НЕ 1, 2, 3, где r - количество проверочных элементов, счетные триггеры 4, 5, 6, информационные входы которых соединены с соответствующими входами двухвходовых элементов И-НЕ 1, 2, 3, а входы сброса объединены и соединены с входом сброса R устройства, дешифратор 7, входы которого соединены с выходами счетных триггеров 4, 5, 6, соответственно, а выходы соединены с первыми входами двухвходовых сумматоров 8, 9, 10, 11 по модулю 2, двухвходовые элементы И 12, 13, 14, 15, дополнительно введенный двухвходовой элемент И 18, счетчик 16 и последовательно-параллельный сдвигающий регистр 17, выходы которого соединены со вторыми входами двухвходовых сумматоров 8, 9, 10, 11 по модулю 2, выходы которых соединены с первыми входами двухвходовых элементов И 12, 13, 14, 15, выходы которых являются информационными выходами устройства, а вторые входы объединены и соединены с первым выходом счетчика 16, второй, третий и четвертый выходы которого соединены с первыми входами 1, 2 и 3 двухвходовых элементов И-НЕ, вторые входы которых объединены и соединены с выходом двухвходового элемента И 18, первый вход которого соединен со входом синхронизации С сдвигающего регистра 17, входом синхронизации С счетчика 16 и является входом синхронизации С устройства, а второй вход соединен с входом последовательной записи D сдвигающего регистра и информационным входом D устройства.

Декодирующее устройство кода Хэмминга работает следующим образом.

В начальном состоянии в последовательно-параллельном сдвигающем регистре 17 информация отсутствует, счетчик 16 и триггеры 4, 5, 6, 7 удерживаются в исходном состоянии логического "0" сигналом сброса по R-входу устройства.

По переднему фронту первого импульса синхронизации, поступающему на вход С устройства, изменяется состояние счетчика 16, на его выходе Q1 устанавливается сигнал логической «1», который поступает на первый вход элемента И-НЕ 1. На вторые входы элементов И-НЕ 1, 2, 3 по импульсу синхронизации поступает первый символ кодовой посылки кода Хэмминга через элемент И 18.

По срезу первого импульса синхронизации первый символ поступает также на вход D последовательно-параллельного сдвигающего регистра 17.

Если первый символ кодовой последовательности является логическим «0», на выходе элемента И-НЕ 1 устанавливается логическая «1», которая поступает на счетный вход триггера 4, на выходе которого устанавливается сигнал логической «1». В противном случае на выходе триггера будет присутствовать сигнал логического «0».

По переднему фронту второго импульса синхронизации изменяется состояние счетчика 16, на выходе Q1 которого устанавливается сигнал логической «0», а на выходе Q2 устанавливается сигнал логической «1», который поступает на первый вход элемента И-НЕ 2. На вторые входы элементов И-НЕ 1, 2, 3 по второму импульсу синхронизации поступает второй символ кодовой посылки кода Хэмминга через элемент И 18.

По срезу второго импульса синхронизации второй символ кодовой последовательности поступает также на вход последовательно-параллельного сдвигающего регистра 17.

Если второй символ кодовой последовательности является логическим «0», на выходе логического элемента «И-НЕ» 2 устанавливается логическая «1», которая поступает на счетный вход триггера 5, на выходе которого устанавливает сигнал логической «1». В противном случае на выходе триггера 5 будет присутствовать сигнал логического «0». Таким образом, счетчик 16 своими выходами Q1, Q2, Q3 определяет прохождение сигналов кодовой посылки в следующем порядке: на вход логического элемента И-НЕ 4 поступают все нечетные символы кодовой последовательности, на вход логического элемента И-НЕ 2 поступают второй, третий, шестой и седьмой символы кодовой последовательности, на вход логического элемента И-НЕ 3 поступают четвертый, пятый, шестой и седьмой символы кодовой последовательности, которые далее поступают на счетные триггеры 4, 5, 6 соответственно, на выходах которых формируются векторы ошибки: S1=b1 ⊕ a1⊕ a2 ⊕a4; S2=b2 ⊕ a1 ⊕ a3 ⊕ a4; S3=b3 ⊕ a2 ⊕ a3 ⊕ a4. При отсутствии ошибок в символах a1', a2', a3', a4' кодовой последовательности S1=S2=S3 и равны логическому «0».

При ошибке в символе a1' кодовой последовательности S1=S2 и равны логической «1». При ошибке в символе a2' кодовой последовательности S1=S3 и равны логической «1» и т.д.

Таким образом, на первые входы сумматоров по модулю 2 8, 9, 10, 11 поступает результат преобразования векторов ошибок S1, S2, S3 с выходов дешифратора 7, а на вторые входы поступают входные информационные элементы a1', a2', a3', a4' кодовой посылки с выхода последовательно-параллельного сдвигающего регистра 17.

По переднему фронту восьмого синхроимпульса результат сложения по модулю 2 информационных элементов a1', a2', a3', a4' и результатов преобразования векторов ошибок S1, S2, S3 поступает на выходы устройства (по сигналу с выхода Q4 счетчика 16 через элементы И 12, 13, 14, 15).

Сигналом сброса по входу R декодирующее устройство кода Хэмминга приводится в исходное состояние.

На фиг.2 показаны временные диаграммы сигналов декодирующего устройства кода Хэмминга.

Изготовлен макетный образец заявляемого декодирующего устройства кода Хэмминга, испытания которого подтвердили его реализуемость, практическую ценность и эффективность.

Декодирующее устройство кода Хэмминга, содержащее r-двухвходовых элементов И-НЕ, где r - количество проверочных элементов, счетные триггеры, информационные входы которых соединены с соответствующими входами двухвходовых элементов И-НЕ, а входы сброса объединены и соединены с входом сброса устройства, дешифратор, входы которого соединены с выходами счетных триггеров, соответственно, а выходы соединены с первыми входами двухвходовых сумматоров по модулю 2, двухвходовые элементы И, отличающееся тем, что дополнительно введены двухвходовой элемент И, счетчик и последовательно-параллельный сдвигающий регистр, выходы которого соединены со вторыми входами двухвходовых сумматоров по модулю 2, соответственно, выходы которых соединены с первыми входами двухвходовых элементов И, выходы которых являются информационными выходами устройства, а вторые входы объединены и соединены с первым выходом счетчика, второй, третий и четвертый выходы которого соединены с первыми входами первого, второго и третьего двухвходовых элементов И-НЕ, соответственно, вторые входы которых объединены и соединены с выходом дополнительно введенного двухвходового элемента И, первый вход которого соединен со входом синхронизации сдвигающего регистра, входом синхронизации счетчика и является входом синхронизации устройства, а второй вход соединен с входом последовательной записи последовательно-параллельного сдвигающего регистра и информационным входом D устройства.