Устройство задержки электрических сигналов

Иллюстрации

Показать всеРеферат

! f

Всеоо ю е .;.я патентно-т.,"..::. >-, идя

I о п и-с"- х-й-тиE

ИЗОБРЕТЕН ИЯ

253I30

Союз Соеетоких

Социалистических

Ресоублил

Зависимое от авт. свидетельства №вЂ”

Зая вле но 27.l V.1967 (№ 1151429/26-9) .с присоединением заявки №вЂ”

Приоритет—

О публиковало 30.1Х.1969. Бюллетень ¹ 30

Дата опубликования описания

Кл. 21а, 36/04

Комитет оо делам иаобретеиий и открытий ори Совете Мииистрое

СССР

МПК Н 03

УДК 621.374,5(088.8) Авторы изобретения

Ю, М. Титов и E. П. Попечителев

Заявитель

Ленинградский электротехнический институт им. В. И. Ульянова (Ленина) УСТРОЙСТВО ЗАДЕРЖКИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ

Известны устройства задержки электрических сигналов, содержащие ключевой транзистор, резистивно-емкостную цепь и пороговое устройство.

Цель изобретения — повысить стабильность временной задержки и расширить диапазон ее плавного регулирования.

Достигается это тем, что в предложенном устройстве к ключевому транзистору подключено пороговое устройство, выполненное по схеме усилителя ограничителя, соединенное с накопительным конденсатором.

Кроме того, пороговое устройство может быть выполнено по схеме двухкаскадного усилителя-ограничителя с общим эмиттерным резистором, причем между эмиттером транзисторов и потенциальной шиной включен стабилитрон.

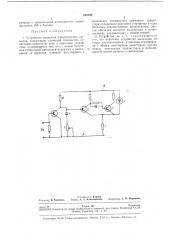

На чертеже изо бражена схема устройства.

К коллектору ключевого транзистора 1 подключено пороговое устройство, выполненное по схеме двухкаскадного усилителя-ограничителя на транзисторах 2 и 8, и одна обкладка накопительного конденсатора 4, вторая обкладка которого через потенциометр 5 соединена с общей шиной б. В эмиттерной цепи транзисторов 2.и 8 включен резистор 7, а между эмиттерами этих транзисторов и потенциальной шиной 8 включен стабилитрон 9.

В нормальном положении транзистор 1 за.перт, и конденсатор 4 заряжается через потенциометр 5 и резистор 10 от источника Ек до напряжения, равного по величине напряжению на резисторе 7. Пилообразное напряжение с конденсатора 4 подается на базу транзистора 2 порогового устройства, вырабатывающего выходные импульсы прямоугольной формы и отрицательной полярности, передний фронт которых задержан относиlo тельно синхроимпульса на время, определяемое параметрами зарядной цепи, положением движка потенциометра 5 и величиной напряжения на резисторе 7. Когда напряжение на конденсаторе 4 превысит па дение напряжения

15 на резисторе 7, транзистор 2 открывается и переходит в режим насыщения, а транзистор 8 закрывается. В таком состоянии схема может находиться сколь угодно долго.

Стабилитрон 9 служит для поддержания на

2р резисторе 7 стабилизированного напряжения.

Когда на вход схемы поступит отрицательный синхроимпульс достаточной амплитуды, транзистор 1 насыщается и конденсатор 4 быстро разряжается через промежуток кол2G лектор-эмиттер транзистора 1 и потенциометр

5. При этом транзистор 2 запирается, а транзистор 8 переходит в режим насыщения. По окончании входного импульса в схеме повторится процесс, описанный выше. Отношение

Зр максимальной длительности выходных им2531 о о может

Составитель Карпов

Редактор В. Кузнецов Техред А. А. Камышникова Корректор Е, Н. Миронов»

Зака". З9 Тираж 48О Подписное

ЦНИИПИ Комитета по делам, изобретений .и открытий при Совете Министров СССР

Москова, Раушокая паб., д. 4, 5.

Типография № 24 Главполиграфпрома, Москва, Г-19, угп Маркса — Энгельса, 14. пульсов к минимальной длительности достигать 200 и больше.

Предмет изобретения о

1. Устройство задержки электрических сигналов, содержащее ключевой транзистор, резистивно-емкостную цепь и пороговое устройство, от гггчающееся тем, что, с целью получения стабильной временной задержки и расши- 19 рения ее пределов плавной регулировки, к

4 коллектору упомянутого ключевого транзистора подключено пороговое устройство и одна обкладка накопительного конденсатора, другая обкладка которого подключена к потенциометру, соединенному с общей шиной.

2. Устройство по п. 1, отличающееся тем, что пороговое устройство выполнено по .схеме двухкаскадного усилителя-ограничителя с общим эмиттерным резистором, причем между эмиттерами транзисторов и потенциальной шиной включен стабилитрон.