Элемент несовпадения

Иллюстрации

Показать всеРеферат

Са!аз Советскик

Сациалистическиу

Республик. :-IIII!Ñ!!МС! С1:!!Г!Х С!!!!ДЕ! ll «1!е!1, Заявлено 24,V1.1968 {№ 1251803/18-24) с присседпнс!!исм заявки X

Приоритет

Опубликовано 30.1Х.1969. Бюллетень ¹ 30

Кл 21а1, 36!18

Комитет по делам изобретений и открытий при Совете ФЛинистрав

СССР

М.ПК Н 03 -<

) Д1х 681 3.053(088.8) Дс!тс! опубликования oIIHoûíllÿ 4Х.1970

А. И. Гусев ! т 1, олеитротехничесиий институт им. В И. Ульянова (Ло!чина) .11Б;1Ъ:,:..:.1.= :й . ! ь

Автор

1 30!.I P E TÑ!! I! Ë

Заявитель

ЭЛЕМЕНТ НЕСОВПАДЕНИЯ

Изобретение относится к элементам автоматики, телемеханики и вычислительной техники.

Оно может найти применение в различных стройствах автоматики и телемеханики, где требуется выполнение логической операции отрицания разнсзначности (или операции равнозначности, которая может быть легко получена простым инвертированием выхода схемы), и, преукде всего, в системах передачи и обработки цифровои инфор»ации, в первую очередь, при построении линейных переключательных схем (лннейных дискретных фильтров), составляющих основу кодирутощих и декодирующих устройств для циклических «одсз.

Извсстные схемы несовпадения на ферротранзисторных ячейках содержат относительно оольшое количество таких ячеек, треоуют два источника питания и тщательного подоора режима работы схемы.

В предлагаемом элементе несовпадения количество ячеек уменьшено, используется только один источник питания — Е,,:, не треоуется выполнения каких-либо особых условии для обеспечения надежной работы схемы; при считывании «1» триоды всех ячеек участву!от в процессе перемагничивания и, следовател!оно, для считывания может оыть использован илинульс минималы!ой мощности.

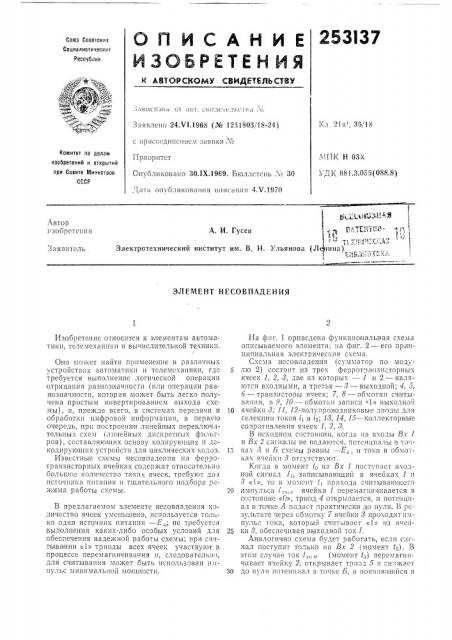

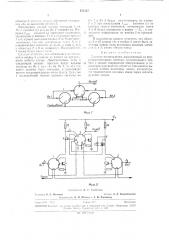

На фнг. 1 приведена функциональная схема описываемого элемента: на фиг. 2 — его пр шципиальная электрическая схема.

Схема несовпадения (сумматор по моду5 лю 2) состоит из трех ферротраензпсторных ячеек 1, 2, 8, две из которых — 1 и 2 — являются входными, а третья — 8 — выходной; 4, 5, б — транзисторы ячеек; 7, 8 — обмотки считывания, а 9, 10 — обмотки записи «1» выходной

10 ячейки 8, 11, 12-полупроводниковые диоды для селекции токов il и i2; 18, 14, 15 — коллекторные сопротивления ячеек 1, 2, 8.

В исходном состояни!1, когда на входы Вх 1 и Вх 2 сигналы не подаются, потснциа Ibl в тс",15 ках Л и В схемы равны — Е,, н токи в обмотках ячейки 8 отсутствуют.

Когда в момент tz на Вх 1 поступает входной сигнал I,, записывающий в ячейках 1 и

8 «1>>, То В В!С>IЕНТ а! Пр1!Хода Са1ИТЫВа1сщЕГО

20 импульса l,„,,„ячейка 1 перемагничивается в состояние «0», триод 4 открывается, и потенциал в точке А падаст практически дс нуля. В результате через обмотку 7 ячейки 8 проходитнмпульс тока, который считывает «)» из ячей25 ки 8, обеспечивая выходной ток I.

Аналогич!нс схема будет работать, если сигнал поступит только на Вх 2 (момент гз). В этом случае ток l,„„(ìoìåíò t.-) перемагш1чивает ячейку 2, открывает триод 5 и cH:IêÿåT

30 до нуля потенциа1 в тОчКЕ Б, а поягив!п1!йся в